Was Sie für die Kanalintegrität spezifizieren sollten: Praktische Checklisten für Hochgeschwindigkeitsverbindungen

Die meisten Teams entdecken Probleme mit der Kanalintegrität erst beim Bring-up: Ein Auge, das in der Simulation sauber aussah, schließt sich auf dem Prüfstand, ein Steckverbinder, der für die Datenrate spezifiziert war, versagt in der tatsächlichen Topologie, oder eine Änderung des Stackups führt zu einem Margenverlust, den niemand eingeplant hatte. Jeder dieser Fälle ist ein Spezifikationsfehler, der sich als Signalintegritätsproblem (SI) zeigt. Die Lösung besteht darin, Kanalintegrität frühzeitig als Satz messbarer Anforderungen zu definieren, sodass sie die Architektur beeinflussen kann, und diese Anforderungen dann in jeder Phase des Designs zu verifizieren.

Zentrale Erkenntnisse

- Kanalintegrität ist in erster Linie ein Anforderungsproblem. Ob Sie Margin gewinnen oder verlieren, entscheidet sich bei Topologie, Stackup und Interconnect-Auswahl.

- Retimer, Redriver, Steckverbinder und Kabel verbrauchen jeweils einen Teil Ihres Kanalbudgets. Spezifizieren Sie sie mit IL-, RL-, Übersprech- und Jitter-Werten, die direkt mit Ihrer Link-Margin verknüpft sind.

- Ein Messplan ist Teil der Kanalspezifikation. Fixture-Strategie und De-Embedding sollten definiert sein, bevor das Layout festgeschrieben wird.

Was Kanalintegrität tatsächlich umfasst

Ein Hochgeschwindigkeitskanal umfasst den gesamten elektrischen Pfad von den Sender-Pins zu den Empfänger-Pins, einschließlich Package-Breakouts, Vias, Referenzebenen-Übergängen, Leiterbahnen, Steckverbindern, Kabeln und jeder aktiven Signalaufbereitung entlang des Weges. Kanalintegrität ist die Fähigkeit dieses Pfads, eine Ziel-Bitfehlerrate (BER) über Spannung, Temperatur, Prozessvariation und reale Interconnect-Bedingungen hinweg einzuhalten. Ihre Topologie, Komponenten und Validierungsmethode müssen alle standhalten, und die Ergebnisse müssen reproduzierbar sein.

Jedes Element im Pfad verbraucht einen Teil des Margin-Budgets. Wenn eines davon unzureichend spezifiziert ist, treten die Probleme spät auf, und der Debug-Zyklus wird teuer. In diesem Artikel stellen wir einen achtstufigen Prozess vor, der Ihnen hilft zu verstehen, was zu spezifizieren ist, wie es zu spezifizieren ist und was Sie von Komponentenlieferanten verlangen sollten, damit Ihre Simulations- und Laborergebnisse zusammenlaufen. Zusätzlich stellen wir praktische Checklisten für jeden Schritt des Prozesses bereit.

Für einen genaueren Blick darauf, wie PCIe 7.0, 800G Ethernet, USB4 und Wi-Fi 7 diese Anforderungen vorgelagert verschärfen, siehe High-Speed Standards Keep Raising the Bar.

Schritt 1. Definieren Sie den Link, den Sie tatsächlich aufbauen

Beginnen Sie mit einem kurzen Block zur Link-Definition, der sowohl in Ihren Anforderungen als auch in Ihrem Testplan enthalten ist.

Checkliste zur Link-Definition

- Standard und Geschwindigkeitsziel (Beispiel: PCIe, Ethernet, USB4 oder ein proprietäres SerDes).

- Anzahl der Lanes und Erwartungen an Lane-Bonding.

- Reichweite und Topologie. Nur auf der Leiterplatte, Board-to-Board, verkabelt oder Flyover.

- Latenzbudget (insbesondere, wenn Sie möglicherweise Retimer hinzufügen).

- Leistungs- und thermische Einschränkungen an wahrscheinlichen Orten der Signalaufbereitung.

- Umgebungs- und mechanische Randbedingungen (Vibration, Servicezugang).

Diese Entscheidungen bilden die Anforderungsbasis für jede nachgelagerte Entscheidung. Legen Sie sie früh fest und behalten Sie sie in Ihrem Testplan bei.

Schritt 2. Erstellen Sie ein Budget, bevor das Layout beginnt

Ein Kanalbudget ist das Rückgrat der Spezifikation. Es verwandelt Wunschdenken in harte Zahlen, die Ihr Stackup, Ihre Steckverbinderwahl und Ihr Signalaufbereitungskonzept tatsächlich erfüllen können.

Budgetposten, die enthalten sein sollten

- Einfügedämpfung (IL) in Abhängigkeit von der Frequenz.

- Rückflussdämpfung (RL) in Abhängigkeit von der Frequenz.

- Übersprechziele: NEXT-, FEXT- und Mixed-Mode-Kennwerte (falls Sie diese verwenden).

- Skew-Budget: einschließlich Beiträgen durch Glasgewebe und Steckverbinder.

- Mode-Conversion-Ziele, da Gleichtaktenergie häufig als EMI sichtbar wird.

- Annahmen zum Jitter-Budget und wie viel Sie erwarten, dass die Entzerrung zurückgewinnt.

Wenn Sie eine Anforderung nicht als Budgetzeile und Referenzebene ausdrücken können, werden Sie sie nicht sauber validieren können.

Schritt 3. Retimer. Was zu spezifizieren ist, wenn Sie CDR benötigen

Wenn Sie Clock and Data Recovery (CDR) benötigen, stellt ein Retimer einen Reset-Punkt im Kanal bereit. Er sendet eine saubere Version des Signals erneut aus und stellt Margin wieder her, die durch Entzerrung allein nicht zurückgewonnen werden kann. Diese Fähigkeit bringt Designrandbedingungen mit sich, die Sie im Voraus spezifizieren müssen.

Checkliste zur Retimer-Spezifikation

- Unterstützte Datenraten und Protokolle.

- Anzahl der Lanes und Flexibilität beim Lane-Mapping.

- Latenz (typisch und Worst-Case).

- Jitter-Toleranz und Jitter-Transferverhalten (wie das Bauteil Jitter filtert oder weitergibt).

- Entzerrungsverhalten und Steuerungsmöglichkeiten: statische Presets versus adaptives Verhalten; wie Sie es konfigurieren und überwachen.

- Leistungszustände und thermische Eigenschaften.

- Anforderungen an den Referenztakt, falls vorhanden.

- Anforderungen an den Signalpfad: Erwartungen an AC-Kopplung, Einschränkungen beim Package-Escape und Routing-Vorgaben.

- Verfügbarkeit von Modellen: IBIS-AMI, wo relevant, plus Referenzdesigns und Evaluierungsunterlagen.

Vorgestellter Retimer

Broadcom BCM85667 ist ein 5-nm-, 16-Lane-PCIe-Gen-6- und CXL-3.1-Retimer mit 64 GT/s PAM4. Sein product brief dokumentiert unterstützte Datenraten, Bifurcation-Optionen, EQ-Steuerungen und Footprint-Kompatibilität. Das ist das Maß an Spezifikationsdetail, das Sie von jedem Retimer erwarten sollten, den Sie qualifizieren.

Schritt 4. Redriver. Was zu spezifizieren ist, wenn Sie lineare EQ möchten

Ein Redriver bietet lineare Entzerrung und Ausgangssignalaufbereitung. Er führt keine Taktrückgewinnung durch. Dieser Kompromiss bedeutet typischerweise geringere Latenz und einfachere Integration, jedoch weniger Fähigkeit, einen stark degradierten Kanal wiederherzustellen.

Checkliste zur Redriver-Spezifikation

- Unterstützte Datenrate und Bandbreite.

- Entzerrungsbereich und Schrittweite.

- Bereich der Ausgangsamplitude und Flat-Gain-Steuerungen.

- Rausch- und Linearitätsverhalten, insbesondere wenn Sie möglicherweise zusammen mit dem Signal auch Rauschen verstärken.

- Eingangsempfindlichkeit und Gleichtaktverhalten.

- Konfigurationsschnittstelle und Telemetrie.

- Package- und Escape-Einschränkungen.

- Verfügbarkeit von Modellen und Hinweise zum Referenzlayout.

Vorgestellter Redriver

Diodes’ PI3EQX32908ZRIEX ist ein 8-Kanal-PCIe-5.0-Linear-Redriver mit Unterstützung für 5 bis 32 Gbit/s sowie programmierbarer kanalweiser EQ-, Ausgangsamplituden- und Flat-Gain-Steuerung; außerdem unterstützt er SAS4- und CXL-Protokolle.

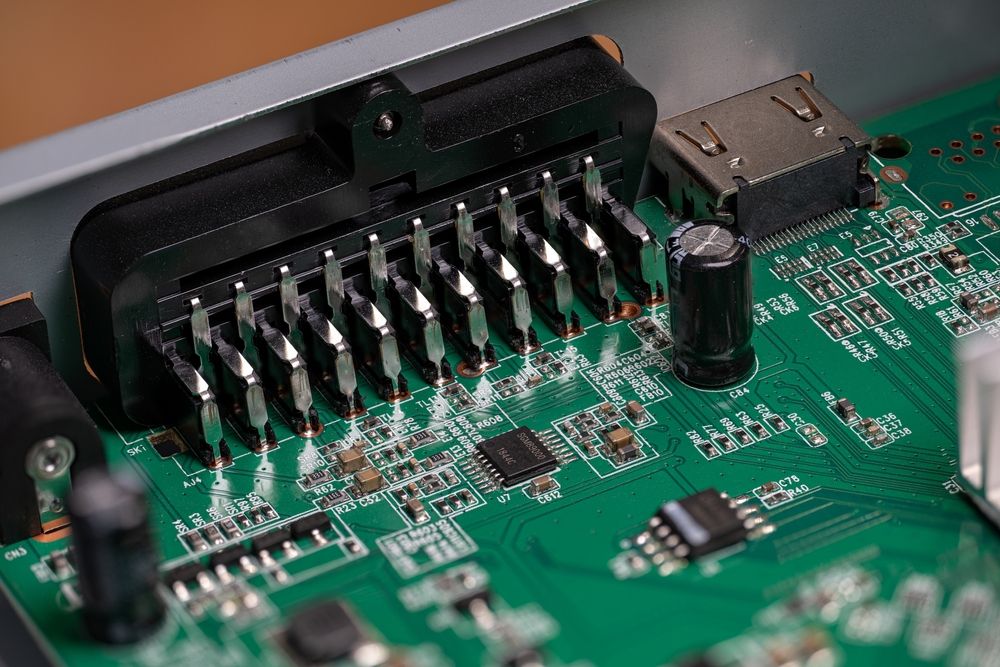

Schritt 5. Steckverbinder als Kanal-Komponenten

Bei hohen Geschwindigkeiten können der Steckverbinder und seine Übergänge einen unverhältnismäßig großen Anteil der Margin verbrauchen, daher verdienen sie dieselbe Spezifikationsstrenge wie jede andere Kanal-Komponente.

Checkliste zur Steckverbinder-Spezifikation

- Zielwert und Toleranz der differentiellen Impedanz.

- IL und RL in Abhängigkeit von der Frequenz für das gesteckte Paar und für die PCB-Übergänge.

- Übersprechverhalten und Hinweise zur Isolation im Pin-Feld.

- Optionen für Stapelhöhe und Toleranzketten.

- Annahmen zu Steckzyklen und mechanischer Haltbarkeit.

- Einschränkungen bei PCB-Footprint und Breakout.

- Verfügbarkeit von S-Parametern und etwaigen Hinweisen zum Referenzdesign.

- Second-Source-Plan auf Schnittstellenebene.

Vorgestellte Steckverbinder

Molex Mirror Mezz 202828-1506 ist ein hermaphroditischer Board-to-Board-Mezzanine-Steckverbinder mit 404 Kontakten, 2,50 mm Stapelhöhe und BGA-Montage, der Datenraten bis zu 56 Gbit/s pro differentiellem Paar unterstützt. Er verwendet einen von OCP empfohlenen Footprint, der in der gesamten Mirror Mezz family gemeinsam genutzt wird, wodurch Sie S-Parameter-Daten, Footprint-Dokumentation und Distributor-Transparenz erhalten, die Sie an Ihr Kanalmodell und Ihre BOM review anhängen können.

Schritt 6. Kabel und Flyovers: Spezifizieren Sie die Kanalerweiterung

Kupferkabelbaugruppen und aktive optische Flyovers erweitern beide die Kanalreichweite über das hinaus, was Leiterbahnen auf der Leiterplatte leisten können, lösen jedoch unterschiedliche Probleme. Kupferkabel verhalten sich als Übertragungsleitungen mit Einschränkungen hinsichtlich Impedanz, Schirmung und Biegeradius. Optische Flyovers umgehen die dielektrischen Verluste vollständig, bringen jedoch elektrooptische Wandlung sowie Anforderungen an Leistung, Thermik und Latenz mit sich. Spezifizieren Sie den Ansatz, den Ihr Link-Budget erfordert, und definieren Sie, was gleichwertige Leistung für alle Alternativen bedeutet, die Sie in Betracht ziehen.

Checkliste zur Kabelspezifikation

- Differenzielle Impedanz und Skew.

- IL und RL in Abhängigkeit von der Frequenz, einschließlich der Übergänge an beiden Enden.

- Wirksamkeit der Schirmung und Erdungskonzept.

- Einschränkungen bei Biegeradius und Zugentlastung.

- Anforderungen an Steckzyklen und Servicezugang.

- Passives versus aktives Verhalten, falls zutreffend. Bei optischen Flyovers spezifizieren Sie Wellenlänge, optisches Leistungsbudget, Latenz und Leistungsaufnahme pro Lane.

- Qualifizierungsanforderungen und Liste freigegebener Kabel.

Vorgestellte aktive optische Flyover-Baugruppe

Samtec ECUO-B04-14-015-0-2-1-2-01 (das FireFly ECUO) ist eine aktive optische Flyover-Baugruppe, erhältlich als 4-Kanal-Vollduplex-Transceiver mit 28 Gbit/s pro Kanal oder als 12-Kanal-Sender bzw. -Empfänger mit 16 Gbit/s pro Kanal. Mit OM3-Multimode-Faser sind Reichweiten bis zu 100 Metern möglich. Sie umgeht PCB-Leiterbahnverluste vollständig und verwendet dasselbe Mikrosteckverbindersystem wie Samtec's copper flyover assemblies, sodass der Footprint gleich bleibt, wenn Sie zwischen optisch und Kupfer wechseln.

Schritt 7. Verlustarme Materialien und Kupfer: Nehmen Sie das Stackup in die Spezifikation auf

Links mit höherer Bandbreite erfordern, dass das Stackup ein kontrollierter Design-Eingang ist. Ihre Kanalspezifikation sollte Materialziele und zulässige Bereiche enthalten und klar benennen, welche Annahmen Sie hinsichtlich Kupferrauheit und Prozessfähigkeit treffen.

Checkliste zur Material- und Stackup-Spezifikation

- Dk- und Df-Zielwerte bei relevanten Frequenzen sowie zulässige Variation.

- Annahmen zum Kupferfolienprofil, wenn Leiterverluste der begrenzende Faktor sind.

- Kontrollen für Glasgewebe und Skew-Risiko bei langen differentiellen Strecken.

- Tg, Td und CTE in Z-Richtung, wenn Ihre Umgebung oder Ihr Assemblierungsprofil anspruchsvoll ist.

- Annahmen zur Fertigerfähigkeit: Bohrungs-Seitenverhältnisse, Registrierung, Via-Füllung und Laminationszyklen.

- Legen Sie das Laminatsystem fest und verlangen Sie eine ausdrückliche Prüfung vor jeder Substitution.

Vorgestellte verlustarme Laminate

Panasonics MEGTRON 7 und Isolas I-Tera MT40 sind repräsentative Laminatfamilien mit extrem geringen bzw. sehr geringen Verlusten, die in digitalen Hochgeschwindigkeitskanälen eingesetzt werden. Nutzen Sie diese Produkte als Referenzpunkte dafür, was Sie von jedem ausgewählten Laminat erwarten sollten: stabile elektrische Kennwerte, Prozessrichtlinien und eine klare Produktidentität, die Sie in den Fertigungsnotizen eindeutig festlegen können.

Schritt 8. Messplan. Machen Sie Korrelation zum Ziel

Ihr Messplan benötigt klar definierte Bezugsebenen, Fixtures, Kalibrierung und De-Embedding, damit Sie Simulationsergebnisse ohne Mehrdeutigkeit mit Messdaten vom Prüfstand vergleichen können. IEEE 370-2020 ist dafür ein praxisnaher Anker und behandelt Datenqualität, Fixture-Aspekte und De-Embedding für die Charakterisierung von PCBs und Verbindungsstrukturen bis 50 GHz.

Checkliste für den Messplan

- Was Sie messen werden: TDR für das Impedanzprofil, VNA-S-Parameter für Interconnect-Segmente sowie Eye-Diagramm oder Jitter an definierten Punkten.

- Wo Sie messen werden: Definieren Sie die Bezugsebenen und benennen Sie sie.

- Wie Sie kalibrieren werden: Geben Sie die Kalibriermethode und die Rückführbarkeit an.

- Wie Sie de-embedden werden: Wählen Sie Methoden, die Sie mit Ihren Fixtures und Werkzeugen tatsächlich umsetzen können.

- Wie Sie korrelieren werden: Definieren Sie Akzeptanzkriterien für die Übereinstimmung zwischen Simulation und Messung.

Vorgestellte Messplattform

Keysight PNA-X Netzwerkanalysatoren decken Frequenzbereiche von 900 Hz bis 67 GHz ab (modellabhängig), mit mehreren internen Quellen, S-Parameter- und Rausch-Empfängern sowie Kompatibilität mit Keysights PLTS-Software für Interconnect-Charakterisierung und De-Embedding.

Wo Octopart in den Workflow passt

Bauteile für die Kanalintegrität haben oft weniger echte Alternativen. Steckverbinderfamilien, spezialisierte Conditioning-ICs und bestimmte Kabelbaugruppen können zu den Komponenten werden, die einen Build verzögern. Verwenden Sie Octopart und das BOM Tool, um drei Dinge miteinander verknüpft zu halten, solange das Design noch flexibel ist:

- Die Teilenummer und den aktuellen Lebenszyklusstatus.

- Die zugehörigen Unterlagen: Datenblätter, Modelle und Referenzdesigns.

- Alternative Produkte und Lieferantenoptionen, bevor Footprints und Schnittstellen festgelegt sind.

Je früher Sie reale Bauteildaten an Ihr Kanalmodell anbinden, desto weniger Annahmen überleben bis ins Layout. Eine S-Parameter-Datei für einen Steckverbinder, ein Produktüberblick zu einem Retimer oder eine Dk/Df-Tabelle für ein Laminat ist mehr wert als ein Platzhalter und der Plan, die Details später festzulegen. Octopart bietet Ihnen einen zentralen Ort, um Verfügbarkeit zu prüfen, Datenblätter abzurufen und den Lebenszyklusstatus zu bestätigen, solange das Design noch flexibel genug ist, um auf diese Erkenntnisse zu reagieren.

Die Disziplin, die Re-Spins verhindert

Kanalintegrität entsteht durch eine Reihe von Entscheidungen, die Sie bei Architektur, Stackup und Auswahl der Verbindungsstrukturen treffen, und wird dann vor und nach dem Layout durch Simulation, Messung und Korrelation verifiziert. Der rote Faden durch all das ist derselbe: Definieren Sie, was Sie benötigen, spezifizieren Sie es in Zahlen, wählen Sie Bauteile mit Daten, die diese Zahlen belegen, und schreiben Sie den Messplan, bevor das Layout festgeschrieben ist. Die Teams, die das konsequent tun, sind diejenigen, die sich einen Re-Spin ersparen.