Grundlagen der Signalintegritätsanalyse für Leiterplatten

Die Grundlagen der Signalintegritätsanalyse für Leiterplatten zu verstehen ist alles andere als einfach. Zwar gibt es Tools für die Signalintegritätssimulation, mit denen Sie das Verhalten von Signalen in verschiedenen Netzen während des Schaltplan- und Layout-Designs berechnen können. Sie müssen jedoch noch einige weitere Schritte unternehmen, um die Ergebnisse zu interpretieren. Dazu kommt, dass Sie für akkurate Ergebnisse auch echte Messungen anstellen sollten. Denn egal wie fortschrittlich manche Signalintegritäts- und EM-Simulationstools auch sind, sie sind nicht vergleichbar mit den Daten, die Sie aus echten Messungen gewinnen können.

Unabhängig davon, welche Methode Sie zur Untersuchung der Signalintegrität in Ihrer Leiterplatte verwenden (tatsächlich sollten Sie beide Methoden anwenden), gibt es einige wichtige Schritte, die Sie unternehmen können, um das Verhalten Ihrer Signale zu analysieren und Probleme in Ihrer Leiterplatte zu identifizieren. In diesem Artikel gehen wir die Grundlagen der Signalintegritätsanalyse Schritt für Schritt durch.

Die Signalintegritätsanalyse Schritt für Schritt

Die Signalintegritätsanalyse beginnt mit Simulationen vor dem Layout. Sobald Sie Ihr Layout aufgebaut haben, können Sie einige wichtige Post-Layout-Simulationen verwenden, um die geometrieabhängige Signalintegrität in Ihrer Leiterplatte zu analysieren. Irgendwann müssen Sie die Ergebnisse Ihrer Signalintegritätssimulation aber mit echten Messungen vergleichen; halten Sie Ihre Ergebnisse daher zum Vergleich griffbereit.

Analysen vor dem Layout

In diesem Teil geht es vor allem um das Schaltungsdesign, die Auswahl von Bauteilen und die Untersuchung davon, wie Signale zwischen den Ein- und Ausgängen von zwei Bauteilen übertragen werden. Es gibt drei wichtige Analysen, die Ihnen in dieser Phase umfangreiche Informationen über das Verhalten Ihrer Leiterplatte liefern.

-

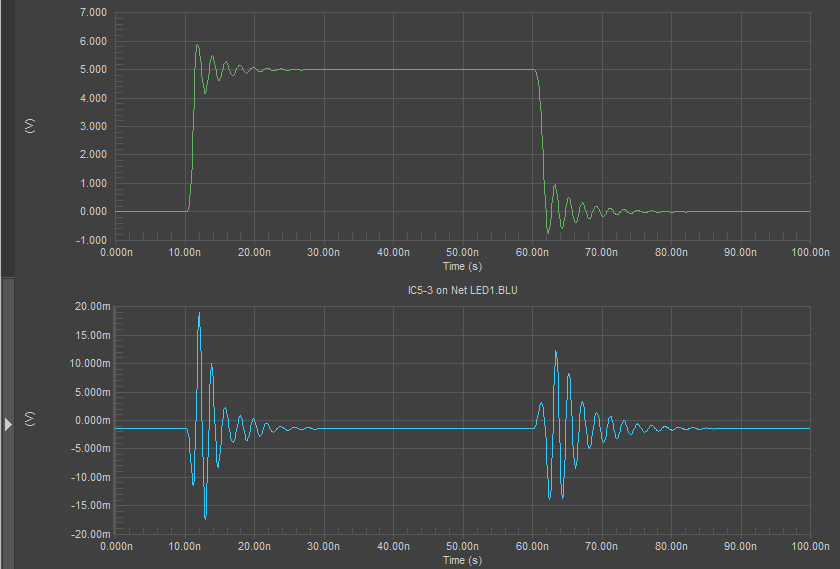

Einschwingverhalten: Einschwingvorgänge in der Verbindung zwischen zwei Puffern können im Zeitbereich mithilfe von Transientenanalysen modelliert werden. Zudem können Sie das Verhalten von Transienten auch mithilfe der Pol-Nullstellen-Analyse bestimmen. Diese zeigen Ihnen das Over-/Underschoot aufgrund von Schwingungen und die Annäherung an den vorgesehenen Signalpegel. Die genauesten Versionen dieser Simulationen (mit integrierten Schaltungen) gibt es in IBIS-Modellen, aber auch SPICE-Teilschaltungen können zur Modellierung von E/A-Puffern verwendet werden.

-

S-Parameter und Übertragungsfunktion: Bestimmte Funktionsblöcke in Ihrer Leiterplatte können als Multiport-Netzwerke modelliert werden. Das bedeutet, dass ihr lineares Verhalten in Bezug auf S-Parameter bei einer bestimmten Frequenz beschrieben werden kann. Sie können die S-Parameter aus einem Reflexionskoeffizienten im Zeitbereich bestimmen. Hierzu brauchen Sie bei Übertragungsleitungen jedoch die durch die Lastkapazität gegebene Eingangsimpedanz. Sie können die Übertragungsfunktion für Ihr Netzwerk dabei aus S-Parametern berechnen und umgekehrt. Hier ist ein ausgezeichneter Leitfaden, der die gesamte daran beteiligte Mathematik erläutert.

-

Impulsantwort: Diese Simulation verfolgt zwei Ziele: die Qualifizierung von S-Parameter-Modellen/Übertragungsfunktion für Kausalität in Ihrer definierten Bandbreite sowie die Untersuchung des Impulsantwortverhaltens für eine definierte Anstiegszeit. Mithilfe von Impulsantworten können Sie außerdem Streuungs- und Ausbreitungsverzögerungen entlang Ihres Verbindungsdesigns extrahieren. So können Sie ein bestimmtes Kanalmodell für ein spezifisches Eingangs-/Ausgangspufferpaar in einer idealen Situation bestimmen – und das noch bevor Sie das Layout der Leiterplatte erstellen.

-

Augendiagramm: Puffermodelle und Verbindungsdesign können zur Simulation eines Augendiagramms verwendet werden. Das Augendiagramm ist ein wichtiger Bestandteil der Kanalkonformität, da es den erwarteten Signalpegel, die Überschwingung, die Intersymbolinterferenz (ISI), den Jitter und die erwartete Bitfehlerrate bei einer pseudozufälligen Bitfolge anzeigt.

In komplexeren Kanälen können Ihnen die oben genannten Analysen vor dem Layout dabei helfen, Dinge wie geplante Via-Übergänge zu qualifizieren.

Analysen nach dem Layout

In diesem Teil geht es darum zu untersuchen, wie sich Störeinflüsse (Parasitics) in Ihrer Leiterplatte auf die Signalintegrität auswirken. Da parasitäre Signalintegritätseffekte Funktionen der Leiterplattengeometrie sind, müssen Sie die folgenden geometrieabhängigen Signalintegritätsprobleme untersuchen:

-

Crosstalk/Übersprechen: Der Fluch vieler Designer, der Crosstalk, entsteht durch induktive und kapazitive Kopplung. Wenn wir einmal die Auswirkungen von Crosstalk auf eine Victim- und Aggressor-Leiterbahn betrachten, tritt kapazitive Kopplung nur dann auf, wenn die beiden Leiterbahnen nebeneinander liegen. Induktives Übersprechen ist dabei nicht durch die Reichweite begrenzt; alle Leiterbahnen auf Ihrer Leiterplatte können sich also über das Magnetfeld hinweg miteinander koppeln.

-

Verhalten von Übertragungsleitungen: Sie können zwar in der Pre-Layout-Phase Übertragungsleitungsmodelle verwenden, um Signalleiterbahnen zu untersuchen; es ist jedoch am besten, wenn Sie dies direkt innerhalb Ihres Layouts selbst tun. Wenn Ihre Leitungen nicht impedanzgesteuert sind, müssen Sie untersuchen, ob Reflexionen auf der Leitung (falls vorhanden) die Signalpegel am Empfänger verschlechtern und bei digitalen Signalen zu einer treppenförmigen Reaktion führen. Bei analogen Signalen kann dies schwieriger sein, da Sie nach Interferenzen und stehenden Wellen auf der Leitung suchen. Der richtige Signalintegritätssimulator kann jedoch die einfallenden und die reflektierten Wellen voneinander trennen, sodass Sie das Verhalten jeder einzelnen Welle untersuchen können. Sie können dann den Reflexionsgrad bestimmen und schauen, ob der Signalpegel Ihren Signalanforderungen entspricht.

-

Alles, was Sie schon vor dem Layout geprüft haben: Hier geht es darum, sicherzustellen, dass Parasitics, Fasergewebe usw. das Verhalten der Signale in Ihrer Leiterplatte nicht drastisch verändern. Wenn mehrere Leiterbahnen diese Prüfung nicht bestehen, muss Ihr Layout entsprechend angepasst werden. Der erste Ausgangspunkt sind hier der Lagenaufbau und die Leiterbahngeometrie.

Tools für die Signalintegritätsanalyse

Die oben genannten Punkte mögen den Anschein erwecken, dass Sie ein komplexes Simulatorprogramm zum Erstellen und Ausführen dieser Signalintegritätsanalysetools benötigen. Welche Tools Sie genau benötigen, hängt davon ab, was Sie simulieren und auswerten möchten. In Ihrem EDA-Tool werden einige dieser Simulationen einfach mit einem Tool wie IBIS durchgeführt, während komplexere Simulationen mit mehreren Netzen einen 3D-Feldlöser oder ein vergleichbares 2D-Feldlöser-Tool erfordern.

Asymmetrische Busse ohne Impedanzspezifikation

Bei langsameren asymmetrischen Bussen ohne Abschluss ist es möglich, ein gewisses Einschwingverhalten (Schwingen) zu beobachten, das auf die Struktur der Verbindung (ihre Kapazität und Induktivität) zurückzuführen sein könnte. Das ist etwas, das bei SPI beobachtet werden kann, wenn die Leiterbahn elektrisch kurz ist. In diesen Bussen ist es möglich, das Schwingen schon vor dem Layout festzustellen, solange Sie ein Übertragungsleitungsmodell in Ihren Schaltplänen angewendet haben und die Pin-Spezifikation entsprechend definiert ist (entweder SPICE-Teilschaltung oder IBIS-Model).

Wenn der asymmetrische Bus geroutet ist, können Sie eine Post-Layout-Simulation mit dem Signalintegritätsanalysator in Ihren EDA-Tools durchführen. Diese Analysatoren können entweder eine Logikfamilienzuweisung oder ein IBIS-Modell für die relevanten Pins/Netze verwenden, um Folgendes zu simulieren:

- Crosstalk-Wellenformen und Identifizierung starker Kopplungsbereiche

- Reflexions-Wellenformen

- Andere Signalverhaltensmetriken (Anstiegs-/Abfallzeit, Überschwingen/Unterschwingen usw.)

- Durchschnittlicher Widerstand entlang der Länge der Leiterbahn berechnen

Bei asymmetrischen Bussen ohne Impedanzspezifikation kann es zu Reflexionen auf der Treiberseite kommen, wenn der Bus (zu) lang wird. Schwingen kann auftreten aufgrund der Kapazität und Induktivität auf dem Bus. Wenn das Schwingen zu einem übermäßigen Überschwingen führt, sind die Reduzierung der Leiterbahninduktivität und das Hinzufügen von Dämpfung die beiden Hauptmöglichkeiten zur Verringerung der Schwingungsamplitude. Die andere Möglichkeit besteht darin, die Dämpfung zu erhöhen, indem Sie einen Vorwiderstand einfügen, so wie Sie es auch mit einem niederohmigen Pufferausgang in einer längeren, nicht abgestimmten Übertragungsleitung tun würden.

Impedanzgesteuerte Busse

Bei asymmetrischen und differenziellen impedanzgesteuerten Bussen könnte der Abschlusswiderstand direkt am Chip anliegen. Das kann dazu führen, dass eine Simulation auf Basis einer Logikfamilie nach dem Layout nicht effektiv ist, da sie den Widerstand des Busses nicht korrekt beschreibt. Crosstalk kann dennoch simuliert werden, weil Sie die Kopplung zwischen zwei Verbindungen nur als Funktion der Anstiegszeit betrachten; das Ausmaß des Übersprechens ist entsprechend umgekehrt proportional zur Anstiegszeit – auch wenn Sie nur eine Logikfamilie zuweisen.

Im Falle einer Simulation nach dem Layout für Reflexionen und Impedanzverletzungen sollte eine Simulation in diesem Fall zumindest IBIS-Modelle verwenden, um das Pufferverhalten zu definieren, anstatt sich auf Logikfamilien-Beschreibungen zu verlassen. Solange die Pufferbeschreibung bekannt und verfügbar ist, kann sie angewendet werden, um das Verhalten des Bauteils im PCB-Editor zu modellieren. Das Standardtool für die Signalintegrität in einem PCB-Editor für Übersprech- und Reflexionswellenformen kann bei der Vorabqualifizierung des Signalverhaltens (Anstiegs-/Abfallzeit, Überschwingen, Übersprechen, gleichbleibender Widerstand und Schwingen) helfen, bevor ein fortschrittlicheres Analysewerkzeug eingesetzt wird.

Um Dinge wie Augendiagramme, Multinetz-Crosstalk und Impedanzabweichungen entlang eines Netzes zu simulieren, kann es empfehlenswert sein, externe Tools zu nutzen. Viele dieser Tools sind mit unterschiedlichen Spezialisierungsgraden verfügbar. Feldlöser sind beispielsweise eine Option. Ein Vollwellen-Feldlöser hingegen ist nicht immer erforderlich; es sei denn, Sie möchten Strahlungsemissionen simulieren oder etwas Tiefergehendes mit SI/PI oder S-Parameter im simulierten Netz extrahieren.

Die leistungsstarken PCB-Design- und Analysetools in Altium Designer® bieten Ihnen zudem einen hilfreichen Ausgangspunkt für die Signalintegritätsanalyse, mit Simulationstools für die Signalintegrität vor und nach dem Layout. Diese genauen Berechnungen bieten Ihnen eine gute Grundlage für den Vergleich Ihrer Messungen. Sie erhalten außerdem Zugang zu umfangreichen Fertigungs-, Planungs- und Dokumentationsfunktionen; und all das auf einer einzigen zentralen Plattform.

Sie können hier eine kostenlose Testversion von Altium Designer herunterladen und mehr über die branchenführenden Tools für Layout, Signalintegritätssimulation und Produktionsplanung erfahren. Sprechen Sie noch heute mit einem unserer Altium-Experten, um mehr über Altium Designer zu erfahren.