Diseño de sistemas de suministro de energía)

Este artículo pretende definir los nuevos desafíos y brindar orientación hacia cómo diseñar correctamente los sistemas de suministro de energía (o PDS, del inglés Power Delivery System) para que puedan satisfacer las necesidades de las nuevas tecnologías.

Como la tecnología de circuitos integrados permite colocar miles de millones de transistores en un único CI, esto permite fabricar chips con sistemas muy poderosos. Esto ha posibilitado el poner el equivalente a súper ordenadores dentro de videojuegos, teléfonos móviles y un montón de otros productos que otrora ocupaban habitaciones enteras. Esta misma tecnología de CI ha posibilitado el crear señales de salida en el rango de los múltiples gigaHertz, cosa que antes solo era posible con carísimos circuitos de microondas. Toda esta tecnología precisa de un excelente sistema de suministro de energía.

Al igual que con la mayoría de los avances de esta naturaleza, existen efectos secundarios que deben tenerse en cuenta. Estos CI tan grandes precisan de diversos voltajes de operación, la mayoría de los cuales no superan 1 V, con corrientes de hasta cien amperios. Junto con esto, como se verá después, las frecuencias exigidas a las barras colectoras de una PCB pueden extenderse hasta el rango de los gigaHertz. Cumplir con todos estos requisitos es una tarea compleja que obliga a los diseñadores a emplear un nivel de ingeniería mucho más complicado del que se requería en el pasado. Desafortunadamente, la mayoría de los métodos actuales en las notas de aplicación no ofrecen los consejos necesarios. Este capítulo se propone definir los nuevos desafíos y brindar orientación hacia cómo diseñar correctamente los sistemas de suministro de energía (o PDS, del inglés Power Delivery System) para que puedan satisfacer las necesidades de las nuevas tecnologías.

UNA FUENTE DE ALIMENTACIÓN IDEAL

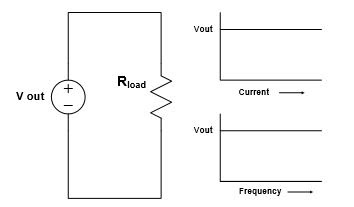

La Figura 5.1 muestra una fuente de alimentación ideal. Una fuente de alimentación ideal se suele conocer como "fuente de voltaje". Las fuentes de voltaje de los sistemas de suministro de energía tienen una impedancia de salida igual a cero, así que no importa cuánta carga (corriente) se le pida a la fuente de voltaje, el voltaje de salida permanece constante. Esto significa la menor cantidad posible entre el enchufe USB y el punto de extracción de energía. Además, sin importar a qué frecuencia se demande la corriente, el voltaje de salida permanece constante. Desafortunadamente, las fuentes de alimentación reales no son así. Todas tienen una impedancia de salida que es diferente de cero, ya sea a DC o a las frecuencias que necesita la lógica moderna.

Figura 5.1 Una fuente de alimentación ideal

UNA FUENTE DE ALIMENTACIÓN REAL

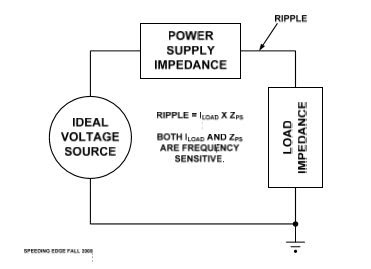

La Figura 5.2 muestra una fuente de alimentación real. Como se puede ver, existe una impedancia de salida en serie con la tensión de entrada. Este diagrama ilustra el problema de diseño que presentan los sistemas de suministro de energía.

Esta impedancia de la salida de distribución de energía varía con la frecuencia, produciendo altas impedancias a algunas frecuencias y bajas impedancias a otras. Donde la impedancia de salida es alta, los cambios en la demanda de corriente producirán cambios en el voltaje de salida. Esto es lo que se conoce como "rizado". El objetivo del diseñador es diseñar un PDS que tenga una impedancia d salida baja a todas las frecuencias en que las cargas precisen de corriente para minimizar el rizado.

Figura 5.2 Una fuente de alimentación real

¿QUÉ ES EL RIZADO?

El rizado es la variación de voltaje en la barra colectora Vdd de una fuente de alimentación. El rizado es el resultado de los cambios den la corriente de carga que generan una caída de voltaje en la impedancia de salida de la fuente, reduciendo por tanto el voltaje de alimentación de la carga. Un exceso de rizado puede causar problemas en el funcionamiento del sistema, haciendo que el voltaje Vdd sea demasiado pequeño como para que el circuito que alimenta pueda operar correctamente. Está demostrado que un exceso de rizado es la principal fuente de EMI en la mayoría de los sistemas. Se acopla directamente en las líneas de señales enrutadas sobre los planos Vdd en una PCB. (Esto es lo que genera las reglas generales de que las señales "críticas" deben enrutarse solamente sobre los planos de tierra). El exceso de rizado suele ser la razón dada para usar solamente fuentes lineales para suministrar energía al SERDES (serializador/deserializador) en enlaces de alta velocidad.

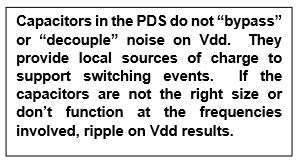

Suele haber confusión en torno al origen del rizado. No es un "ruido" que brota de una fuente misteriosa que hay que "evadir" o "desacoplar". Si existe un rizado en una barra colectora esto es una mala señal, que indica que la impedancia de la PDS es demasiado alta a las frecuencias del rizado. El remedio es rediseñar el PDS para reducir la impedancia a esas frecuencias. El método normal para reducir la impedancia del PDS es añadir capacitores de "desacoplamiento". De nuevo, estos no están desacoplando nada. Simplemente están suministrando una fuente local de carga para respaldar a un evento de conmutación. Un mejor nombre para estos capacitores son "cubetas de coulombs", porque almacenan coulombs de carga que se usa para respaldar los eventos de conmutación. Una vez que esto se comprende, el trabajo de ingeniería es determinar cuántos coulombs y a qué frecuencia hacen falta en el PDS.

Rizado en Vdd

CAPACITORES O CUBETAS DE COULOMBS

A todo diseñador le habrá ocurrido que se le pida colocar capacitores (condensadores) alrededor de componentes analógicos y lógicos. En la mayoría de los casos, las instrucciones de cuántos deben ser y dónde deben ir se sacan de la nota de una aplicación. Es raro, si es que ocurre, que estas notas de aplicación se hayan diseñado para asegurar que se usen el tipo y cantidad correcta de capacitores, o que su ubicación esté bien definida.

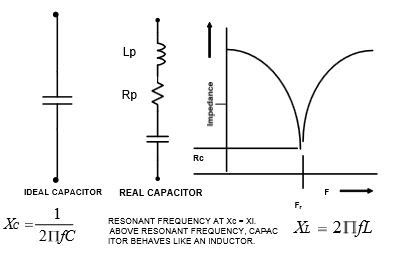

Es importante reconocer que los capacitores tienen dos parásitas que limitan su capacidad de proveer de carga en eventos de conmutación en una PCB. La Figura 5.3 es el diagrama de un capacitor ideal, un capacitor real y la impedancia vs. frecuencia del capacitor real. Ten presente que el capacitor real tiene una inductancia (Lp) y una resistencia (RP) en serie con esta. Estas son características parásitas inevitables en todos los capacitores, sin importar lo pequeños que sean.

En la parte inferior de la Figura 5.3 hay dos ecuaciones. Estas permiten calcular la impedancia de L y C como función de la frecuencia. Ten presente que a DC o f=0, la impedancia del capacitor es infinita y no se puede ver en las cargas del PDS. Ten presente que, a una DC o f=0, la impedancia del inductor es cero y no es visible antes las cargas del PDS A medida que aumenta f, Xc disminuye y XL aumenta. A una, y solamente una, frecuencia: Fr. Estas dos impedancias son iguales y se cancelan entre sí, y la impedancia que ven las cargas del PDS es la resistencia parásita: R. Es a esta frecuencia que la cubeta de coulombs es más útil en el PDS.

Por debajo de Fr, el capacitor pasa a tener una alta impedancia y no puede enviar carga. Muy por encima de Fr, el capacitor comienza a lucir como un inductor en paralelo con la capacitancia de plano de la PCB formando un circuito sintonizado en paralelo. Este circuito sintonizado en paralelo puede crear una impedancia alta que resultará en grandes voltajes de rizado a la frecuencia de resonancia del circuito sintonizado en paralelo.

Figura 5.3 Capacitores ideales y reales

IMPEDANCIA vs. FRECUENCIA DE UN PDS

Al diseñar un PDS, la tarea es crear una baja impedancia en una amplia gama de frecuencias. La figura 5.4 es la impedancia vs. la frecuencia de un único capacitor de 0,1 uF y un único capacitor de 0,01 uF montado entre Vdd y Vss en un conjunto de barras colectoras. La curva azul es el perfil de impedancias del capacitor de 0,1 uF, la curva amarilla es la impedancia del capacitor de 0,01 uF y la curva roja es la impedancia combinada de estos dos capacitores.

Las notas de la mayoría de las aplicaciones le indican al diseñador que coloque uno de los valores de los capacitores en cada barra colectora. En la Figura 5.4 se puede ver que la impedancia disminuye hasta los 100 miliohm entre los 6 MHz y los 15 MHz. En cualquier parte de este rango, la impedancia se incrementa rápidamente. Imagínate que hay un delta de 1 amperio a 100 MHz. El rizado a esta frecuencia sería de 500 milivoltios. A frecuencias superiores, las cosas se pondrían incluso peores.

Figura 5.4 Impedancia vs. Frecuencia de un capacitor de 0,01 uF y un capacitor de 0,1 uF en una PDS

CÓMO LUCEN LAS CARGAS

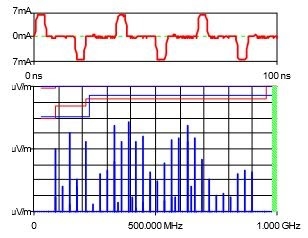

Una buena pregunta es cómo luce la carga que debe soportar el PDS. En la mayoría de los sistemas basados en CMOS, las líneas de transmisión tienen terminaciones en serie, tal como se ve en la Figura 1.7 del capítulo 1 de este libro. La forma de onda de voltaje cuando este tipo de circuito conmuta de 1 a 0 y viceversa se muestra en la Figura 1.12. La corriente se extraerá del PDS para cargar la línea de transmisión. Para determinar cuáles son las frecuencias en esa forma de onda de corriente es necesario hacer una transformada de Fourier. La Figura 5.5. muestra la forma de onda actual en color rojo en la parte superior. La excursión positiva es la corriente extraída del PDS para cargar la línea de transmisión cuando pasa de un 0 lógico a un 1 lógico. La excursión negativa es la forma de onda de la corriente cuando se elimina la carga de la línea de transmisión cuando pasa de un 1 lógico a un 0 lógico.

La parte inferior de la Figura 5.5. es una transformada de Fourier de la forma de onda de corriente que carga la línea de transmisión de un 0 lógico a un 1 lógico. Esto muestra las frecuencias necesarias para que el PDS cree una forma de onda lógica correctamente. En este ejemplo, la línea de transmisión tiene 12 pulgadas (30 cm) de longitud y la frecuencia del reloj es de 30 MHz. Ten presente que hay componentes de frecuencia que comienzan alrededor de los 80 MHz y llegan hasta los 900 MHz. Ninguno de estos son armónicos del reloj. La frecuencia más alta está determinada por el tiempo de crecimiento del borde de ataque (1 ns) y la frecuencia más baja está determinada por la longitud de la línea de transmisión.

Figura 5.5. Transformada de Fourier de la forma de onda de corriente que excita una línea de transmisión terminada en serie.

Al consultar la figura 5.4, queda claro que la estrategia clásica de utilizar capacitores de 0,1 uF y 0,01 uF, tan recomendada por tantas notas de aplicación, solo sirve para frecuencias de hasta 30 MHz. Ninguno de estos componentes de frecuencia dejan de estar respaldados por el PDS y aparecen como ruido de rizado en Vdd. Este ruido se acopla con cualquier señal enrutada en plano Vdd y puede escapar de la PCB por los cables de señal. Esta es la fuente principal de EMI en casi todos los sistemas con problemas de EMI. El mismo ruido aparece en cualquier señal lógica que esté en un 1 lógico, porque el CMOS cortocircuita las líneas de señales a Vdd cuando está en un 1 lógico.

Fuente principal de EMI

En 1995, esto se demostró en la facultad de EMC de la University of Missouri, Rolla, ahora conocida como la Missouri University of Science and Technology. Para demostrar el problema y su solución, se realizó un estudio para analizar qué pasaría cuando se emplea el enfoque clásico de circunvalar el PDS y cómo resolver el problema. El elemento 1 en las referencias al final del capítulo son el resultado de ese estudio. Cualquiera que tenga que diseñar un PDS hará bien en leerse este caso práctico. La Figura 5.6 es una gráfica de impedancia vs. frecuencia en la PCB de prueba utilizada en el estudio. La PCB de prueba tenía un capacitor de plano de unos 15 nF.

Hay tres curvas de impedancia vs. frecuencia en la Figura 5.6 La primera es la impedancia de la PCB desnuda, que muestra solamente la impedancia del capacitor de plano. La segunda es la impedancia de la placa con un capacitor de 0,1 uF y un capacitor de 0,01 uF añadidos, y la tercera es una con un capacitor de 0,1 uF y cuatro capacitores de 0,01 uF. Tal como se espera, cuando solo se prueba la placa desnuda, la impedancia es muy alta a bajas frecuencias porque el tamaño del capacitor de plano es pequeño. En la segunda curva, cuando se añaden dos capacitores, cosa que ocurriría si se siguen a cabalidad las notas de la aplicación, la impedancia combinada es baja, en donde el capacitor de 0,1 uF es resonante en serie (a unos 13 MHz) y se incrementa a medida que la frecuencia aumenta y cae de nuevo, puesto que los capacitores de 0,01 uF se vuelven resonantes en serie (aproximadamente a 45 MHz). Entre los 50 MHz y los 100 MHz, la impedancia es peor que si no se hubiesen añadido capacitores. Este fenómeno se conoce como un "hueco" de impedancia. Es el resultado de la inductancia parásita del capacitor de 0,01 uF y el que su creciente inductancia forme un circuito sintonizado en paralelo con el capacitor de plano de la PCB.

5.6 Gráfico de la impedancia del PDS vs. frecuencia del estudio de UMR, cortesía de la IEEE

Una solución que se propone con frecuencia a este problema es añadir más capacitores. La tercera curva es el resultado de añadir más capacitores de 0,01 uF, en este caso un total de 4. Lo único que ha cambiado es que el mínimo de impedancia creado por los capacitores de 0,01 uF es mucho menor y que se ha desplazado un poco en frecuencia, y que el “hueco” de impedancia ha aumentado en frecuencia pero sigue ahí. Cómo hacer que desaparezca este "hueco" en la impedancia será un tema a discutir posteriormente en este capítulo. Ten presente que, por encima de los 140 MHz, no hay cambios.

A diferencia del perfil de impedancia en la Figura 5.4, la impedancia por encima de los 100 MHz es relativamente baja. El motivo de esto es la presencia del capacitor de plano. Es el capacitor el que soporta las frecuencias en la forma de onda conmutada por encima de 100 MHz. El propósito del ensayo de UMR era mostrar a los ingenieros de EMI que la correcta contención de la EMI dependía de la ingeniería de un buen capacitor de plano en cada riel que brindara compatibilidad con formas de onda conmutadas.

La mayoría de los procesadores modernos cuentan con modalidades de "suspensión" y "actividad" para minimizar el consumo de energía cuando hay poca o ninguna actividad. Esto es especialmente importante cuando un producto está alimentado por baterías, como los teléfonos móviles. Cuando estos procesadores pasan del estado "suspendido" al estado "activo", se produce una corriente transitoria similar a la indicada en la Figura 5.5. El manejo de estas corrientes transitorias se hace mediante las mismas técnicas empleadas para líneas de transmisión conmutadas.

CAPACITANCIA DE PLANO

Se ha demostrado anteriormente, y también en muchas otras ocasiones, que es necesario usar un capacitor de plano para la correcta operación de la mayoría de los sistemas de suministro de energía. Esto se logra separando los planos Vdd y Vss con unos dieléctricos muy finos. La Figura 5.7 es un gráfico de capacitancia por pulgada cuadrada como función de la separación entre los planos para una constante dieléctrica de 4, que es la típica de la mayoría de los chapados que se usan para esto. Hay dos curvas, una roja y una negra. La curva roja es la capacitancia por pulgada cuadrada para planos sólidos y la curva negra es la capacitancia por pulgada cuadrada cuando hay una gran concentración de agujeros en los planos, causados por componentes muy estrechamente empaquetados, como las BGA.

Figura 5.7 Capacitancia por pulgada cuadrada en dos planos paralelos como función de la separación

DETERMINAR LA CANTIDAD NECESARIA DE CAPACITANCIA DE PLANO

La determinación de cuánta capacitancia de plano hace falta para una barra colectora específica es un análisis complejo. Los ingenieros necesitarán utilizar una de las herramientas listadas posteriormente en este capítulo para lograrlo. Este análisis implica una simulación que incluye una carga de corriente variable y un capacitor plano variable. La carga se activa y desactiva, y la magnitud del rizado se va midiendo a medida que se incrementa el tamaño del capacitor plano. Una vez que se ha llegado al objetivo de rizado, es necesario determinar el tamaño del capacitor plano. En este punto, es posible diseñar el stackup de la PCB para que incluya suficiente capacitancia de plano para cada barra colectora.

El diseño del PDS debe realizarse antes de diseñar el stackup de la PCB

CREAR CAPACITANCIA DE PLANO

Está claro que casi todas las barras colectoras en las PCB modernas requieren de algún tipo de capacitancia de plano para poder soportar los bordes de ataque de rápida conmutación típicos de las señales lógicas. La pregunta que surge es precisamente cómo crear tales capacitores planos. La Figura 3.9 del capítulo 3 muestra una PCB de 10 capas con dos pares de planos estrechamente espaciados, en las capas 3 y 4; y las capas 7 y 8. Están separadas por tan solo 3 mils (75 micrones) para crear capacitancia interplanar

Pero ¿qué ocurriría si el stackup que ha funcionado habitualmente en el pasado no tuviese suficientes pares de planos como para crear la capacitancia necesaria? Existen dos soluciones. Optar por no crear un stackup que tenga la capacitancia de plano requerida no es una de ellas. La solución más fácil es añadir pares de planos adicionales para resolver el problema. Existe una serie de motivos por los cuales esto podría no ser una opción viable.

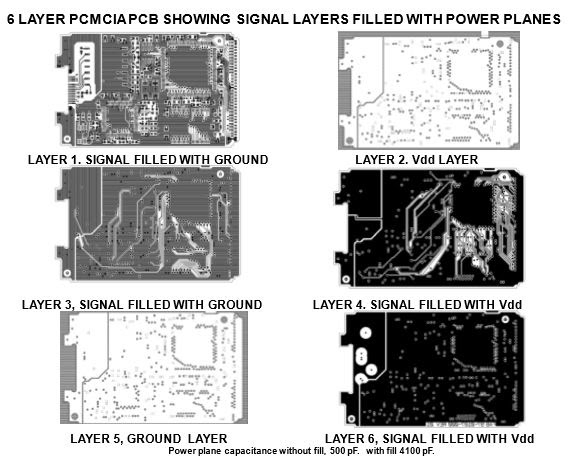

La Figura 5.8 ilustra cómo se resolvió este problema con una PCB PCMCIA de 6 capas, a la que no se le podía añadir un par de capas adicionales por motivos tanto de coste como de espesor. Este diseño falló las pruebas de EMI nada menos que seis veces. En cada ocasión, los ingenieros cambiaban la población de los capacitores discretos esperando poder arreglar el problema, pero sin éxito. El motivo por el que no funcionaba está muy bien articulado en el ensayo de UMR mencionado anteriormente. Una versión de 8 capas de este diseño se fabricó añadiendo dos capas de alimentación para crear un capacitor de plano de potencia, lo que resolvió definitivamente el problema de la EMI. Esta solución presentaba dos problemas. El primero es que la PCB era demasiado gruesa para la carcasa, y el segundo es que el coste de las dos capas adicionales habría sacado al producto del mercado en términos de precio.

En las capas 1, 3, 4 y 6, el cobre está representado en color negro. En las capas 2 y 5, las capas originales de alimentación y tierra (respectivamente), el cobre se muestra en color blanco.

Al inspeccionar una de las cuatro capas de señales (1, 3, 4 y 6), quedó claro que estas tenían espacios sin usar de tamaño considerable, que podían recubrirse con cobre y crear capacitancia de plano. Cuando se hizo esto, la capacitancia de plano antes del relleno era de medio nanoFaradio, y la capacitancia después del relleno resultó de 4 nanoFaradios, más que suficiente para resolver el problema de EMI.

La Figura 5.8 muestra el stackup de esta PCB PCMCIA antes de rellenar estas capas de señal a la izquierda, y después a la derecha. Como se puede ver en la figura, el stackup anterior solo tenía un capacitor plano con una separación de 12 mils, mientras que el último stackup contaba con cinco capacitores planos con separaciones de 4 mils.

Figura 5.8 Una tarjeta PCMCIA con relleno en la capa de señal para añadir capacitancia de plano

Figura 5.9 Antes y después de la creación del stackup de seis capas de una PCB PCMCIA

UBICACIÓN DE LOS CAPACITORES

La mayoría de los diseñadores han visto una amplia gama de "filosofías" para ubicar capacitores de "bypass", también conocidos como capacitores de desacoplamiento. Algunos de ellos están listados a continuación.

- Lo más cerca posible a cada terminal de alimentación

- En cada terminal de alimentación

- Debajo del componente

- Usar pistas para conectar el capacitor a cada terminal de alimentación.

Ninguno de los anteriores luce muy preciso. Debería existir un método preciso para determinar la ubicación de los capacitores para asegurarse de que funcionen correctamente y, a la vez, hagan que el montaje y la disposición lo más sencillos posible. De hecho, existe un método bien definido que ha sido utilizado desde hace mucho por empresas que diseñan productos de alto desempeño. Estas empresas entienden que la capacitancia de plano es un componente necesario en un PDS. Cuando este capacitor de planos es parte del PDS, la inductancia del par de planos es varios órdenes de magnitud inferior que la inductancia de montaje de cada capacitor.

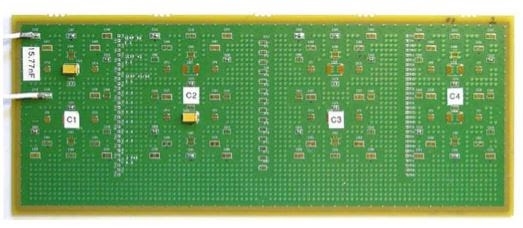

La Figura 5.10 es una PCB de prueba con una capacitancia de plano integrada muy bien diseñada. Esta PCB de prueba se utilizó para hacer una gama de medidas relacionadas con el comportamiento de los capacitores. En este ejemplo, la pregunta que se hace es: si se montara un CI en la esquina superior izquierda de la PCB, ¿podría detectar si hay un capacitor montado en C1, C2, C3 o C4? Esta prueba determinará en dónde debe colocar el diseñador cada capacitor para lograr el mejor rendimiento.

Figura 5.10 PCB de prueba usada para evaluar la ubicación de los capacitores

La Figura 5.11 es la medición de impedancia vs. frecuencia en las cuatro ubicaciones de los capacitores. Nótese que las cuatro curvas son virtualmente idénticas, cosa que indica que la ubicación del capacitor hizo poca diferencia en la impedancia general del PDS. La pequeña diferencia que se ve es el resultado de la difusión de la inductancia en el par de planos a medida que el capacitor se va separando del CI. ¡Es importante destacar que C1 está a 1/2 pulgada (1,25 cm) del CI y que C4 está a unas 9 pulgadas (23 cm)!

Figura 5.11 Impedancia vs. Frecuencia de cuatro ubicaciones de capacitores en la figura 5.8

La conclusión que se debe sacar de las pruebas antes mencionadas es que la ubicación de los capacitores de bypass en los diseños de PDS que incluyen un capacitor de plano es poco importante. Las instrucciones del autor para una disposición de PCB es que se deben colocar los capacitores en donde no interfieran con la disposición y hacer que el montaje sea lo más sencillo posible. Todas las notas de aplicación que hacen hincapié en que hay que agolpar todos los capacitores entre las vías bajo una BGA o "lo más cerca posible" están dificultando el diseño y montaje, y también encareciéndolo sin motivo.

La Figura 5.12 muestra un ejemplo de una PCB diseñada con los capacitores de desacoplamiento colocados en sitios donde no interfieren con la disposición.

Figura 5.12 Un diseño de PCB con capacitores correctamente ubicados

Punta del capacitor de desacoplamiento

MINIMIZACIÓN DE LOS "HUECOS" DE IMPEDANCIA

En la Figura 5.6 ocurrieron máximos de impedancia que degradaban el rendimiento del PDS a las frecuencias a las que ocurrían. Estos son defectos en el PDS cuya incidencia debe impedirse. En esa sección se determinó que estos defectos fueron resultado de un circuito sintonizado en paralelo, formado por el capacitor plano y la inductancia parásita de los capacitores adjuntos al plano. La Figura 5.13 es un ejemplo de un circuito sintonizado en paralelo y muestra la curva resultante de impedancia vs. frecuencia de la combinación.

Tanto el inductor como el capacitor tienen un poco de resistencia parásita. El término RL es la resistencia parásita del capacitor y el RC es la resistencia parásita de los planos. La resistencia de los planos está en el orden de los microOhm y no tiene mucho efecto sobre el comportamiento de este circuito. La resistencia parásita del capacitor tendrá un efecto importante sobre los huecos de impedancia que aparecen en los sistemas de distribución de energía.

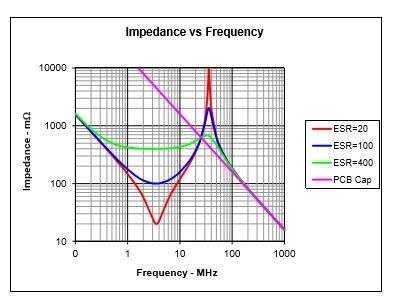

A bajas frecuencias, la impedancia del inductor es muy baja y la impedancia del capacitor es muy alta. A una frecuencia dada, estas dos impedancias tendrán el mismo valor y actuarán de tal modo que producirán una alta impedancia. Los ingenieros de RF aprovechan esto para crear un circuito sintonizado a una cierta frecuencia deseable, para así rechazar a las demás. Desafortunadamente, este comportamiento puede degradar un PDS. Existe un método para minimizar este problema en un PDS. La Figura 5.14 es una curva de un capacitor plano y un capacitor de 1 uF con tres diferentes pérdidas o ESR (resistencia equivalente en serie).

Figura 5.13 Circuito sintonizado en paralelo creado por un capacitor y un inductor

Figura 5.14 Impedancia vs. Frecuencia en un capacitor plano y en capacitores discretos

El gráfico en la Figura 5.14 contiene cuatro curvas. La curva de color morado es la impedancia vs. frecuencia del capacitor de plano en sí. La curva roja es la combinación de un capacitor de 1 uF con una ESR de 20 miliOhm y el capacitor de plano. La curva azul es la combinación del capacitor de 1 uF con una ESR de 100 miliOhm y el capacitor de plano. La curva verde es la combinación del capacitor de 1 uF con una ESR de 400 miliOhm y el capacitor plano.

Si la impedancia objetivo de la PDS era de 20 miliOhm, esto se puede lograr a 3,5 MHz usando tan solo un capacitor con una ESR de 20 miliOhm. El problema con esta solución es que, a 35 MHz, ¡Hay un hueco de impedancia de nada menos que de 10 Ohm! Esto es desastroso para un PDS. Cuando se usa un capacitor con más pérdidas (100 miliOhm), el resultado es lo que se ve en la curva de color azul. La impedancia a 3,5 MHz ha aumentado a unos 100 miliOhm y el hueco de impedancia se ha reducido a apenas dos Ohm, que está mucho mejor, pero no es suficiente.

La curva verde, usando un capacitor con una ESR de 400 miliOhm finalmente ha eliminado el hueco de impedancia. En el proceso, la impedancia a 3,5 MHz ha aumentado a 400 miliOhm. Si la impedancia objetivo era de 20 miliOhm, entonces nos hemos pasado muchísimo. Para regresar a los 20 miliOhm sin crear un hueco de impedancia, es necesario usar 20 de estos capacitores con "fugas" en paralelo. Así es exactamente cómo los ingenieros de PDS determinan cuánto de cada valor del capacitor hace falta.

La experiencia ha demostrado que el mejor tipo de capacitores cerámicos para usar en un PDS son los que tienen dieléctricos X5R o C7R. Este es el tipo de dieléctrico que se prefiere para los capacitores usados en el PDS.

Minimizar los huecos de impedancia

INDUCTORES O NÚCLEOS DE FERRITA

Muchas notas de aplicación indican a los ingenieros que coloquen núcleos de ferrita en las terminales de alimentación de los dispositivos. El motivo habitual que se esgrime es que esto "bloquea" al ruido e impide que entre por las terminales de alimentación de la PDS. Esta solución es un "paño caliente" que se usa con mucha frecuencia para resolver el problema de un exceso de ruido en el PDS, que realmente es causado por un diseño deficiente. Es muy posible que los consejos acerca de cómo diseñar mal un PDS hayan provenido de la misma nota de la aplicación. Anteriormente en este capítulo, se determinó que un buen PDS tendrá una muy baja impedancia a la frecuencia de operación. Un núcleo de ferrita tiene alta impedancia si lo que se necesita es bloquear el ruido adecuadamente.

El origen de esta regla general data de finales de la década de 1980, en la algunos dispositivos (dispositivos CMOS personalizados) finalmente se llegaron a conmutar lo suficientemente rápido como para crear frecuencias en la banda de la EMI. Los técnicos de EMI insertaron perlas$ de ferrita en los terminales de alimentación de estos dispositivos, y la EMI desapareció. La razón es que el dispositivo CMOS no tenía acceso al condensador plano de la PCB y ya no podía alternar a la velocidad necesaria como para crear frecuencias en la banda EMI.

Y si pasamos a tecnología CMOS moderna, que nos permite diseñar PCB con SERDES (serializador/deserializador) que operan a tasas de 28 Gb/s en adelante. De repente, todas estas piezas precisan de acceso al capacitor plano de la PCB para poder funcionar correctamente. La Figura 5.15 es el diagrama de ojo para la salida de un SERDES de 3.125 Gb/S donde el diagrama de ojo a la izquierda se tomó con un núcleo de ferrita en la terminal Vdd del excitador y el de la derecha es sin el núcleo de ferrita.

Figura 5.15 Diagrama de ojo de un SERDES DE 3,125 Gb/S con un núcleo de ferrita a la izquierda, y sin el núcleo a la derecha

No coloques núcleos de ferrita en las terminales de alimentación de los CI.

PCB SIN CAPACITANCIA DE PLANO

Existen miles de productos que llevan PCB de cuatro capas, con stackups similares a los de la Figura 5.16. La mayoría de las placas base para PC y videojuegos se diseñan así. Todos tiene señales de tal velocidad que necesitan capacitancia de plano para hacer su trabajo, pero esta no está presente en una PCB de cuatro capas. ¿Cómo es posible que funcionen bien sin presencia de capacitancia de plano?

Podría ser buena idea indicar por qué los capacitores de planos funcionan a mayores frecuencias que los capacitores discretos. El motivo es que la inductancia de un par de planos de espaciado estrecho está en el orden de los femtohenrios, mientras que las de los capacitores discretos mejor montados rara vez baja de 1 nanohenrio.

Figura 5.16 Un stackup típico de cuatro capas como los usados en los videojuegos

CÓMO DIVIDIR PLANOS DE TIERRA

Existen algunas "reglas generales" que le dicen al diseñador que se debe dividir un plano de tierra debajo de un convertidor A-D o hacer un "foso" alrededor de un circuito analógico o fuente de alimentación conmutada para evitar que las corrientes en el plano de tierra vayan a un lugar donde podrían degradar el rendimiento de los circuitos cercanos Ninguna de estas reglas viene acompañada de evidencias de que exista un problema real o que dividir los planos de tierra mejore realmente el desempeño. En la experiencia de este autor, seguir estas reglas tiene mayores probabilidades de crear problemas, como el de la EMI, que de resolverlos.

Existen muchos documentos publicados acerca de cómo tratar la estructura de tierra en una PCB. En todos se afirma que la manera más robusta de conectar tierras en componentes en un sistema de rendimiento óptimo es con un plano de tierra continuo y sin interrupciones, Es la estructura con las menores inductancia y resistencia que hay en una PCB, siempre que no resulten perturbadas por divisiones o "fosos".

La referencia 8 indicada a continuación es una explicación de cómo manejar la tierra "A" y la tierra "D" en un convertidor A-D. Ha sido redactada por el ingeniero jefe de Dispositivos Analógicos y explica con claridad que crear dos tierras diferentes no resuelve ningún problema, sino por el contrario, causa más.

No hagas cortes en plano de tierra

HERRAMIENTAS DE DISEÑO PARA PDS

Existe una gran cantidad de herramientas de diseño adaptadas al problema de diseño del PDS. Van desde herramientas basadas en hojas de cálculo de Excel que modelan todos los capacitores y los planos de la PCB en dos dimensiones, hasta herramientas muy complejas que modelan la PCB entera y junto con todas las cargas. Estas herramientas le permiten al diseñador simular eventos de conmutación reales, como probar un capacitor de desacoplamiento, para así ver los perfiles de rizado y caída de voltaje ocurren cuando los circuitos se encienden y apagan.

Algunos fabricantes de componentes han incluso publicado herramientas que sus clientes pueden usar para diseñar sus PDS. Entre estos se encuentra Altera, que ha publicado una herramienta que se puede descargar gratis de su página web. La herramienta es Altera PDN_Tool V10. El autor ha usado esta herramienta en gran cantidad de diseños, con excelentes resultados.

RESUMEN

Con la conversión de los conjuntos de datos paralelos y buses de direcciones más voluminosos, así como la capacidad de fabricar CI con miles de millones de transistores, el problema de diseño de PCB ha pasado gradualmente desde el tratar de enrutar miles de cables en espacios reducidos sin preocuparse mucho por la integridad de la señal o el diseño de sistemas de suministro de energía a la necesidad de preocuparse por cómo los materiales afectan a la calidad de la señal y a cómo el stackup de la PCB afecta a los sistema de suministro de energía y a la EMI.

En muchos casos, el diseño del sistema de suministro de energía es mucho más complicado que el enrutamiento de las señales. Esto se debe al hecho de que hay gran cantidad de voltajes diferentes que deben ajustarse a un número limitado de capas; precisan de secuencias complejas y sus corrientes suelen ser muy altas, con bajos niveles de voltaje operativo. Afortunadamente, las herramientas y métodos están bien desarrollados, lo que ayuda a los diseñadores a resolver todo bien a la primera.

REFERENCIAS

- Power Bus Decoupling on Multilayer Printed Circuit Boards” (en español: "Desacoplamiento en bus de potencia en placas de circuito impreso multicapa") IEEE Transactions on Electromagnetic Compatibility, Vol. 37, NO 2, Mayo de 1995.

- Smith, etal, “Power Distribution System Design Methodology and Capacitor Selection for Modern CMOS Technology” (en español: "Metodología de diseño para sistemas de distribución de energía y selección de capacitores para tecnología CMOS moderna") Publicado por Sun Microsystems, 1999

- Hubing, Todd, etal, “PWB Power Structures: Theory and Design” (en español: "Estructuras de potencia par PWB: teoría y diseño"), University of Missouri, Rolla, Noviembre de 1999.

- “Power Distribution Network Design Methodologies” (en español: "Metodologías de diseño para redes de distribución de energía"), Istvan Novak, IEC Publications, 2008.

- Smith, Larry, etal, “On Die Capacitance Measurements in the Frequency and Time Domains,” (en español: "Acerca de la medición de capacitancia en chips en los dominios de tiempo y de frecuencia") DesignCon 2011.

- Smith, Larry, “PDN Currents” (en español: "Corrientes en PDN") Publicado en SI Reflector. Disponible en Speeding Edge.

- Smith, Larry & Bogatin, Eric: “Principles of Power Integrity and PDB Design Simplified” (en español: "Principios de integridad de la alimentación y diseño de PDB, simplificados") Prentice Hall, 2017. 8. Grounding A/D Converters (en español: "Cómo aterrar convertidores A/D")‐ James Bryant, Analog Devices, EDN Página 42, Marzo 2006