Conception du système d'alimentation électrique

Cet article a pour but de définir les nouveaux défis et de fournir des conseils concernant la conception du système d'alimentation électrique (PDS) afin que celui-ci réponde aux besoins des nouvelles technologies.

La technologie des circuits intégrés, qui permet d'intégrer des milliards de transistors sur un seul circuit intégré, a donné naissance à des systèmes très puissants sur une puce. Il est ainsi possible de placer l'équivalent de superordinateurs dans des jeux vidéo, des téléphones portables et de nombreux autres produits qui occupaient autrefois des salles informatiques entières. Cette même technologie des circuits intégrés a permis de créer des signaux de sortie de l'ordre de plusieurs gigahertz, ce qui n'était autrefois possible qu'avec des circuits micro-ondes très coûteux. Toute cette technologie a besoin d'un système de distribution d'énergie bien conçu.

Il faut savoir que les circuits intégrés de très grande taille nécessitent souvent plusieurs tensions de fonctionnement différentes, dont la plupart ne sont pas plus élevées qu’un volt, avec des courants qui peuvent atteindre plus de cent ampères. En outre, comme nous le verrons plus loin, les fréquences demandées aux rails d'alimentation d'un circuit imprimé peuvent atteindre le gigahertz. Répondre à toutes ces exigences est une tâche complexe qui oblige les concepteurs à faire appel à des compétences techniques beaucoup plus poussées que celles requises par les niveaux de technologie précédents. Malheureusement, la plupart des méthodes figurant actuellement dans les notes d'application n'offrent pas les conseils nécessaires. Ce chapitre a donc pour but de définir ces nouveaux défis et de fournir des conseils sur la manière de concevoir avec succès le système d'alimentation électrique (PDS) afin que celui-ci réponde aux besoins de ces nouvelles technologies.

UNE ALIMENTATION IDÉALE

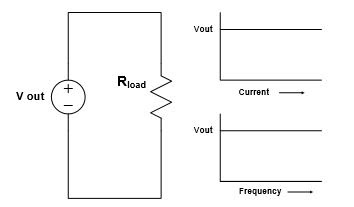

La figure 5.1 représente une alimentation électrique idéale. Une alimentation idéale est souvent appelée « source de tension ». Les sources de tension des systèmes d'alimentation ont une impédance de sortie nulle. La tension de sortie reste constante et ce, quelle que soit la charge (courant) demandée à l'alimentation. Cela signifie qu'il doit y avoir le moins d'espace possible entre la prise USB et le point de consommation. De plus, quelle que soit la fréquence à laquelle le courant est demandé, la tension de sortie reste constante. Malheureusement, les vraies alimentations ne sont pas comme ça. Celles-ci ont toutes une impédance de sortie qui n'est pas nulle, ni en courant continu, ni aux fréquences requises par la logique moderne.

Figure 5.1 Une alimentation électrique idéale

UNE VÉRITABLE ALIMENTATION ÉLECTRIQUE

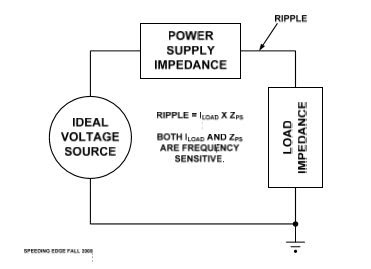

La figure 5.2 représente une alimentation électrique réelle. Comme on peut le voir, il y a une impédance de sortie en série avec la source de tension. Ce diagramme illustre le problème de conception du système d'alimentation électrique.

Cette impédance de sortie de l'alimentation varie en fonction de la fréquence, ce qui donne lieu à des impédances élevées à certaines fréquences et à des impédances faibles à d'autres. Lorsque l'impédance de sortie est élevée, les variations de la demande de courant se traduisent par des variations de la tension de sortie. C'est ce qu'on appelle l'ondulation. L'objectif du concepteur est de concevoir un PDS dont l'impédance de sortie est faible à chaque fréquence où les charges ont besoin de courant afin de minimiser l'ondulation.

Figure 5.2 Une alimentation électrique réelle

QU'EST-CE QUE L'ONDULATION ?

L'ondulation est une variation de tension sur le rail Vdd d'une alimentation. Concrètement, l'ondulation est le résultat de changements dans le courant de la charge développant une chute de tension à travers l'impédance de sortie de l'alimentation, réduisant ainsi la tension d'alimentation vue par la charge. Une ondulation excessive peut entraîner un dysfonctionnement du système en rendant la tension Vdd trop faible pour que le circuit que celle-ci alimente puisse fonctionner correctement. Il a été démontré qu'une ondulation excessive est la principale source d'EMI dans la plupart des systèmes. Celle-ci se couple directement aux lignes de signaux acheminées sur les plans Vdd d'un circuit imprimé. (C'est ce qui donne lieu à l'une des règles empiriques selon laquelle les signaux "critiques" ne doivent passer que par les plans de masse). L'ondulation excessive est souvent la raison invoquée pour n'utiliser que des alimentations linéaires afin d’alimenter les SERDES (sérialiseur/désérialiseur) dans les liaisons à grande vitesse.

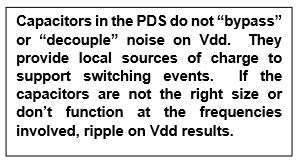

Il y a souvent une confusion sur l'origine de l'ondulation. Il ne s'agit pas d'un "bruit" provenant d'une source mystérieuse qui doit être "contournée" ou "découplée". S'il y a une ondulation sur un rail de tension, c'est que l'impédance du PDS est trop élevée aux fréquences contenues dans l'ondulation. La solution consiste à revoir la conception du PDS pour réduire l'impédance à ces fréquences. La méthode habituelle pour réduire l'impédance du PDS consiste à ajouter des condensateurs de « découplage". Les condensateurs de « découplage » fournissent une source de charge locale pour soutenir un événement de commutation. Il serait préférable de les appeler "seaux de Coulomb » (ou coulomb buckets), car ils stockent des coulombs de charge utilisés pour soutenir les événements de commutation. Il convient ensuite de déterminer combien de coulombs et à quelles fréquences sont nécessaires dans le PDS.

Ondulation sur Vdd

CONDENSATEURS OU SEAUX DE COULOMB (COULOMB BUCKETS)

Il a été demandé à chaque concepteur de placer des condensateurs autour des composants logiques et analogiques. Dans la plupart des cas, les instructions relatives à leur nombre et à l'endroit où celles-ci doivent être placées sont tirées d'une note d'application. Ces notes d'application sont rarement (voire jamais) conçues pour garantir que le bon type et la bonne quantité de condensateurs sont utilisés, ou que leur emplacement est bien défini.

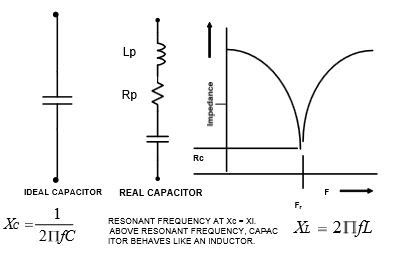

Il est important de reconnaître que les condensateurs ont deux parasites qui limitent leur capacité à fournir une charge aux événements de commutation sur un circuit imprimé. La figure 5.3 est un diagramme représentant un condensateur idéal, un condensateur réel et l'impédance en fonction de la fréquence du condensateur réel. Remarquez que le condensateur réel a une inductance (Lp) et une résistance (RP) en série avec celui-ci. Il s'agit de parasites indésirables qui sont une partie inévitable de chaque condensateur, aussi petit soit-il.

Au bas de la figure 5.3 figurent deux équations. Ceux-ci permettent de calculer l'impédance des L et C en fonction de la fréquence. Remarquez qu'à DC ou f = 0, l'impédance du condensateur est infinie et qu'il n'est pas visible pour les charges PDS. Remarquez également qu'à DC ou f = 0, l'impédance de l'inducteur est nulle et que celui-ci n'est pas visible pour les charges PDS. Lorsque f augmente, Xc diminue et XL augmente à une et une seule fréquence, Fr. Ces deux impédances sont égales et s'annulent mutuellement, et l'impédance qui est vue par les charges PDS est la résistance parasite R. C'est à cette fréquence que le seau de coulomb (coulomb bucket) est le plus utile dans le PDS. En dessous de Fr, le condensateur devient une impédance élevée et ne peut pas fournir de charge à un chargement. Bien au-dessus de Fr, le condensateur commence à ressembler à une inductance qui est en parallèle avec la capacitance du circuit imprimé formant un circuit accordé en parallèle.

Ce circuit accordé en parallèle peut créer une impédance élevée qui se traduira par des tensions d'ondulation très élevées à la fréquence de résonance du circuit accordé en parallèle.

Figure 5.3 Condensateurs idéaux et réels

IMPÉDANCE EN FONCTION DE LA FRÉQUENCE D’UN PDS

Il convient de créer, lors de la conception d'un PDS, une faible impédance sur une large gamme de fréquences. La figure 5.4 représente l'impédance en fonction de la fréquence d'un seul condensateur de 0,1 uF et d'un seul condensateur de 0,01 uF montés entre Vdd et Vss d'un ensemble de rails d'alimentation. La courbe bleue est le profil d'impédance du condensateur de 0,1 uF, la courbe jaune est l'impédance du condensateur de 0,01 uF, et la courbe rouge est l'impédance de ces deux condensateurs combinés.

La plupart des notes d'application demandent au concepteur de placer un certain nombre de ces deux valeurs de condensateurs sur chaque rail d'alimentation. On peut voir sur la figure 5.4 que l'impédance est abaissée à 100 milliohms entre 6 MHz et 15 MHz. De part et d'autre de cette plage, l'impédance augmente rapidement. Imaginez qu'il y ait un delta I de 1 ampère à 100 Mhz. L'ondulation à cette fréquence serait de 500 millivolts. À des fréquences supérieures, les choses seraient encore pires.

Figure 5.4 Impédance en fonction de la fréquence d'un condensateur de 0,01 uF et de 0,1 uF sur un PDS

À QUOI RESSEMBLENT LES CHARGES ?

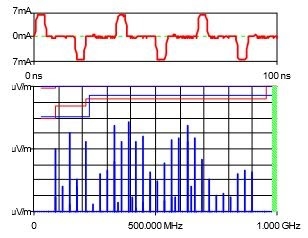

À quoi ressemblent les charges que le PDS doit supporter ? Dans la plupart des systèmes à base de CMOS, les lignes de transmission sont terminées en série, comme le montre la figure 1.7 du chapitre 1 de cet ouvrage. La figure 1.12 montre la forme d'onde de la tension lorsqu'un tel circuit passe d'un 1 à un 0 et inversement. Le courant sera tiré du PDS pour charger la ligne de transmission. Afin de déterminer les fréquences de cette forme d'onde de courant, il est nécessaire d'effectuer une transformation de Fourier. La figure 5.5 montre la forme d'onde du courant en haut en rouge. L'excursion positive est le courant tiré du PDS pour charger la ligne de transmission lorsque celle-ci passe d'un niveau logique 0 à un niveau logique 1. L'excursion négative est la forme d'onde du courant lorsque la charge est retirée de la ligne de transmission, quand celle-ci passe d'un niveau logique 1 à un niveau logique 0.

La partie inférieure de la figure 5.5 est une transformée de Fourier de la forme d'onde du courant qui charge la ligne de transmission d'un 0 logique à un 1 logique. Cela montre les fréquences nécessaires au PDS pour créer une forme d'onde logique correcte. Dans cet exemple, la ligne de transmission mesure 30 cm de long et la fréquence d'horloge est de 30 MHz. Remarquez qu'il y a des composantes de fréquence qui commencent autour de 80 MHz et vont jusqu'à 900 MHz environ. Aucun de ces éléments n'est une harmonique de l'horloge. La fréquence la plus élevée est fixée par le temps de montée du front de commutation (1 nSec) et la fréquence la plus basse est fixée par la longueur de la ligne de transmission.

Figure 5.5 Transformée de Fourier de la forme d'onde du courant pilotant une ligne de transmission à terminaison série

Si l'on se reporte à la figure 5.4, on constate que la stratégie classique des condensateurs 0,1 uF, 0,01 uF recommandée par de nombreuses notes d'application ne concerne que les requêtes jusqu'à 30 MHz environ. Aucun des composants de fréquence n'est pris en charge par le PDS et apparaît sous forme de bruit d'ondulation sur Vdd. Ce bruit se couple à tout signal acheminé par le plan Vdd et peut s'échapper du circuit imprimé par les câbles de signal. C'est la principale source d'EMI dans presque tous les systèmes qui échouent à l'EMI. Ce même bruit apparaît sur tout signal logique qui est à un niveau logique 1 parce que le CMOS court-circuite les lignes de signaux à Vdd lorsque celles-ci sont à un niveau logique 1.

Source primaire de l'EMI

En 1995, ce fait a été démontré par la faculté d’EMC de l'Université du Missouri, Rolla, aujourd'hui connue sous le nom d'Université des sciences et technologies du Missouri. Pour démontrer le problème et la façon de le résoudre, une étude a été menée pour voir ce qui se passe lorsque l'approche classique de contournement du PDS est utilisée, et comment résoudre le problème. Le point 1 dans les références à la fin de ce chapitre est le résultat de cette étude. La lecture de cette étude est fortement recommandée pour toute personne concevant un PDS. Le circuit imprimé de test comportait un condensateur plan d'environ 15 nF.

La figure 5.6 présente trois courbes d'impédance en fonction de la fréquence. La première est l'impédance du circuit imprimé nu montrant uniquement l'impédance du condensateur plan. La deuxième est l'impédance de la carte avec un condensateur de 0,1 uF et un condensateur de 0,01 uF ajoutés. Enfin, la troisième est avec un condensateur de 0,1 uF et quatre condensateurs de 0,01 uF. Comme on peut s'y attendre, lorsque seule la carte nue est testée, l'impédance est très élevée aux basses fréquences car la taille du condensateur plan est petite. Dans la deuxième courbe, lorsque deux condensateurs sont ajoutés, comme cela peut se produire en suivant une note d'application, l'impédance combinée est faible là où le condensateur .1 uF est résonnant en série (environ 13 MHz). L'impédance combinée augmente lorsque la fréquence augmente et chute à nouveau lorsque le condensateur .01 uF devient résonnant en série (environ 45 MHz). Entre 50 MHz et 100 MHz, l'impédance est pire que si aucun condensateur n'avait été ajouté. Ce phénomène est souvent appelé "trou d’impédance » (ou impedance hole). C'est le résultat de l'inductance parasite du condensateur .01uF et de son inductance de montage formant un circuit accordé en parallèle avec le condensateur plan du circuit imprimé.

Caption: 5.6 Tracé de l'impédance du PDS en fonction de la fréquence, tiré de l'étude de l'UMR, avec l'aimable autorisation de l'IEEE.

La solution qui est souvent proposée pour régler ce problème consiste à ajouter des condensateurs supplémentaires. La troisième courbe est le résultat de l'ajout de condensateurs .01 uF supplémentaires, dans ce cas 4. La seule chose qui a changé, c'est que l'impédance basse créée par les condensateurs .01 uF est beaucoup plus faible et a légèrement augmenté en fréquence. Quant au trou d’impédance, celui-ci a augmenté en fréquence mais est toujours là. Nous verrons plus loin dans ce chapitre comment faire disparaître ce « trou d’impédance » (impedance hole). Remarquez qu'au-dessus de 140 MHz environ, il n'y a pas de changement.

Contrairement au profil d'impédance de la figure 5.4, l'impédance au-dessus de 100 MHz est relativement faible. La raison en est la présence du condensateur plan. C'est ce condensateur qui supporte les fréquences de la forme d'onde de commutation supérieures à 100 MHz. L'objectif de l'article de l'UMR était de montrer aux ingénieurs EMI que la réussite du confinement des EMI dépendait de la conception d'un bon condensateur plan sur chaque rail qui supporte les formes d'onde de commutation.

La plupart des processeurs modernes disposent d'un mode veille et d'un mode actif pour minimiser la consommation d'énergie lorsque l'activité est faible ou nulle. Ceci est particulièrement important lorsqu'un produit est alimenté par une batterie, comme un téléphone portable. Lorsque ces processeurs passent de l'état de veille à l'état actif, il en résulte un transitoire de courant similaire à celui illustré à la figure 5.5. Le traitement de ces transitoires de courant se fait à l'aide des mêmes techniques que celles utilisées pour la commutation des lignes de transmission.

CONDENSATEUR PLAN

Il a été démontré ci-dessus, et dans de nombreux autres endroits, qu'un condensateur plan est nécessaire au bon fonctionnement de la plupart des systèmes d'alimentation électrique. Ceci est réalisé en séparant les plans Vdd et Vss par des diélectriques très fins. La figure 5.7 est un tracé de la capacité par pouce carré en fonction de la séparation entre les plans pour une constante diélectrique de 4, qui est typique de la plupart des stratifiés utilisés à cette fin. Deux courbes sont tracées, une rouge et une noire. La courbe rouge représente la capacité par pouce carré pour les plans qui sont pleins et la courbe noire représente la capacité par pouce carré lorsqu'il y a une forte concentration de trous dans les plans causés par des composants densément emballés tels que les matrices de billes.

Figure 5.7 Capacitance par pouce carré pour deux plans parallèles en fonction de la séparation

DÉTERMINER LA QUANTITÉ DE CAPACITANCE NÉCESSAIRE

Déterminer la capacitance du plan nécessaire pour un rail d'alimentation donné est une analyse complexe. Pour ce faire, l'ingénieur doit utiliser l'un des outils énumérés plus loin dans ce chapitre. Cette analyse implique une simulation comprenant une charge à courant et un condensateur plan variables. La charge est mise hors tension et sous tension, et la quantité d'ondulation est mesurée lorsque la taille du condensateur plan augmente. Une fois l'objectif d'ondulation atteint, la taille du condensateur plan est déterminée. À ce stade, il est possible de concevoir l'empilement des circuits imprimés de manière à inclure une capacitance suffisante pour chaque rail d'alimentation.

La conception du PDS précède l'empilage du circuit imprimé

CRÉATION DE LA CAPACITANCE

Il est clair que presque tous les rails d'alimentation des circuits imprimés modernes nécessitent une certaine capacitance pour supporter les fronts de commutation rapides contenus dans les signaux logiques. La question qui se pose est de savoir comment créer de tels condensateurs plan. La figure 3.9 du troisième chapitre montre un circuit imprimé à 10 couches avec deux paires de plans rapprochés, les couches 3 et 4 ainsi que les couches 7 et 8. Ceux-ci sont séparés par seulement 3 mils (75 microns) pour créer une capacité interplans.

Que faire si l'empilement de couches habituel qui a fonctionné dans le passé ne comporte pas suffisamment de paires de plans pour créer la capacité nécessaire ? Il existe deux solutions. Choisir de ne pas créer un empilement qui a la capacitance requise n'en fait pas partie. Afin de résoudre le problème, il convient d’ajouter des paires de plans supplémentaires. Cependant, cela peut ne pas être une option pour un certain nombre de raisons.

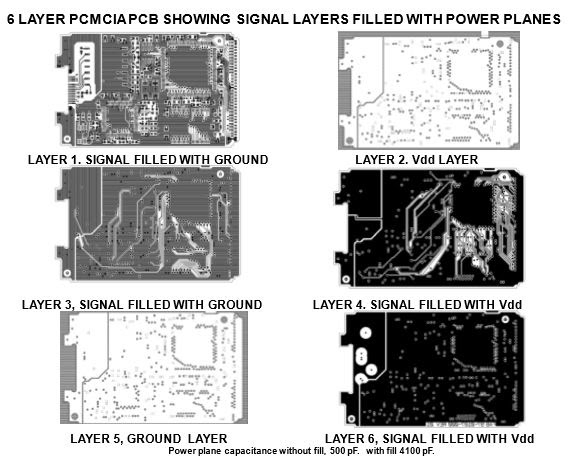

La Figure 5.8 illustre la manière dont ce problème a été résolu avec une carte PCMCIA à 6 couches qui ne pouvait pas accueillir une paire de couches supplémentaires pour des raisons de coût et d'épaisseur. Cette conception a échoué six fois aux tests EMI. À chaque fois, les ingénieurs ont modifié la population des condensateurs discrets dans l'espoir de résoudre le problème, sans succès. La raison pour laquelle cela n'a pas fonctionné est bien expliquée dans le document de l'UMR cité ci-dessus. Une version à 8 couches de cette conception a été fabriquée en ajoutant deux couches de puissance pour créer un condensateur de plan de puissance et le problème d'EMI a disparu. Cette solution présentait deux problèmes :

- Le circuit imprimé était trop épais pour tenir dans son boîtier,

- Le coût supplémentaire des deux couches additionnelles rendait le produit non compétitif sur le marché.

Sur les couches 1, 3, 4 et 6, le cuivre est représenté en noir. Sur les couches 2 et 5, les couches d'alimentation et de masse originales, le cuivre est représenté en blanc.

En inspectant les quatre couches de signal, 1, 3, 4 et 6, il est apparu clairement qu'il y avait beaucoup d'espace inutilisé sur ces couches qui pouvait être rempli de cuivre et créer une capacitance du plan. Lorsque cela a été fait, la capacité du plan avant le remplissage était d'un demi-nanoFarad, et celle d’après était de quatre nanoFarads, ce qui était suffisant pour résoudre le problème des EMI.

La Figure 5.8 montre l'empilement de ce circuit imprimé PCMCIA avant le remplissage de ces couches de signaux sur la gauche et après le remplissage de ces couches de signaux sur la droite. Comme on peut le voir sur la figure, l'empilement “avant” n'avait qu'un seul condensateur plan avec une séparation de 12 mil, et l’empilement “après” a cinq condensateurs plans avec des séparations de 4 mil.

Figure 5.8 Une carte PCMCIA à 6 couches montrant le remplissage de la couche de signal pour ajouter la capacitance du plan.

Figure 5.9 Avant et après l'empilement de six couches du circuit imprimé PCMCIA

EMPLACEMENT DES CONDENSATEURS

La plupart des concepteurs ont vu une grande variété de "philosophies" pour l'emplacement des condensateurs de dérivation, également connus sous le nom de “condensateurs de découplage”. Voici quelques exemples :

- Aussi près que possible de chaque câble d’alimentation,

- Près de chaque câble d’alimentation,

- Sous le composant,

- Utilisez des traces pour connecter le condensateur à chaque fil d'alimentation.

Cependant, rien de tout cela ne semble très précis. Il doit y avoir une méthode précise pour déterminer l'emplacement des condensateurs. Celle-ci doit garantir que ceux-ci font leur travail correctement et, en même temps, rendent la disposition et l'assemblage aussi faciles que possible. En fait, il existe une méthode bien définie qui est utilisée depuis très longtemps dans les entreprises qui conçoivent des produits performants. Ces entreprises ont compris que la capacitance du plan est un composant nécessaire d'un PDS. Lorsque ce condensateur plan fait partie du PDS, l'inductance de la paire de plans est inférieure de plusieurs ordres de grandeur à l'inductance de montage de chaque condensateur.

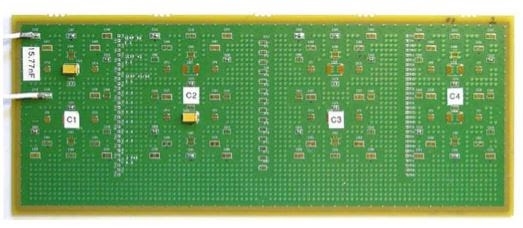

La figure 5.10 est un circuit imprimé de test contenant une capacitance du plan bien conçue. Ce circuit imprimé de test a été utilisé pour effectuer une grande variété de mesures concernant le comportement des condensateurs. Dans cet exemple, la question posée est la suivante : si un circuit intégré était monté dans le coin supérieur gauche du circuit imprimé, pourrait-il détecter si un condensateur était monté en C1, C2, C3 ou C4 ? Ce test permet de déterminer où le concepteur doit placer chaque condensateur afin d’obtenir les meilleures performances.

Figure 5.10 Circuit imprimé d'essai utilisé pour évaluer l'emplacement des condensateurs

La figure 5.11 représente l'impédance mesurée en fonction de la fréquence des quatre emplacements de condensateurs. Remarquez que les quatre courbes sont pratiquement identiques, ce qui indique que l'emplacement du condensateur a fait très peu de différence dans l'impédance globale du PDS. La petite différence que l'on observe est le résultat de la propagation de l'inductance de la paire de plans lorsque le condensateur est éloigné du circuit intégré. Il faut noter que C1 est à environ ½ pouce (1,25 cm) du circuit intégré et C4 à environ 9 pouces (23 cm) !

Figure 5.11 Impédance en fonction de la fréquence des quatre condensateurs de la figure 5.8

La conclusion qui doit être tirée des tests ci-dessus est que l'emplacement des condensateurs de dérivation dans les conceptions PDS qui incluent un condensateur plan est de très peu d'importance. Les instructions de l'auteur à un concepteur de circuit imprimé sont de placer les condensateurs là où ils n'interfèrent pas avec la mise en page et de rendre l'assemblage aussi facile que possible. Toutes les notes d'application qui insistent sur la nécessité d'entasser des condensateurs entre les vias sous une matrice de billes ou "aussi près que possible" rendent la conception et l'assemblage difficiles et plus coûteux sans raison valable.

La figure 5.12 est un exemple de circuit imprimé conçu avec les condensateurs de dérivation placés là où ils n'interfèrent pas avec la mise en page.

Figure 5.12 Une conception de circuit imprimé avec des condensateurs bien placés

Astuce concernant le condensateur de dérivation

MINIMISER LES "TROUS" D’IMPÉDANCE (IMPEDANCE HOLES)

Dans la figure 5.6, il y avait des hauts d'impédance qui dégradaient les performances du PDS aux fréquences où ceux-ci se produisent. Il s'agit de défauts du PDS dont il faut empêcher la production. Il était indiqué dans cette section que ces défauts étaient le résultat d'un circuit accordé en parallèle formé par le condensateur plan et l'inductance parasite des condensateurs fixés au plan. La figure 5.13 est un exemple de circuit accordé en parallèle et la courbe d'impédance en fonction de la fréquence de la combinaison qui en résulte.

L'inducteur et le condensateur ont tous deux une certaine résistance parasite. Le terme RL est la résistance parasite du condensateur et le terme RC est la résistance parasite des plans.

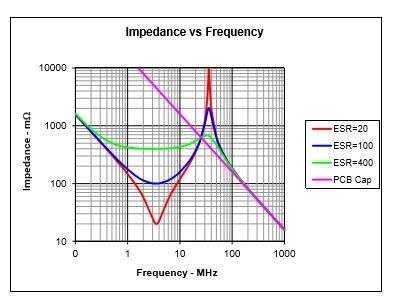

La résistance des plans est de l'ordre des micro-ohms et n'aura pas beaucoup d'effet sur le comportement de ce circuit. La résistance parasite du condensateur aura un effet majeur sur les trous d'impédance qui apparaissent dans les systèmes d'alimentation. Aux basses fréquences, l'impédance de l'inducteur est très faible et l'impédance du condensateur est très élevée. À une fréquence donnée, ces deux impédances seront identiques et agiront de telle sorte que celles-ci produisent une impédance élevée. Un ingénieur RF en tire parti pour créer un circuit accordé permettant de sélectionner une fréquence utile dans une radio et de rejeter les fréquences voisines. Malheureusement, ce comportement peut dégrader un PDS. Il existe une méthode permettant de minimiser ce problème dans un PDS. La figure 5.14 est un tracé d'un condensateur plan et d'un condensateur de 1 uF avec trois pertes ou ESR (Equivalent Series Resistance) différentes.

Figure 5.13 Un circuit accordé en parallèle créé par un condensateur et une inductance

Figure 5.14 Impédance en fonction de la fréquence d'un condensateur plan et de condensateurs discrets

Le graphique de la figure 5.14 contient quatre courbes. La courbe violette est l'impédance en fonction de la fréquence du condensateur plan par lui-même. La courbe rouge est la combinaison d'un condensateur 1 uF avec un ESR de 20 milliohms et du condensateur plan. La courbe bleue est la combinaison du condensateur 1 uF avec un ESR de 100 milliohms et du condensateur plan. La courbe verte est la combinaison du condensateur 1 uF avec un ESR de 400 milliohms et du condensateur plan.

Si l'impédance cible du PDS était de 20 milliohms, celle-ci est atteinte à 3,5 MHz en utilisant seulement un condensateur avec un ESR de 20 milliohms. Le problème avec cette solution est qu'à 35 MHz, il y a un trou d'impédance qui est de 10 ohms, ce qui est désastreux dans un PDS. Lorsqu'on utilise un condensateur avec plus de pertes (100 milliohms), on obtient la courbe bleue. L'impédance à 3,5 MHz est passée à environ 100 milliohms et le trou d'impédance a été réduit à deux ohms, ce qui est mieux, mais toujours pas suffisant.

La courbe verte, utilisant un condensateur avec un ESR de 400 milliohms a finalement éliminé le trou d'impédance. Durant le processus, l’impédance à 3,5 MHz est passée à 400 milliohms. Si l'impédance cible était de 20 milliohms, c'est un grand manque. Pour revenir à 20 milliohms sans créer un trou d'impédance, il est nécessaire d'utiliser 20 de ces condensateurs à pertes en parallèle. C'est exactement de cette manière que les ingénieurs de PDS déterminent le nombre de condensateurs nécessaires pour une valeur donnée.

L'expérience a montré que le meilleur type de condensateurs céramiques à utiliser dans un PDS sont ceux avec des diélectriques X5R ou X7R. C'est le diélectrique préféré pour les condensateurs utilisés dans le PDS.

Minimiser les trous d'impédance

DES INDUCTEURS OU DES BILLES DE FERRITE

De nombreuses notes d'application demandent au concepteur de placer des billes de ferrite dans les câbles d'alimentation des appareils. La raison habituellement invoquée est que cela permet de "bloquer" le bruit provenant du PDS sur les broches d'alimentation de l'appareil. Il s'agit toujours d'une solution pour résoudre le problème, à savoir le bruit excessif du PDS, dû au fait qu'il n'a pas été bien conçu. Il y a de fortes chances pour que les conseils sur la façon de mal concevoir le PDS proviennent de la même note d'application.

Plus tôt dans ce chapitre, il a été démontré qu'un bon PDS dispose d’une très faible impédance aux fréquences de fonctionnement. Une perle de ferrite est une impédance élevée si celle-ci doit réussir à bloquer le bruit. L'origine de cette règle empirique remonte à la fin des années 1980, lorsque certains dispositifs (dispositifs CMOS personnalisés) ont fini par commuter assez rapidement pour créer des fréquences dans la bande EMI. Les techniciens EMI ont inséré des billes de ferrite dans les câbles d'alimentation de ces appareils et les EMI ont disparu.

La raison en est que le dispositif CMOS n'avait pas accès au condensateur plan du circuit imprimé et ne pouvait plus commuter assez rapidement pour créer des fréquences dans la bande EMI. Avance rapide vers la technologie CMOS d'aujourd'hui qui nous permet de concevoir des circuits imprimés avec des SERDES (Serializer/Deserializer) qui fonctionnent à des taux de 28 Gb/S et plus. Soudainement, ces pièces doivent avoir accès au condensateur plan du circuit imprimé pour faire leur travail. La Figure 5.15 représente le diagramme en œil de la sortie d'un SERDES 3,125 Gb/S. Le diagramme en œil de gauche est pris avec une perle de ferrite dans le fil Vdd du pilote, et celui de droite avec la perle de ferrite retirée.

Figure 5.15 Diagramme oculaire d'un SERDES 3,125 Gb/S avec perle de ferrite à gauche et sans perle à droite

Ne pas placer de perles de ferrite dans les câbles d'alimentation des circuits intégrés.

CIRCUITS IMPRIMÉS SANS CAPACITANCE

Il existe des milliers de produits fabriqués sur des circuits imprimés à quatre couches avec des empilements comme celui illustré à la Figure 5.16. La plupart des cartes mères de PC et des jeux vidéo sont conçus de cette manière. Ceux-ci ont tous des signaux si rapides qu'ils ont besoin d'une capacité plane pour faire leur travail, mais il n'y en a pas dans un circuit imprimé à quatre couches. Comment est-il possible qu'ils fonctionnent correctement en l'absence de capacitance ?

Il serait bon de préciser pourquoi les condensateurs plans fonctionnent à des fréquences plus élevées que les condensateurs discrets. La raison en est que l'inductance d'une paire très rapprochée est de l'ordre des femtohenries alors que celle des condensateurs discrets les mieux montés est rarement inférieure à 1 nanohenry.

Figure 5.16 Empilement typique d'un circuit imprimé à quatre couches comme celui utilisé dans un jeu vidéo

DIVISER LES PLANS DE MASSE

Il existe des "règles empiriques" qui indiquent au concepteur qu'il doit diviser un plan de masse sous un convertisseur analogique-numérique ou "baliser" la zone autour d'un circuit analogique ou d'une alimentation à découpage pour empêcher les courants dans le plan de masse d'aller là où ils pourraient dégrader les performances des circuits situés à proximité. Aucune de ces règles n'est accompagnée de preuves de l'existence d'un réel problème ou du fait que la division des plans de masse améliore les performances. D'après l'expérience de l'auteur, suivre de telles règles risque davantage de créer un problème, tel que l'EMI, que de le résoudre.

Il existe de nombreux documents publiés sur la manière de traiter la structure du sol dans un circuit imprimé. Tous affirment que la manière la plus robuste de connecter les masses des composants d'un système pour obtenir des performances optimales est d'utiliser un plan de masse continu et ininterrompu.

C'est la structure d'inductance et de résistance la plus faible qui existe dans un circuit imprimé, tant que celle-ci n'est pas perturbée par des coupures ou des douves. La référence 8 ci-dessous est une explication de la façon de traiter la masse "A" et la masse "D" d'un convertisseur analogique-numérique. Il est écrit par l'ingénieur en chef d'Analog Devices et montre clairement que la création de deux plans différents ne résout aucun problème et risque même d'en causer.

Ne pas couper les plans de masse

OUTILS DE CONCEPTION PDS

Il existe un certain nombre d'outils de conception adaptés au problème de la conception de PDS. Il peut s'agir d'outils basés sur des feuilles de calcul Excel qui modélisent tous les condensateurs et les plans du circuit imprimé en deux dimensions, ou d'outils très complexes qui modélisent l'ensemble du circuit imprimé et toutes les charges. Ces outils permettent au concepteur de simuler des événements de commutation réels, comme le test d'un condensateur de découplage, pour voir quels profils d'ondulation et de chute de tension il y aura lorsque les circuits s'allumeront et s’éteindront.

Certains fabricants de composants ont même publié des outils que leurs clients peuvent utiliser pour concevoir leur PDS comme Altera qui a rendu public un outil téléchargeable gratuitement sur son site web. L'outil est Altera PDN_Tool V10. L'auteur a utilisé cet outil dans des dizaines de conceptions et a obtenu de bons résultats.

RÉSUMÉ

Avec la conversion de la plupart des bus de données et d'adresses larges et parallèles en paires différentielles ainsi que la possibilité de fabriquer des circuits intégrés comportant des milliards de transistors, le problème de la conception des circuits imprimés a changé. Celui-ci est en effet progressivement passé de la tentative de faire passer des milliers de fils dans des espaces réduits, sans trop se soucier de l'intégrité du signal ou de la conception du système d’alimentation, à la nécessité de se préoccuper de la manière dont les matériaux affectent la qualité du signal. Il s’agit également maintenant de se préoccuper de la manière dont l'empilement des circuits imprimés affecte les systèmes d'alimentation et les EMI.

Dans de nombreux cas, la conception du système d'alimentation est plus difficile que le routage de tous les signaux. Cela est dû au fait qu'il y a souvent de nombreuses tensions différentes qui doivent tenir dans un nombre limité de couches. Celles-ci nécessitent un séquençage complexe et leurs courants sont souvent très élevés avec des tensions de fonctionnement faibles. Heureusement, les outils et les méthodes sont bien développés pour aider le concepteur à bien faire les choses et ce, du premier coup.

LES RÉFÉRENCES

- Power Bus Decoupling on Multilayer Printed Circuit Boards” IEEE Transactions on Electromagnetic Compatibility, Vol. 37, NO 2, May 1995.

- Smith, etal, “Power Distribution System Design Methodology and Capacitor Selection for Modern CMOS Technology” Published by Sun Microsystems, 1999.

- Hubing, Todd, etal, “PWB Power Structures: Theory and Design”, University of Missouri, Rolla, November 1999.

- “Power Distribution Network Design Methodologies”, Istvan Novak, IEC Publications, 2008.

- Smith, Larry, etal, “On Die Capacitance Measurements in the Frequency and Time Domains,” DesignCon 2011.

- Smith, Larry, “PDN Currents,” Published on SI Reflector. Available from Speeding Edge.

- Smith, Larry & Bogatin, Eric: “Principles of Power Integrity and PDB Design Simplified,” Prentice Hall, 2017. 8. Grounding A/D Converters‐ James Bryant, Analog Devices, EDN Page 42, March 2006