Copper Wrap Plating in Your PCB

PCBs undergo plating processes to fill vias and apply surface finishes to protect exposed copper. There is another plating process used to ensure reliability in a PCB layout: wrap plating. This process is used in via-in-pad fabrication, but also has a similar use in sub-lamination builds. Originally introduced in IPC-6012E, the process is familiar to PCB fabricators and is widely considered to be a standard capability. Keep reading to see how the process works and how it works in different types of PCB stackup builds.

What is Wrap Plating in PCB Fabrication?

Wrap plating is a lamination process that is used for PCB stack-up builds requiring filled and plated vias. It has been named and described in the IPC standards for rigid circuit boards, and fabricators are familiar with the use of this process. The most common application for plated-over vias is for via-in-pad, but in general, every plated hole on a PCB could be filled and plated over with wrap plating.

As a fabrication process and in terms of its qualification requirements, wrap-over plating is described in IPC-6012, Revision F, referenced in Section 3.6.2.11.1. The flowchart below outlines wrap-over plating and the processes involved in each step.

The important process that finishes wrap plating is the etching process. During the plating process, the entire circuit pattern is plated. The leftover wrap plating is only applied after etching everything else away from the circuit patterns, leaving behind filled holes which are plated over with the copper wrap plating.

It is possible to perform successive rounds of wrap plating on the same layer. As described in the flowchart above, when a previously plated region has a new layer applied with a second wrap plating process, the etching step will remove it and leave behind the original wrap plating thickness. This is useful in builds that require multiple plating rounds, such as sub-lamination builds as described below.

Specifying Wrap Plating Requirements

Like all other fabrication requests, wrap plating is specified in a fabrication drawing using the fabrication notes. Specific holes or regions to be wrap plated need to be indicated in a fabrication drawing or file with a Gerber/DXF file. Wrap plating can also be specified on one side or both sides of the PCB (IPC-4761 Type 7a and 7b vias).

Information to specify for wrap plating includes:

- Desired wrap plating thickness (typical is ~1 mil)

- Wrap plating overlap onto via pads/annular rings

- Acceptable thickness and diametric tolerances

- IPC-4761 via type conformance

- Via fill material, ideally using a brand name if applicable

- Locations of specific vias requiring wrap plating

Typically, the process for assigning vias to be wrap plated is done by the manufacturer in a CAM review. They will compare the locations of landing pads and vias by overlaying the drill data on top of the paste mask data. From this, the manufacturer can identify via holes that require plugging and capping.

In Altium Designer, you can select specific vias to be wrap plated and automatically generate the data showing the filling and plating location in mechanical layers. Once these mechanical layers are created, you can then export the fill and plate information as Gerber files. Make sure to include a note in your fabrication notes that specifies which Gerber files correspond to filling and plating locations to ensure there is no confusion.

These fill and cap layers are auto-generated in Altium

Wrap Plating in Sub-Lamination Builds

Sub-lamination builds can be a challenge when large numbers of mechanically drilled blind or buried vias are used. This is because each layer span requires a plating round to form through-hole vias in each sub-lamination.

This builds up the plating thickness in each cycle, and that limits component density and drilling capability. This is especially challenging in high-reliability designs built with sub-laminations, where the via hole wall plating thickness requirement very quickly plates the surface layers up to heavy copper levels, especially when Class 3 is required. Because multiple sub-laminations may be required to reach high layer counts with dense routing, wrap plating can be used to enable PCB stack-up fabrication without excessive copper buildup on the surface layer.

This process involves plating each sub-lamination with copper to form the blind or buried vias, and then etching one or more layers to reduce the copper plating thickness on the surface. In other words, this is like a selective etching process that can help keep copper weight low, even after repeated plating cycles.

The images below show how these repeated plating and lamination cycles proceed with sub-lamination builds (two sub-laminations are shown).

Step 1:

Step 2:

Step 3:

Step 4:

Finally, this would be repeated for the through-hole vias as the final drilling, plating, filling, and wrap plating step. By enforcing this process on all via holes, the copper weight on the surface layer can be controlled and will get so large that it impacts clearances, feature sizes, or annular ring requirements.

Clearly, this adds additional process steps for each sub-lamination section. As you add processing steps, you also add processing cost due to material consumption and labor. With enough sub-lamination fabrication cycles, it's possible this could offset the cost savings you would expect when using sub-laminations as opposed to stacked microvias in an HDI build.

Reliability Under Thermal Cycling

As a PCB is thermally cycled over time, volumetric expansion creates compressive or tensile stress on the copper wrap plating, via fill material, and laminate interfaces. The amount of stress depends on a number of factors, including the temperature gradient between the board and the environment, the thermal expansion coefficients for each material involved, and number of layers in the board.

Mismatched thermal expansion coefficients for the board materials is a cause of significant stress on copper wrap plating. This can cause the plating in the via barrel to crack and separate from the butt joint. Continuous copper wrap plating can also crack at the right angle at the end of the via.

Once the interior of the via separates from the butt joint, or if the via cracks at the edge of the wrap plating, an open circuit failure occurs in the via. More failures will occur as the flexes during repeated thermal cycling. Vias that end closer to the outermost layer in the board are much more likely to fracture under thermal cycling as the board will naturally flex to a greater degree in these layers.

Despite the potential for failure in these structures, copper wrap plating is still more reliable than vias that do not use copper wrap plating. This extra layer of wrapped copper provides extra structural integrity to the plating in the via wall, as well as increasing the contact area between the via plating and the annular ring.

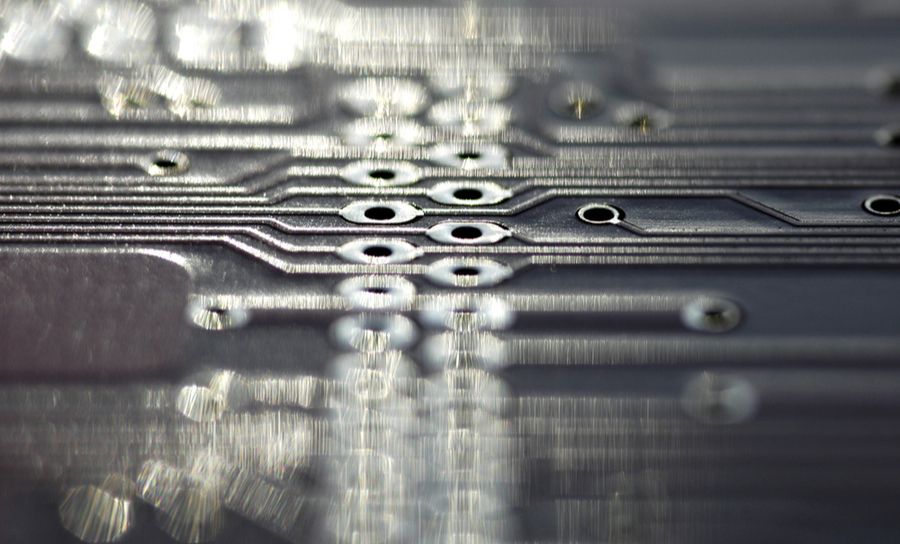

Visibility and stability of the copper on your board is valuable.

The structural integrity can be increased further by adding button plating over the top of the wrap plating. Some manufacturers do this out of principle. The button plating will also wrap over the top and bottom edges of the via, just like wrap plating. The plating resist is then stripped, the via is filled with an epoxy, and the surface is finally planarized, leaving a smooth surface. This is arguably the best way to maximize reliability while still meeting the IPC 6012E standards.

IPC 6012E compliant plating can also be easily applied to buried vias, as long as the buried vias are segmented into separate layer stacks. The inner layer stacks can be plated with copper wrap, just as in the case of a through-hole via. These vias on interior layers can be plated just as one would do with a through-hole via. Each segmented stack is plated, the final stackup can be arranged using a prepreg.

To learn more about copper wrap plating, watch the podcast episode below with Gerry Partida.

Whether you need to build reliable power electronics or advanced digital systems, use Altium’s complete set of PCB design features and world-class CAD tools. Altium provides the world’s premier electronic product development platform, complete with the industry’s best PCB design tools and cross-disciplinary collaboration features for advanced design teams. Contact an expert at Altium today