Modeling Copper Foil Roughness in Altium Designer's Impedance Profiler

Advanced transmission line models for long interconnects require that designers include copper foil roughness calculations in order to determine accurate impedance. Without the right models or design software, you’ll be left to estimate the skin effect impedance, dispersion, and parasitics in your PCB. These models can be difficult to work with by hand if you’re not mathematically inclined, but the right design tools can be used to quickly incorporate copper roughness in your impedance profiles as you create your stackup.

With the new layer stack manager in Altium Designer®, you can now include copper foil roughness factors directly in your impedance calculator. This is quite easy to do in the layer stack manager, but it begs the question: what exactly is the copper roughness factor? Which value should be used for your interconnects? This is a complex question that relates to copper deposition processes on cores and laminates. However, with some reasonable approximations in two standard models for copper roughness, you can calculate a reasonable copper roughness factor value in Altium’s impedance profiler.

Impedance Profiles in Your PCB Stackup

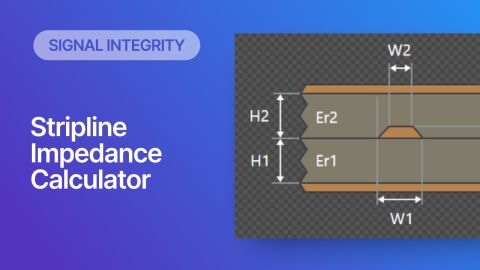

The impedance profiler in Altium Designer includes an integrated electromagnetic field solver, which calculates transmission line impedance profiles at a desired reference frequency. This solver uses the roughness, Dk, and Df values to determine an impedance value for microstrips, striplines, and coplanar geometries (both single-ended and differential). This causal solver gives the impedance assuming very high frequency propagation where the impedance begins to saturate to a fixed value and begins to become insensitive to frequency.

When it comes to modeling resistive and inductive losses due to the skin effect, there are two factors to consider:

- Interconnect cross-sectional geometry: The cross-sectional dimensions of your traces determine the skin depth for AC signals. This creates resistive and inductive impedance contributions to the characteristic impedance.

- Surface roughness and morphology of the deposited copper: Real electrodeposited copper is not smooth, and is instead created from accumulated chunks of material. In addition, etching during manufacturing will roughen the surface, which increases losses that would normally occur due to the skin effect.

The first point above can be easily included using the standard equations from electromagnetism. Modeling the second point requires accounting for the internal morphology of the copper trace, as well as the average surface roughness of the trace. If you want to work with the standard circuit model for transmission line impedance, then you’ll use the following equation to include the impedance contributions from copper roughness:

The R(rough) resistance term is related to the skin effect and the roughness of the copper used to form transmission lines. Accounting for the morphology requires developing some models which are specific to the arrangement of copper particles and their sizes.

Roughness correction factors can generally be used in a PCB-specific field solver, such as Altium Designer’s integrated field solver from Simberian. Other field solvers for full 3D solutions can be used in The roughness correction factor you use in Altium Designer’s impedance profiler needs to be determined using a causal representation. This can easily be calculated using the Hammerstad or Cannonball-Huray models, although there are many other models available that are being incorporated into EDA tools.

Calculating Copper Foil Roughness Correction Factors

The widely accepted models for calculating roughness correction factors are the Cannonball-Huray and Hammerstad models. The Cannonball-Huray model has more power and adaptability in terms of fitting to experimental data, but its form is more complex. However, enforcing causality in this model does yield a closed-form expression for the roughness correction factor in this model. The main input in the model is a measurement of the average copper particle size in a trace (called a cannonball in this model).

In contrast, the Hammerstad model provides a closed-form equation for the copper roughness correction factor, which is a function of surface roughness. This makes the Hammerstad model easier to work with as your manufacturer only needs to supply an RMS surface roughness value, which can be determined from a simple atomic force microscope (AFM) surface profile measurement.

In both models, the goal is to calculate K, which is then multiplied into R in the following lossy characteristic impedance equation:

The table below shows the formulas used to calculate K in the above equation.

I’d like to point designers to a DesignCon 2018 paper for more information on using a related set of formulas for causal copper foil roughness correction factors. Notice that the copper foil roughness correction factors above are functions of frequency, so you will need to choose a limiting frequency value (usually 10 GHz is a good benchmark). Once you’ve calculated this value, you can enter it into the impedance profiler in Altium Designer.

Including Causal Copper Foil Roughness in Altium Designer

Copper foil roughness is quite easy to include in the layer stack manager in Altium Designer. Once you’ve created a blank PCB and you are designing your stackup, simply click on the Impedance tab at the bottom of the layer stack manager. This will bring up the Impedance Profile window, as shown below. In this window, you can input the copper foil roughness parameters for your board, and the electromagnetic field solver will automatically determine the geometry that meets your target impedance within your desired tolerance.

The impedance profiler will automatically calculate the interconnect impedance for your layer stack and the roughness parameters you entered. You can then save this impedance profile and use it in your design rules using a net-specific or net-class specific custom query. This helps you semi-automate tasks like length tuning/delay tuning, differential pair routing, and signal integrity calculations.

A Note on Accuracy

The more mathematically minded designer will look at the above equations and note that there is significant variation in impedance with frequency. Because defined impedance values are most often used in high-speed digital PCBs, the transmission lines used on these interfaces are most often differential and the interfaces require high channel bandwidths.

Because of the variance over frequency, and the fact that today's EDA tools are only powerful enough to use a single impedance value as a constraint in PCB routing rules, it is appropriate to question how well the enforced routing rules will ensure channel compliance up to high frequencies. To ensure signal integrity over broad bandwidths, a designer should:

- Validate the impedance profiler value by simulating the completed routing in a post-layout simulator (like Simbeor or Ansys)

- Test fabricated transmission lines on a test board, either in-house or by requesting controlled impedance testing from a manufacturer on a test coupon

In my opinion, the best approach here is to use the Dk and Df values for your dielectrics that are at least equal to the upper limit on required channel bandwidth; normally this would be the Nyquist frequency for the interface in question.

The takeaway is: the value you get the Altium Designer's impedance profiler (and every other PCB stackup-based impedance profiler) is a good estimate, but it does not capture all the information you would get in an S-parameter plot for your transmission line. In fact, because the impedance profiler is only calculating the parameters in a straight geometry, it will never capture all the information you would get from testing and post-layout electromagnetic simulations. At low channel bandwidths (up to a few GHz), this will not matter as much, but it becomes much more important at higher bandwidths.

Altium Designer® contains many more layout and routing features for your next advanced design. Once you’ve incorporated copper foil roughness into your stackup, your impedance profile will be accessible by all the other design tools and your high-speed design rules. This is critical for ensuring your next advanced design meets important signaling standards and that interconnect losses are kept in check.

Now you can download a free trial of Altium Designer and learn more about the industry’s best layout, simulation, and production planning tools. Talk to an Altium expert today to learn more.