Testpoint Manager

Testpoints optimization

Testpoints help reduce the time required for PCBA testing and debugging, and also increase testing certainty, as the measurements are taken in automated systems. The elimination of human errors is another key benefit of automatic testing systems, which allow for reliable collection of measurement data directly from the production batch. If the product covered by ATE testing is designed to be on the market for many years, the test records history -containing measurement data collected over a long period during automated testing — may serve as a valuable source of information. For example, the stability of a device’s parameters measured from batch to batch, the reliability and quality of subassemblies or components like substrates or semiconductors used in the product, can be analyzed. Additionally, warranty or service actions can be planned accordingly.

The number of testpoints should be matched to the device’s functionality and the types of signals that are to be measured by the ATE. For fabrication tests (bare PCB), each copper trace is tested, so the number of testpoints (such as a pad, a via or a dedicated point) is much larger compared to assembly tests. Altium Designer supports the bare PCB testing through the Testpoint Manager. However, tasks related to fabrication testpoints assignment should be discussed with the PCB manufacturer. Assembly testpoints assignment, on the other hand, should be closely discussed with the design engineer, taking into account the product’s functionality, the time required for testing, test types and required precision, ATE costs and more. Some basic rules are provided below that may serve as a foundation for assembly test point assignment.

It is worth following several rules for assembly testpoints, as outlined below. These rules can serve as a guide for determining the optimal number of assembly testpoints required for reliable measurement within given accuracy or signal type, thereby reducing the time and financial costs associated with constructing the automated test stand:

- For power supply voltage verification, usually one test point per one voltage level is sufficient.

- If the voltage measurement is to be taken under load provided by the ATE, the load current should not exceed the nominal current specification of the test probe. In this case, a four wire measurement (two wires for current excitation, two for voltage sensing) can provide more accurate results by canceling out the resistance and voltage drop across the wires and probes.

- Power supply ground probes should not be shared with any voltage sensitive signals, such as analog signals or programming signals. These probes should be organized such that only power supply current flows through these probes. Usually, one common ground probe for DC voltage measurement without a current load is sufficient.

- Programming buses should have a dedicated set of test probes that includes power supply delivery (including ground connection) and data lines. It might be necessary to use additional ground probes for fast interfaces like JTAG to maintain signal integrity of the interface under control.

- Serial interfaces such as UART or SPI may have a dedicated test point for each bus line, plus one dedicated ground test point.

- Quasi-static lines, such as signal lines for LED, relay control, and similar, can have only one test probe per signal line with one ground probe that is shared amongst all low speed lines. The same applies to analog signal lines, with DC component only or with very low frequency, e.g. outputs of the operational amplifiers used at DC (excluding signal measurements or acquisition as these usually require precise measurements) or for comparators, bias voltages and more. In this case, one common ground test point can be used. This point should be tied to signal ground - a ground point on the PCB that does not carry supply current or digital logic current.

- High-speed signal buses should not be equipped with test point pads on the signal lines, as those pads impact impedance continuity (this affecting the signal integrity) along the transmission lines. In this case a dedicated solution is required (e.g. special type of differential high impedance test probes or probes with PCB sockets installed during assembly). The same applies to radio frequency signals - a coax cable probe should be used to maintain the impedance match and desired load for the RF module that is under the test (usually 50Ω).

- Testpoints for high-impedance signal lines, such as pH sensors, high impedance biasing networks, high impedance resistive dividers, precise integrated circuits and more should be designed as a shielded or guarded connection. Shielding is necessary to prevent any external interference to be coupled into the sensitive or high impedance circuits and guard fencing reduces leakage current within the test probes and ATE. The ATE wiring may be prone to significant crosstalk and may act as an antenna injecting unwanted disturbances into the circuit by the test probes. If precise and sensitive circuits are under the scope of automated testing then a dedicated solution may be provided by a vendor of the ATE (or test probe manufacturer). Design engineers may also choose a different net to be tested - e.g. to provide a test point of high impedance line after a buffer (that in principle has a low output impedance and is less prone to any external EMI coupling or current leaks).

Labeling the testpoints using the silkscreen layer of the PCB, for example GND, VCC, SCLK, MISO, MOSI or similar reduces any errors related to ATE setup and provides a guide for manual measurements during device’s debugging. Additionally, multiple sets of ground points across the PCB can help with the signal integrity and noise reduction of the measured signals. During evaluation of the ATE different grounds can be used to verify the signal integrity or noisiness of the analog signal measurements.

Fault detection in the automated testing environment

One of the key goals of adding testpoints in PCB design is to improve fault detection and reduce time to market while maintaining high quality of the product. Testpoints, when used with ATE, also provide a valuable source of information related to product quality control. Thanks to the Testpoint Manager tool, PCB designers can quickly set up and provide all necessary information such as: x/y location and type of the test point) to test engineers who prepare an ATE test stand - a fixture that includes a nail bed with instrumentation (composed of signal sources, DMMs and more). ATE setup and assembly require the definition of assembly testpoints, which one of the key features of the test point manager included in Altium Designer - to support test engineers.

For fabrication tests of PCB traces, as mentioned earlier, it is mandatory to test all connections on the PCB level without any components assembled. This means that the PCB manufacturer must specify the location of specific points on the PCB for the flying probe head. The coordinates of the fabrication testpoints can be obtained in the Test Point Manager as well. However, for hardware designers and PCBA manufacturers, it is more important to manage assembly testpoints, as they define the locations on the PCB for signal measurement or excitation, which prove the correct assembly and proper operation of the assembled PCB.

The use of testpoints for PCB design is almost always time and cost effective. The exceptions are lowvolume, budget-conscious or simple products with basic functionality that do not benefit from automated testing.

In case of low-volume products, the time required to develop the ATE system is not cost and time efficient compared to manually testing a small number of PCBs. Moreover, for highly specialized products with small batches, such as high precision data acquisition systems or RF systems, testing (and calibration) activities are usually carried out manually or semi-automatically by highly skilled specialists with high precision instrumentation.

For budget-conscious and simple electronics products, it is often that some of the PCBAs, after final assembly, may be faulty or damaged when powered on, e.g. toys. These types of products typically do not require any programming or calibration. The same applies to devices with simple functionality, such as LED drivers or flashlights - i.e. automated, or even manual, testing of this type of electronics is not cost and time efficient. It is often more economical to scrap a faulty device rather than attempt to repair it.

In other cases, implementing automated product testing in the design workflow helps reduce costs and ensures quality control (maintaining an appropriate level of quality throughout the product’s lifespan). The Testpoint Manager provided in the Altium Designer is one of the key tools for automated testing methodology, offering a convenient method for defining and managing testpoints.

One of the main goals of automated testing is to detect assembly defects on the PCB level that are related to assembly quality (e.g. ensuring that temperature and speed settings for the reflow process are adjusted for proper SMD component assembly). Another important goal for automated testing is to ensure that the assembled device meets the required specifications within large production runs and to detect any anomalies, such as deviations in: the power supply voltage stability or SMPS efficiency are outside required specification.

It should be noted that the determining typical values and tolerances for the measured signals should take into account manufacturing and components variations. If the margins are too narrow (for example: if component tolerances are not factored into the margin calculations), the production yield may be too low, even though devices are functional and within specification. On the other hand, wide margins may lead to the false acceptance of products that are outside the technical specifications, e.g. accuracy or thermal drift of such devices are measured to be beyond specification.

Typical values and margins should be carefully considered during the design phase and hardware verification of the prototypes. Additionally, the long term time drift and thermal stability of the test system should be evaluated accordingly to exclude any drifts of the measurement instrumentation related with thermal drift of time drift. Fixture and ATE inspection, such as using a so-called golden sample of the tested product plus regular maintenance and validation period should be specified in the test methodology and ATE maintenance because fixture and ATE degradation (or thermal drift) can have the same impact as PCBA degradation resulting in yield reduction.

Measurements and testing reliability - risks related with automated testing

Automated testing, whether in the form of a flying probe or tests conducted in a dedicated fixture with instrumentation, is based on the excitation and measurement of electrical values present on the PCB. In most cases, the measured values are voltage and current. Whether a complete device (or just assembled PCB) passes the test is determined by comparing the measured value with the correct value, which is in most cases specified as a value range, e.g. 4.9V…5V…5.1V. Values beyond the defined range indicate a board or device failure, meaning that the PCB assembly process or its components requires repair, replacement or disposal if it is economically justified.

It is worth keeping in mind that the correct values range determines whether the device passes the test or not. Defining the expected range of values is not a trivial task and it is often carried out in the form of statistical analysis and analysis of the values obtained from several or more devices in order to check whether the distribution of measured values correlates with statistical calculations and design expectations.

Some faults may go undetected if the defined values’ range is not set correctly. For example, the supply voltage provided by the 1.8V LDO regulator is measured after the ferrite bead that has specified DC resistance (say 0.1Ω). This DC resistance is accounted for when defining the correct values span under the load. The test is conducted with a current load of 200mA - TP100 is loaded with a current of 200mA - see Figure X2. The pass criteria for this measurement are set within the range of 1.5V...1.85V (DC drop across L100 is included). With the given pass criteria is it not possible to detect, for example, a broken ferrite bead whose resistance has increased from the nominal 0.1Ω up to 1Ω (10 times). The device can still operate correctly with a lower supply voltage on the power rail (1.6V instead of 1.78V typical value including DC drop on the ferrite bead with its nominal resistance of 0.1Ω) and may not cause any noticeable issues for the end user. However, a ferrite bead failure may worsen over the time - the resistance can deteriorate, leading to an excessive voltage drop that could result in complete loss of functionality. To address this issue, the correct voltage range for 1.8V rail should be limited to LDO tolerances and DC drop across the resistance span of the ferrite bead with 5% to 10% of additional margin, for example: 1.725V...1.85V.

Figure 1: 1.8V LDO test - Tp100 loaded with 200mA. When L100 (ferrite bead) resistance is 0.1Ω then the typical voltage at TP100 is 1.78V (not including tolerance of the LD1117 1.8V LDO).

On the other hand, setting too narrow ranges for the measured values, relative to component tolerances, can result in low production yield of the assembled PCB modules, even though these PCBAs are fully functional.

Mechanical aspects of the nail bed and test fixture are also critical. The pressure applied by the multiple test probes to the PCBA as well as the arrangement of test points across the PCBA that will transfer the forces exerted by the needles also require careful design.

Insufficient contact pressure may result in an unreliable connection between the test probe and test point, leading to false or uncertain readings. On the other hand, if the pressure of the PCBA against the nail-bed is too high then the PCBA board may be damaged during testing (e.g. components can crack or desolder from the pads). High pressure between test probes and test points also causes increased wear of the needles. To conclude: a proper placement of test points is important for automated and reliable testing.

Test point placement and arrangement is supported by Test Point Manager parameters such as:

- Management of the test points grid - Figure 2

- Management of the test points clearance rules - Figure 3

Figure 2: Grid configuration options

Figure 3: Testpoint clearances options

These alignment capabilities allow test points to be assigned to the PCB in a way that minimizes the risks associated with forces of the test fixture. Additionally, it is also possible to plan force distribution as required for a given PCBA (e.g., evenly over the whole space of the PCB or with a specific and accepted distribution across the PCB area that results from the mechanical properties of the PCBA).

Furthermore, there are several functional tests of the PCBA that should not be carried out in automated fashion, by excitation or measurements of the test points because obtained results may not be reliable. These can include, for example:

- Automated tests of high precision data acquisition systems - devices in which the resistance of connections or thermal voltages associated with the test system (e.g. contact between the test point and test probe) can significantly alter the measured value. In addition, these devices often require a warm up period: being powered on and allowed to stabilize for a certain duration to ensure that component temperatures and thermal drifts are in steady state prior to the ATE characterization). Measurements of the PCBA (or a complete device) taken immediately after power up, without a warm up period, may affect the measurements obtained in the ATE due to thermal drift of the device under test.

- PCBAs and devices operating at radio frequency - in this case a specialized test probe type are required. probes are typically connected to a flexible coaxial cable with controlled impedance along the instrumentation setup. Some test probes (e.g. - see Figure 4) are designed to interface directly with an u.fl socket. In such cases, the PCB designer should foresee a footprint for an RF connector on the PCBA. Regular test probes, typically used for voltage measurements, should be avoided, as they do not provide adequate impedance match between the signal source and the ATE. Using unmatched probes can lead to distorted readouts, increased coupling of the RF signals to the ATE or other circuits on the PCBA and also poses a risk of damage for the RF components.

- High power systems - these usually require specialized connectors capable of handling high currents or high voltages. In case of high current devices, a dedicated set of test points may be a suitable solution (as long as the probes can share the current almost equally - this property should be guaranteed by the design of the PCB). The PCBA pressure for multiple current test probes should be equalized as well and distributed across the PCB without risk of PCB bend or component cracks. For high voltage application a proper clearance is required. Safety regulations and required voltage levels should be analyzed before the test bed and test fixture is designed. Arcing or increase in the contact resistance for high current application will reduce the life time of the test probes and may cause damage to the PCB. Both arcing and increased resistance between the probe and test point during high current measurements generate the heat, which may cause damage to test probes or the PCB.

Figure 4: High frequency test probe (source Ingun)

PCB design engineer must consider the test point type (that best suits the test probe) on the PCB level. Test points can take various forms of a THT pad, via or a circular test point pad as well as an RF socket that provides connection to a specialized test probe. Test point size, shape and type as well as its connection to the PCB by copper traces should include the following criteria:

- Current Load: Ensure the test point can safely handle the current during measurement without overheating or causing damage.

- Voltage Levels: Consider the voltage present at the test point during the test, including any voltage spikes due to inductance or transient conditions.

- Clearance: Ensure adequate clearance between test points, especially for high-voltage measurements, to prevent arcing.

- Current Sharing: If multiple probes are used to measure current, ensure the resistance is balanced to evenly distribute the current across all probes.

Test engineers should support the PCB development to implement design for testing principles.

Testpoint Manager in Altium Designer

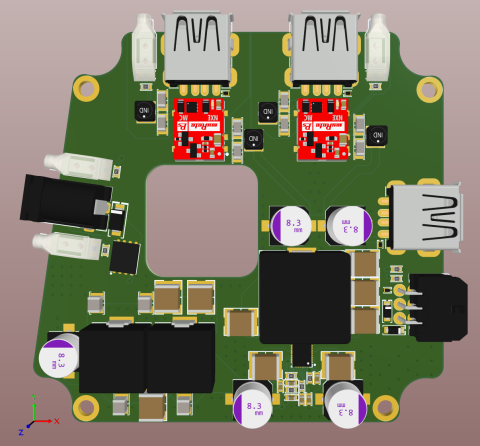

The following tutorial presents the capabilities and usage of the Altium Designer’s Testpoint Manager. Next section describes the test point configuration and assignments methods for an exemplary PCB design that is shown in Figure 5.

Figure 5: PCB layout used to demonstrate Testpoint Manager capabilities

Board given in Figure 5 contains both THT and SMD components. In addition, a set of top layer pads are added to serve as dedicated test points (bottom right corner of the board). The main goal is to assign a test point status to different objects that are located on the PCB by means of the Testpoint manager integrated in the Altium Designer. In this example, only assembly test points are used. It is also assumed that test points will be assigned only to the top layer, as dedicated pads for test probes (TP5, TP6 and TP7) are already on the top layer. If the design is complex, assigning test points to both sides (top and bottom) is also possible in the Testpoint Manager.

Interface to the PCB is done through the J1 connector (THT component, left side of the PCB). This component is an interface for analog signals used in the final product. As J1 is a THT connector its manual assembly takes place after functional tests, so in this case THT pads of J1 connector may be used as a set of test points for automatic testing right after SMD assembly is completed.

It is recommended, in the first step, to create a net class containing all nets connected directly to the J1 pads - having a dedicated class per each test point type makes the test point management much easier and faster. Creating a new net class can be done by accessing the Class Editor (Design->Classes) - Figure 6.

Figure 6: Net classes definition for test point management purposes

A class named, for example, AJinp can be defined and added to a set of net classes of the project. All nets related to the J1 connector are now included in the AJinp class - see Figure 7.

Figure 7: Net class AJinp created

Next step is to open the Design Rules editor: Design---> Rules and select Assembly Test Point section - see Figure 8.

Figure 8: Project rules window for Assembly Test Points

In the Rules and Constraints editor window, shown in Figure 8, parameters related to the assignment of assembly test points for the AJinp class can be edited. It is important to select the top layer checkbox (Allowed Side: Top) as the layer dedicated to test points assignments. Additionally «Allow testpoint under component» option should be selected, as the J1 connector is on the same side as the test points - THT pads of this connector. Without this option selected, test points will not be added or the PCB designer should change the location of the test points to the bottom side.

The next step is to run the Testpoint Manager (Tools --- >Testpoint Manager) - see Figure 9. Then, the Assembly Testpoints button should be clicked, and the Assign All option should be selected. When this button is clicked, the test points will be assigned to the eight pads of the J1 connector (eight signal lines that were previously added to the AJinp class).

Figure 9: Testpoint Manager main window used to assign testpoints

The assignment results are shown in Figure 10 - eight testpoint statuses are added to the J1 connector’s pads. Figure 11 presents the properties window of one of the pads of the J7 connector. Note that the assembly testpoint check box is selected, meaning that the testpoint status has been assigned to a given pad automatically by the Testpoint Manager.

Figure 10: Test point assignment results

Figure 11: Properties of a pad with test point status assigned

Dedicated SMD pads are the next to be assigned. These pads are connected to the outputs of the operational amplifiers and to the power supply line - see Figure 12. A set of rules will be defined in the next steps to automatically assign test point statuses to these objects (circular SMD pads on the PCB).

Figure 12: Dedicated test points presented on the schematic

Power line test points will be assigned in the first step. The arrangement of power line pads is shown in Figure 13. These power supply test points are arranged in a 100 mils x 100 mils grid. The procedure is similar to steps described earlier: a net class called, for example, Power, which will include VCC, VEE and GND nets is created. This class is then used within the Testpoint manager. Additionally, the next rule for test points in the Project Design Rules is created and assigned to Power net class only. A grid spacing of 100 mils can be activated (including tolerance specification if the grid layout of test points in the project is not uniform). Next, the pad size specifications(Min/Max/Preferred) are set so that only the test pad size of 1.5mm (diameter of dedicated pads for test points) falls within the specified range. The final test point configuration for the power lines is shown in Figure 14.

Figure 13: Power supply test point alignment

Figure 14: Power supply testpoint configuration in the project design rules

The next step is to open the Testpoint Manager tool and assign the test point status to the Power net class. Three additional testpoints (Figure 15) should be assigned after clicking the Assign All button. So far 11 nets with PCB objects like THT and SMD pads have been assigned a test point status.

Figure 15: Power supply testpoint assignment

There are four testpoints left to assign. These points are connected to the outputs of the operational amplifiers (TP1, TP2, TP3, and TP4) - see Figure 12. The physical appearance of these points is the same as that of the power line test points(1.5mm in diameter), so these test points can be included in the Power net class as well. However, to keep the project rules related to the testpoints clearly defined and easy to read and manage, it is recommended to create a dedicated net class for these four testpoints only - see Figure 16.

Figure 16: Dedicated class for operational amplifier outputs nets

Similar to the configuration for net class described earlier (assigning a new net class to test points) can be created as described in Figure 14. In order to select test points connected to the outputs of the operational amplifiers, the testpoints diameter was reduced to 1.49 mm on the PCB level. A change of 0.01 mm is negligible with respect to PCB production or functionality of the final project. With size change, it is much easier to select only these pads to be used as assembly testpoints. On the other hand, assigning the net to the OPamp net class, defined earlier, will work the same way. However, if the project is complex, changing the dimensions of the test points to values not present in the project reduces management efforts related to selecting the right objects for testpoint assignment. Additionally, other physical aspects of the dedicated testpoints can be changed to distinguish between different testpoint purposes (e.g., power lines, analog lines, or digital signals). The final configuration for the operational amplifier testpoints is given in Figure 17. Test point assignment results are given in Figure 18.

Figure 17: Configuration for testpoints with modified diameter

Figure 18: Assignment result for testpoints with modified diameter

The result of the Testpoint Manager’s assignments can also be viewed in project files accessed through the menu tab: File--->Assembly Outputs--->Test Point Report. The result of the work is shown in Figure 19 (it is the text content of the test point report, including net names, coordinates, and test point names).

Figure 19: Assembly output file - testpoint report generated automatically by Altium Designer

Testpoints assignment for the OPamp net class is the last step related to assembly testpoints. The assembly output file, shown in Figure 19, can be used by the test engineers to prepare a nail bed and the fixture. PCB project printouts generated automatically within Altium Designer, as well as the instrumentation list and the list of correct values for each testpoint, are also required to complete the ATE design.

Conclusion

An automatic approach to the testpoint assignment to selected objects on the PCB is described. Automation in the assignment process allows for easy and time-efficient testpoint assignment, including the location of the testpoint and its physical characteristics (e.g. size or layer location of the PCB with x/y coordinates).

In the case of complex PCB designs, the integration of the Testpoint Manager with the Net Class Editor and the ability to assign testpoints based on the object’s physical appearance reduce the time required for test stand development (e.g. test fixture or nail bed).

Testpoints play a crucial role in reducing PCBA testing and debugging time while increasing measurement reliability in automated systems. They help eliminate human errors and ensure accurate data collection directly from production batches.

Altium Designer's Testpoint Manager simplifies the testpoint assignment process, making it easier for PCB designers to integrate testpoints efficiently. Our latest whitepaper explores the theoretical importance of testpoints, covering optimization strategies, fault detection in automated testing, and best practices for reliable measurements. Additionally, it provides a step-by-step tutorial on using Testpoint Manager in Altium Designer, including configuration and assignment methods for an exemplary PCB design.