The PCB Layout "Rules of Thumb" and Guidelines Debate Rages On

To this day, I still see many PCB layout "rules of thumb" that first became common nearly 20 years ago. Do these rules still universally apply? The answer is a firm "maybe." Many of the conversations you'll see on forums regarding PCB design rules devolve into an always/never discussion, causing some designers to use or ignore common design rules in situations where they may not apply. In some cases, this will not cause a board to fail. As some PCB design veterans have said, the board might work just fine on accident.

The discussion around PCB layout rules of thumb is not that these rules are correct or incorrect. The problem is that the discussion around these rules often lacks context, leading to the always/never type of discussion seen in some popular forums. My goal in this article is to communicate the context behind the common PCB design rules. Hopefully, this will illustrate when these different rules are applicable and when they should be avoided.

The Common PCB Layout Rules of Thumb

Without further adieu, let's break down some common PCB layout rules of thumb and see if we can provide some helpful context behind these design rules.

Orthogonal Routing

I discussed this particular rule of thumb in a recent article, so I'll only repeat the important points here. The orthogonal routing rule states that traces on adjacent signal layers should be routed along perpendicular directions to eliminate inductive crosstalk between traces on these adjacent layers. At high frequencies, you'll find that capacitive crosstalk starts to dominate, producing current spikes between orthogonal traces.

At low rise time and low frequencies (less than a few GHz), there won't be appreciable capacitive crosstalk between orthogonal traces on adjacent layers. At high frequencies in RF boards (several 10s of GHz), cavity resonances in the fiber weave and between ungrounded conductive structures will create strong electromagnetic resonances at specific frequencies. This can then induce strong crosstalk between signal layers, even if the traces in each layer are routed orthogonally.

The better choice at any frequency is to simply separate signal layers by plane layers. This is especially true with modern PCBs, which run at high edge rates/frequencies simply due to the logic families used in modern ICs. If you do suspect you'll be fine using orthogonal trace routing, you should still run a basic crosstalk simulation with orthogonal traces and check whether crosstalk will break through your noise margin. Be sure to carefully plan your return path as well, as this is one of the primary problems with orthogonal trace routing.

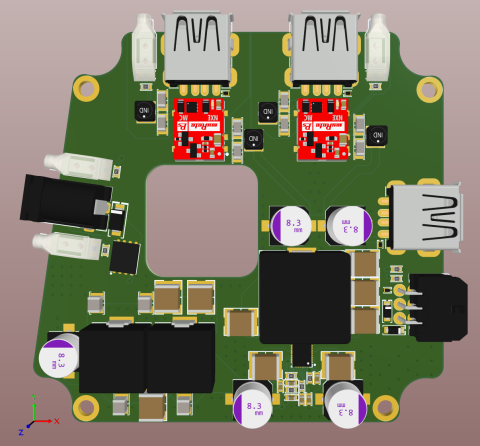

Thermal Reliefs on Through-Holes, Vias, and Pads

This is one of those classic 'always/never' types of debates. One designer will say that they never use thermal reliefs on holes and they've never had soldering or assembly problems. Meanwhile, another designer will state that thermal reliefs should always be used on every plane connection. So, who is correct?

Both parties are correct in different situations. In my view, thermal reliefs should always be placed on through-hole connections to plane layers or large polygons.

For SMD pads or via connections back to a plane, and when reflow soldering is being used, it's a different story. If you have SMD pads connecting directly to a polygon on the same layer, and you're soldering by hand, you can certainly benefit from thermal reliefs on the SMD pad as you will not need to crank up the temperature on your iron to compensate heat dissipation. I think the same would apply to vias connecting between a relief-less pad and an internal plane layer. However, if the polygon is small, do you really need the thermal reliefs on SMD pads or vias? I do not think so, especially when reflow soldering is used.

Right Angle Routing

This rule of thumb is probably the one rule everyone loves to hate. To this day, I still see designers stating right-angled traces should never be used under any circumstances. The reasons include the nonsensical, such as electrons can't make a 90-degree turn at a trace corner, yet these same designers ignore 90-degree turns at vias. The reasons are also practical, such as a shorter trace can be routed with two 45-degree turns compared to two 90-degree turns. Other explanations for this rule of thumb state the outside of all 90-degree turns must be chamfered. There is also the issue of acid traps, although this is not a concern with modern alkaline etchants.

Unless you're working at 50 GHz and above (this is only the mmWave radar/5G community at this point), you won't have to worry about right-angle traces. In fact, you could route at any angle you like while still maintaining impedance control throughout the interconnect. This process is extremely easy when your PCB routing tools are integrated with an electromagnetic field solver.

The '3W' Rule(s)

The 3W rule refers to three possible rules:

- A rule for preventing crosstalk

- A rule for sizing traces in sawtooth/accordion length tuning

- A rule for defining spacing between microstrips (or striplines) and copper pour

3W Rule #1: The first version of the 3W rule states the spacing between adjacent traces should be at least 3x the width of the traces. The goal is to minimize magnetic flux between traces. The logic states that minimizing magnetic flux between traces thus minimizes inductive crosstalk.

The incarnations of this rule that I've read seem to ignore the fact that the strength of inductive crosstalk is proportional to the loop inductance of the aggressor and victim trace, which is proportional to the area enclosed by both traces. If the loop inductance and area enclosed by each trace are made smaller, then the traces could be spaced by less than 3W. Just as is the case with orthogonal routing, you should run a basic crosstalk simulation while varying the spacing between your traces. In many designs, you will find that 1.5W or 2W is appropriate down to layer thicknesses of 4-6 mil.

3W Rule #2: The next incarnation of the 3W rule appears in sawtooth routing for length matching. This rule is an upper limit on the size of the sawtooth section, which is intended to minimize impedance discontinuities in these length-matching structures. Read more about this version of the 3W rule in this recent article.

3W Rule #3: Finally, the third incarnation of this rule relates to the spacing between microstrips and nearby copper pour, or between striplines and nearby copper pour. This separation rule states that the spacing between the trace and the copper pour should be at least 3x the width of the trace in order to prevent the nearby pour from modifying the impedance of the copper.

As I discussed in a recent article and showed with some simple simulations, this rule is overly conservative. While following the rule won't necessarily hurt your design or cause a signal integrity problem, you can certainly violate this rule to some extent. The exact extent to which you can violate this rule depends on the trace width to layer thickness spacing, as well as the dielectric constant of the substrate. Take a look at the linked article to see how this can be calculated. If you're not in the mood to calculate the minimum spacing you can set in your striplines or microstrips, you can go with the 3W rule just to be safe.

The ‘20H’ Rule

This rule defines the distance a ground plane should extend beneath a power plane in a PCB. First, you should place a power plane adjacent to its ground plane in a modern PCB to ensure sufficient interplane capacitance and reduce power bus ripple in high-speed boards.

Some experimental studies on this matter present mixed results. According to one study, RF emissions from fringing fields at less than approximately 300 MHz can be reduced by ~5 dBμV/m by following the 20H rule. At higher frequencies corresponding to forced resonances in the ground plane-power plane waveguide structure, the results are quite different. RF emissions are suppressed at some frequencies but increased at other frequencies, regardless of whether the 20H rule is followed. In effect, following the 20H rule simply changes the resonance frequencies, all of which are in the GHz range.

Here's the verdict: if your signal bandwidths are below the GHz range, then you might as well use the 20H rule. Otherwise, there does not appear to be a universal benefit; whether or not the 20H rule will suppress RF emissions from fringing fields depends on the signal bandwidth.

Further Reading on PCB Layout Rules

Take a look at these other articles on PCB design rules:

- Top 5 PCB Design Guidelines Every PCB Designer Needs to Know

- 7 Common Misconceptions about PCB Design

- The Worst Advice We've Ever Heard About PCB Design

No matter which PCB layout rules of thumb or industry standards are important for your design, you can define them as design rules in Altium. The unified design environment in Altium integrates your design data with the routing and layout tools, and your design tools will check your board against your design rules as you build your layout. You'll also have a complete set of tools for running signal integrity simulations and preparing your new product for manufacturing.