Co określić dla integralności kanału: praktyczne listy kontrolne dla łączy wysokiej prędkości

Większość zespołów odkrywa problemy z integralnością kanału dopiero podczas uruchamiania: oko, które w symulacji wyglądało czysto, zamyka się na stanowisku pomiarowym; złącze, które miało parametry wystarczające dla danej szybkości transmisji, zawodzi w rzeczywistej topologii; albo zmiana stackupu powoduje spadek marginesu, którego nikt nie uwzględnił w budżecie. Każdy z tych przypadków jest w istocie błędem specyfikacji, który ujawnia się jako problem z integralnością sygnału (SI). Rozwiązaniem jest zdefiniowanie integralności kanału jako zestawu mierzalnych wymagań odpowiednio wcześnie, tak aby mogły one wpłynąć na architekturę, a następnie weryfikowanie tych wymagań na każdym etapie projektu.

Najważniejsze wnioski

- Integralność kanału to przede wszystkim problem wymagań. Margines zyskujesz albo tracisz poprzez wybory dotyczące topologii, stackupu i połączeń międzyelementowych.

- Retimery, redrivery, złącza i kable zużywają część budżetu kanału. Należy je specyfikować za pomocą parametrów IL, RL, przesłuchów i jitteru, które bezpośrednio wiążą się z marginesem łącza.

- Plan pomiarowy jest częścią specyfikacji kanału. Strategia fixture’ów i de-embedding powinny zostać zdefiniowane, zanim układ ścieżek zostanie zamrożony.

Co naprawdę obejmuje integralność kanału

Kanał wysokiej szybkości obejmuje całą ścieżkę elektryczną od wyprowadzeń nadajnika do wyprowadzeń odbiornika, w tym wyprowadzenia z obudowy, przelotki, przejścia między płaszczyznami odniesienia, ścieżki, złącza, kable oraz wszelkie aktywne układy kondycjonowania sygnału po drodze. Integralność kanału to zdolność tej ścieżki do spełnienia docelowego współczynnika błędów bitowych (BER) w całym zakresie napięcia, temperatury, zmienności procesu oraz rzeczywistych warunków połączeń. Topologia, komponenty i metoda walidacji muszą być wystarczająco dobre, a wyniki muszą być powtarzalne.

Każdy element ścieżki zużywa część budżetu marginesu. Gdy którykolwiek z nich jest niedostatecznie określony, problemy pojawiają się późno, a cykl debugowania staje się kosztowny. W tym artykule przedstawiamy ośmiostopniowy proces, który pomoże Ci zrozumieć, co należy specyfikować, jak to robić i czego wymagać od dostawców komponentów, aby wyniki symulacji i pomiarów laboratoryjnych były zbieżne. Dodatkowo udostępniamy praktyczne checklisty dla każdego etapu tego procesu.

Aby bliżej przyjrzeć się temu, jak PCIe 7.0, 800G Ethernet, USB4 i Wi‑Fi 7 podnoszą te wymagania już na wcześniejszych etapach projektowania, zobacz Standardy wysokich szybkości stale podnoszą poprzeczkę.

Krok 1. Zdefiniuj łącze, które rzeczywiście budujesz

Zacznij od krótkiego bloku definicji łącza, który zostanie uwzględniony zarówno w wymaganiach, jak i w planie testów.

Checklist definicji łącza

- Standard i docelowa szybkość (na przykład: PCIe, Ethernet, USB4 lub własny SerDes).

- Liczba linii i oczekiwania dotyczące ich łączenia.

- Zasięg i topologia. Tylko na płytce, między płytkami, kablowo czy jako flyover.

- Budżet opóźnienia (szczególnie jeśli możesz dodać retimery).

- Ograniczenia mocy i termiczne w prawdopodobnych miejscach kondycjonowania sygnału.

- Ograniczenia środowiskowe i mechaniczne (wibracje, dostęp serwisowy).

Te decyzje tworzą bazę wymagań dla każdego kolejnego wyboru. Ustal je wcześnie i zachowaj w planie testów.

Krok 2. Zbuduj budżet, zanim rozpocznie się layout

Budżet kanału stanowi trzon specyfikacji. Zamienia życzeniowe myślenie w konkretne liczby, które stackup, wybór złączy i plan kondycjonowania sygnału mogą rzeczywiście spełnić.

Pozycje budżetu, które należy uwzględnić

- Tłumienie wtrąceniowe (IL) w funkcji częstotliwości.

- Tłumienie odbiciowe (RL) w funkcji częstotliwości.

- Docelowe wartości przesłuchów: NEXT, FEXT oraz metryki mixed-mode (jeśli ich używasz).

- Budżet skew: w tym wpływ splotu włókna szklanego i złączy.

- Docelowe wartości konwersji modów, ponieważ energia wspólna często objawia się jako EMI.

- Założenia budżetu jitteru oraz to, jak wiele oczekujesz odzyskać dzięki equalizacji.

Jeśli nie potrafisz wyrazić wymagania jako pozycji budżetowej i płaszczyzny odniesienia, nie będziesz w stanie go jednoznacznie zwalidować.

Krok 3. Retimery. Co specyfikować, gdy potrzebujesz CDR

Gdy potrzebujesz odzyskiwania zegara i danych (CDR), retimer zapewnia punkt resetu w kanale. Ponownie transmituje czystą wersję sygnału, przywracając margines, którego sama equalizacja nie jest w stanie odzyskać. Ta zdolność wiąże się z ograniczeniami projektowymi, które trzeba określić z góry.

Checklist specyfikacji retimera

- Obsługiwane szybkości transmisji i protokoły.

- Liczba linii i elastyczność mapowania linii.

- Opóźnienie (typowe i najgorszy przypadek).

- Tolerancja jitteru i charakterystyka jego przenoszenia (w jaki sposób układ filtruje jitter lub go przepuszcza).

- Zachowanie i sterowanie equalizacją: statyczne presety kontra działanie adaptacyjne; sposób konfiguracji i monitorowania.

- Stany zasilania i charakterystyka termiczna.

- Wymagania dotyczące zegara odniesienia, jeśli występują.

- Wymagania ścieżki sygnałowej: oczekiwania dotyczące sprzężenia AC, ograniczenia wyprowadzeń z obudowy i wytyczne routingu.

- Dostępność modeli: IBIS-AMI tam, gdzie ma to znaczenie, a także projekty referencyjne i materiały ewaluacyjne.

Wyróżniony retimer

Broadcom BCM85667 to wykonany w procesie 5 nm, 16-liniowy retimer PCIe Gen 6 i CXL 3.1 pracujący z szybkością 64 GT/s PAM4. Jego opis produktu zawiera informacje o obsługiwanych szybkościach transmisji, opcjach bifurkacji, ustawieniach EQ i zgodności footprintu. Tego poziomu szczegółowości specyfikacji należy oczekiwać od każdego retimera, który kwalifikujesz.

Krok 4. Redrivery. Co specyfikować, gdy chcesz liniowego EQ

Redriver zapewnia liniową equalizację i kondycjonowanie wyjścia. Nie realizuje odzyskiwania zegara. Taki kompromis zwykle oznacza mniejsze opóźnienie i prostszą integrację, ale mniejszą zdolność do przywrócenia mocno zdegradowanego kanału.

Checklist specyfikacji redrivera

- Obsługiwana szybkość transmisji i pasmo.

- Zakres equalizacji i wielkość kroku.

- Zakres amplitudy wyjściowej i sterowanie flat gain.

- Zachowanie pod względem szumu i liniowości, szczególnie jeśli możesz wzmacniać szum razem z sygnałem.

- Czułość wejściowa i obsługa składowej wspólnej.

- Interfejs konfiguracji i telemetria.

- Obudowa i ograniczenia wyprowadzeń.

- Dostępność modeli i wytyczne dotyczące layoutu referencyjnego.

Wyróżniony redriver

Diodes’ PI3EQX32908ZRIEX to 8-kanałowy liniowy redriver PCIe 5.0 obsługujący od 5 do 32 Gb/s z programowalnym EQ dla każdego kanału, regulacją amplitudy wyjściowej i flat gain; obsługuje również protokoły SAS4 i CXL.

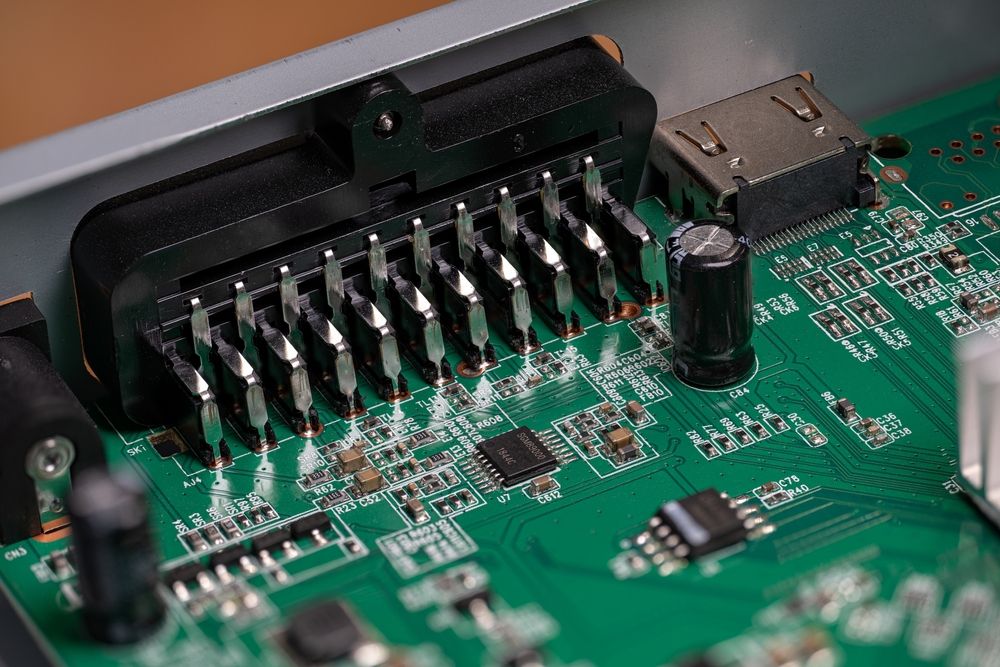

Krok 5. Złącza jako elementy kanału

Przy wysokich szybkościach złącze i jego przejścia mogą zużywać nieproporcjonalnie dużą część marginesu, dlatego zasługują na taką samą rygorystyczną specyfikację jak każdy inny element kanału.

Checklist specyfikacji złącza

- Docelowa impedancja różnicowa i tolerancja.

- IL i RL w funkcji częstotliwości dla sparowanej pary oraz dla przejść PCB.

- Zachowanie pod względem przesłuchów i wytyczne dotyczące izolacji pola pinów.

- Opcje wysokości stacku i tolerancje skumulowane.

- Liczba cykli łączenia i założenia dotyczące trwałości mechanicznej.

- Ograniczenia footprintu PCB i breakoutu.

- Dostępność parametrów S oraz wszelkich wytycznych projektów referencyjnych.

- Plan drugiego źródła na poziomie interfejsu.

Wyróżnione złącza

Molex Mirror Mezz 202828-1506 to hermafrodytyczne złącze mezzanine płytka-płytka z 404 obwodami, wysokością stacku 2,50 mm i montażem BGA, obsługujące szybkości transmisji do 56 Gb/s na parę różnicową. Wykorzystuje footprint zalecany przez OCP, współdzielony w całej rodzinie Mirror Mezz, co zapewnia dane S-parameter, dokumentację footprintu i widoczność u dystrybutorów, które możesz dołączyć do modelu kanału i przeglądu BOM.

Krok 6. Kable i flyovery: specyfikuj rozszerzenie kanału

Miedziane zespoły kablowe i aktywne flyovery optyczne wydłużają zasięg kanału poza to, co mogą zapewnić ścieżki na płytce, ale rozwiązują różne problemy. Kable miedziane zachowują się jak linie transmisyjne z ograniczeniami dotyczącymi impedancji, ekranowania i promienia gięcia. Flyovery optyczne całkowicie omijają straty dielektryczne, ale wprowadzają zagadnienia konwersji elektrooptycznej, zasilania, termiki i opóźnienia. Należy specyfikować takie podejście, jakiego wymaga budżet łącza, oraz zdefiniować, co oznacza równoważna wydajność dla wszelkich rozważanych alternatyw.

Checklist specyfikacji kabla

- Impedancja różnicowa i skew.

- IL i RL w funkcji częstotliwości, w tym przejścia na obu końcach.

- Skuteczność ekranowania i sposób uziemienia.

- Ograniczenia promienia gięcia i odciążenia mechanicznego.

- Wymagania dotyczące liczby cykli łączenia i dostępu serwisowego.

- Zachowanie pasywne lub aktywne, jeśli dotyczy. W przypadku flyoverów optycznych należy określić długość fali, budżet mocy optycznej, opóźnienie i pobór mocy na linię.

- Wymagania kwalifikacyjne i lista zatwierdzonych kabli.

Wyróżniony aktywny zespół flyovera optycznego

Samtec ECUO-B04-14-015-0-2-1-2-01 (FireFly ECUO) to aktywny zespół flyovera optycznego dostępny jako 4-kanałowy transceiver full-duplex 28 Gb/s na kanał albo jako 12-kanałowy nadajnik lub odbiornik 16 Gb/s na kanał. Z włóknem wielomodowym OM3 może osiągać do 100 metrów. Całkowicie omija straty ścieżek PCB i wykorzystuje ten sam system mikrozłączy co miedziane zespoły flyover Samtec, dzięki czemu footprint pozostaje taki sam przy przejściu między optyką a miedzią.

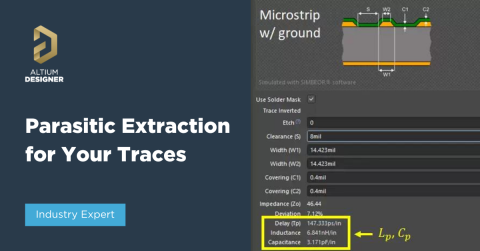

Krok 7. Materiały niskostratne i miedź: uwzględnij stackup w specyfikacji

Łącza o większym paśmie wymagają, aby stackup był kontrolowanym wejściem projektowym. Specyfikacja kanału powinna obejmować docelowe materiały i dopuszczalne zakresy, a także jasno określać założenia dotyczące chropowatości miedzi i możliwości procesu produkcyjnego.

Checklist specyfikacji materiału i stackupu

- Docelowe wartości Dk i Df przy odpowiednich częstotliwościach oraz dopuszczalne odchylenia.

- Założenia dotyczące profilu folii miedzianej, gdy straty przewodnika są czynnikiem ograniczającym.

- Kontrola ryzyka związanego ze splotem włókna szklanego i skew dla długich przebiegów różnicowych.

- Tg, Td i CTE w osi Z, jeśli środowisko pracy lub profil montażu są wymagające.

- Założenia dotyczące możliwości producenta PCB: współczynniki aspektowe wierceń, rejestracja, wypełnianie przelotek i cykle laminacji.

- Zamroź system laminatu i wymagaj jawnego przeglądu przed wprowadzeniem jakichkolwiek zamienników.

Wyróżnione laminaty niskostratne

MEGTRON 7 firmy Panasonic oraz I-Tera MT40 firmy Isola to reprezentatywne rodziny laminatów o ultraniskich i bardzo niskich stratach, stosowane w szybkich kanałach cyfrowych. Traktuj te produkty jako punkty odniesienia przy określaniu wymagań wobec dowolnego wybranego laminatu: stabilne dane elektryczne, wytyczne procesowe oraz jednoznaczna identyfikacja produktu, którą można jednoznacznie wskazać w uwagach produkcyjnych.

Krok 8. Plan pomiarów. Celem ma być korelacja

Twój plan pomiarów musi obejmować zdefiniowane płaszczyzny odniesienia, przyrządy pomiarowe, kalibrację oraz de-embedding, aby można było bez niejasności porównywać wyniki symulacji z danymi z pomiarów laboratoryjnych. IEEE 370-2020 stanowi praktyczny punkt odniesienia dla tych działań, obejmując jakość danych, kwestie związane z oprzyrządowaniem oraz de-embedding na potrzeby charakteryzacji PCB i połączeń wzajemnych do 50 GHz.

Lista kontrolna planu pomiarów

- Co będziesz mierzyć: TDR dla profilu impedancji, parametry S z VNA dla segmentów połączeń oraz diagram oka lub jitter w określonych punktach.

- Gdzie będziesz mierzyć: Zdefiniuj płaszczyzny odniesienia i nadaj im nazwy.

- Jak będziesz kalibrować: Określ metodę kalibracji i jej identyfikowalność.

- Jak będziesz wykonywać de-embedding: Wybierz metody, które możesz zrealizować przy użyciu swojego oprzyrządowania i narzędzi.

- Jak będziesz prowadzić korelację: Zdefiniuj kryteria akceptacji dla zgodności między symulacją a pomiarem.

Wyróżniona platforma pomiarowa

Analizatory sieci Keysight PNA-X obejmują zakresy częstotliwości od 900 Hz do 67 GHz (zależnie od modelu), oferują wiele wewnętrznych źródeł, odbiorniki parametrów S i szumów oraz kompatybilność z oprogramowaniem PLTS firmy Keysight do charakteryzacji połączeń wzajemnych i de-embeddingu.

Gdzie Octopart wpisuje się w ten workflow

Elementy związane z integralnością kanału często mają mniej rzeczywistych zamienników. Rodziny złączy, specjalistyczne układy scalone do kondycjonowania sygnału oraz niektóre zespoły kablowe mogą stać się elementami, które opóźniają realizację projektu. Używaj Octopart oraz narzędzia BOM Tool, aby utrzymać powiązanie trzech kwestii, gdy projekt jest jeszcze wystarczająco elastyczny:

- Numer części i aktualny status cyklu życia.

- Materiały pomocnicze: karty katalogowe, modele i projekty referencyjne.

- Produkty alternatywne i opcje dostawców, zanim footprinty i interfejsy zostaną ostatecznie ustalone.

Im wcześniej powiążesz rzeczywiste dane komponentów z modelem kanału, tym mniej założeń przetrwa do etapu layoutu. Plik parametrów S złącza, nota produktowa retimera albo tabela Dk/Df laminatu są warte więcej niż placeholder i plan doprecyzowania wszystkiego później. Octopart daje jedno wygodne miejsce do sprawdzenia dostępności, pobrania kart katalogowych i potwierdzenia statusu cyklu życia, gdy projekt jest jeszcze na tyle elastyczny, by uwzględnić to, co znajdziesz.

Dyscyplina, która zapobiega kolejnym rewizjom

Integralność kanału buduje się poprzez zestaw decyzji podejmowanych na etapie architektury, stackupu i doboru połączeń wzajemnych, a następnie weryfikuje za pomocą symulacji, pomiarów i korelacji przed oraz po wykonaniu layoutu. Wspólny mianownik wszystkich tych działań jest ten sam: określ, czego potrzebujesz, zapisz to liczbowo, wybieraj komponenty poparte danymi potwierdzającymi te wartości i przygotuj plan pomiarów, zanim layout zostanie zamknięty. Zespoły, które robią to konsekwentnie, to te, które unikają kolejnej rewizji projektu.