Podstawy analizy integralności sygnału na obwodzie drukowanym

Podstawy analizy integralności sygnału PCB to o wiele więcej niż tylko podstawowe informacje. Narzędzia do symulacji integralności sygnałów świetnie sprawdzają się w obliczaniu zachowania sygnałów w różnych sieciach podczas projektowania schematu i układu, ale potrzebna jest pewna wiedza, aby zinterpretować wyniki. Choć niektóre narzędzia do symulacji integralności sygnału i symulacji pól elektromagnetycznych (EM) mogą być bardzo rozbudowane, to i tak nie mogą się równać z informacjami, które można uzyskać z pomiarów. Bez względu na to, która metoda zostanie użyta do zbadania integralności sygnału na płytce (warto wykorzystać obie), trzeba wykonać kilka ważnych kroków, aby przeanalizować zachowanie sygnałów i zidentyfikować problemy na płytce.

Wprowadzenie do analizy integralności sygnału

Analiza integralności sygnału rozpoczyna się od symulacji na etapie pre-layout. Po zbudowaniu układu można skorzystać z kilku ważnych symulacji post-layout, aby przeanalizować integralność sygnału zależną od geometrii na płytce. W pewnym momencie trzeba będzie porównać wyniki symulacji integralności sygnału z rzeczywistymi pomiarami, warto więc zachować wyniki do porównania.

Analizy pre-layout

Ta część dotyczy tak naprawdę projektowania obwodów, wyboru komponentów i sprawdzania, w jaki sposób sygnały przemieszczają się między we/wy na dwóch komponentach. Istnieją trzy ważne analizy, które dostarczą najważniejszych informacji na temat zachowania projektowanego obwodu.

-

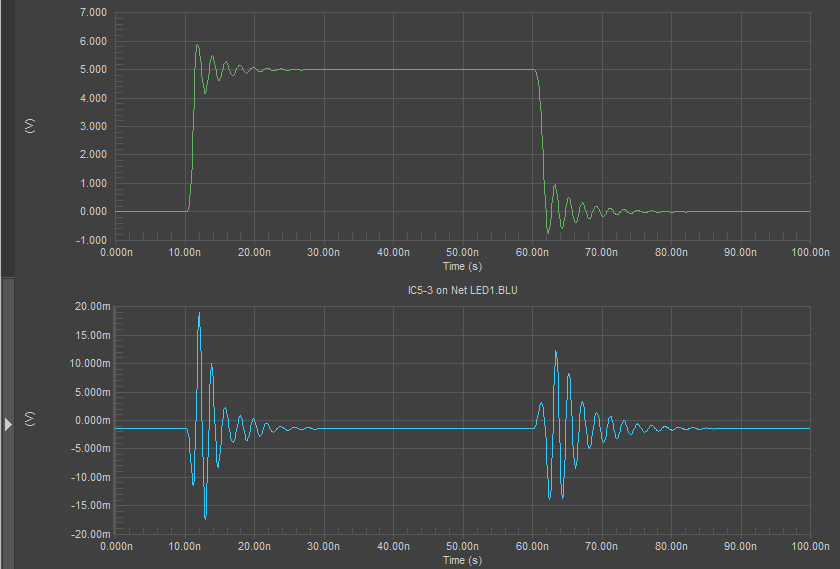

Zachowania nieustalone. Reakcje nieustalone w połączeniu między dwoma buforami można również modelować w dziedzinie czasu za pomocą analizy stanów nieustalonych. Można również określić zachowanie stanów nieustalonych na podstawie analizy zerowania biegunów. To pokaże przeregulowanie/niedoregulowanie ze względu na dzwonienie i zbliżenie się do zamierzonego poziomu sygnału. Najdokładniejsze wersje tych symulacji z układami scalonymi obejmują modele IBIS, chociaż podukłady SPICE mogą być używane do modelowania buforów we/wy.

-

Parametry S i funkcja przenoszenia. Niektóre bloki funkcjonalne na płytce mogą być modelowane jako sieci wieloportowe, co oznacza, że ich liniowe zachowanie można opisać za pomocą parametrów S przy określonej częstotliwości. Można określić parametry S na podstawie współczynnika odbicia w domenie czasowej, który w liniach transmisyjnych obejmuje impedancję wejściową określoną przez pojemność obciążenia. Można obliczyć funkcję transferu dla danej sieci na podstawie parametrów S i odwrotnie. Tutaj prezentujemy doskonały przewodnik, który pokazuje całą związaną z tym matematykę.

-

Charakterystyka impulsowa. Symulacja ta obejmuje dwa cele: kwalifikację modeli parametrów S / funkcji przenoszenia pod kątem przyczynowości w określonej samodzielnie szerokości pasma oraz zbadanie charakterystyki impulsowej dla określonego czasu narastania. Charakterystyka impulsowa umożliwia również wyodrębnienie delty dyspersji i propagacji w projekcie połączeń. Kwalifikuje to planowany model kanału dla danej pary buforów wejścia/wyjścia w idealnej sytuacji, zanim zostanie przygotowany układ PCB.

-

Wykres oczkowy. Modele buforów i projekt połączeń mogą być wykorzystane do symulacji wykresu oczkowego. Wykres oczkowy jest ważną częścią zgodności kanału, ponieważ pokazuje oczekiwany poziom sygnału, przeregulowanie, interferencję międzysymbolową (ISI), jitter i oczekiwaną bitową stopę błędów w pseudolosowej sekwencji bitów.

W bardziej złożonych kanałach powyższy zestaw analiz pre-layout może pomóc w zakwalifikowaniu takich aspektów jak zaplanowane przejścia.

Jeżeli struktura każdego z tych elementów jest znana przed utworzeniem projektu, można

Analizy post-layout

Ta część dotyczy sprawdzenia, w jakim zakresie elementy pasożytnicze na płytce wpływają na integralność sygnału. Ponieważ efekty pasożytnicze integralności sygnału są funkcją geometrii płytki, należy przeanalizować następujące problemy integralności sygnału zależne od geometrii:

-

Przesłuch. Przesłuchy, będące zmorą wielu projektantów, wynikają ze sprzężenia indukcyjnego i pojemnościowego. Jeśli badasz wpływ przesłuchu na jednej ścieżki na drugą, sprzężenie pojemnościowe wystąpi tylko wówczas, gdy obie ścieżki będą ze sobą sąsiadować. Przesłuch indukcyjny nie jest ograniczony zasięgiem, a wszystkie ścieżki na płytce mogą łączyć się ze sobą poprzez pole magnetyczne.

-

Zachowanie linii przesyłowej. Chociaż można użyć modeli linii transmisyjnych do zbadania ścieżek sygnałowych podczas fazy pre-layout, najlepiej jest to zrobić bezpośrednio z poziomu układu. Jeśli linie nie mają kontroli impedancji, należy sprawdzić, czy odbicia na linii (o ile występują) obniżają poziom sygnału w odbiorniku i prowadzą do reakcji schodkowej z sygnałami cyfrowymi. W przypadku sygnałów analogowych może to być bardziej skomplikowane, ponieważ szukamy interferencji i powstawania fal stojących na linii. Jednak odpowiedni symulator integralności sygnału może oddzielić fale padające i odbite, co umożliwia zbadanie zachowania każdej z nich z osobna. Następnie można określić poziom odbicia i sprawdzić, czy poziom sygnału spełnia wymagania dotyczące sygnalizacji.

-

Wszystko, co zostało zbadane na etapie pre-layout! Chodzi o to, aby sprawdzić, czy efekty pasożytnicze, splot skrętki itp. nie zmieniają znacząco zachowania sygnałów na płytce. Jeśli wiele ścieżek spowoduje niepożądane zachowania, układ trzeba będzie zmodyfikować. Pierwszym miejscem, od którego należy zacząć, jest stackup i geometria ścieżek.

Narzędzia do analizy integralności sygnału

Powyższe punkty mogą sprawiać wrażenie, że do zbudowania i uruchomienia narzędzi do analizy integralności sygnału niezbędny będzie złożony program symulacyjny. Potrzebne narzędzia będą zależeć od tego, co zamierzamy symulować i oceniać. W Twoim narzędziu EDA niektóre z tych symulacji są po prostu wykonywane za pomocą programu podobnego do IBIS, a bardziej złożone symulacje z wieloma siatkami mogą wymagać solvera pola 3D lub porównywalnego narzędzia solvera 2D.

Magistrale single-ended bez specyfikacji impedancji

W wolniejszych magistralach single-ended bez terminacji można zaobserwować pewne przejściowe zachowanie (dzwonienie), które może być spowodowane strukturą połączenia (jego pojemnością i indukcyjnością). Można to zaobserwować w SPI, gdy ścieżka jest elektrycznie krótka. W tych magistralach możliwe jest zaobserwowanie dzwonienia na etapie pre-layout, o ile model linii transmisyjnej został zastosowany na schematach i o ile specyfikacja pinów jest zdefiniowana (podukład SPICE lub model IBIS).

Gdy magistrala single-ended jest faktycznie poprowadzona, można przeprowadzić symulację na etapie post-layout za pomocą analizatora integralności sygnału w narzędziach EDA. Analizatory te mogą wykorzystywać przypisanie rodziny logicznej lub model IBIS dla odpowiednich pinów/sieci w celu symulacji:

- Przebiegów przesłuchu i identyfikacji silnych regionów sprzężenia

- Kształtu fal odbiciowych

- Innych wskaźników zachowania sygnału (czas narastania/opadania, przeregulowanie/niedoregulowanie itp.)

- Obliczania średniej impedancji dla całej ścieżki.

W magistralach single-ended bez specyfikacji impedancji możliwe jest zaobserwowanie odbić na końcu sterownika, gdy magistrala staje się długa, lub dzwonienia z powodu pojemności i indukcyjności magistrali. Jeśli dzwonienie powoduje nadmierne przeregulowanie, to zmniejszenie indukcyjności ścieżki i dodanie tłumienia stanowią dwie główne drogi prowadzące do zmniejszenia amplitudy dzwonienia. Innym sposobem jest zwiększenie tłumienia poprzez dodanie rezystora szeregowego, co można zrobić w przypadku wyjścia bufora o niskiej impedancji do dłuższej niedopasowanej linii transmisyjnej.

Magistrale z kontrolą impedancji

W magistralach single-ended i magistralach różnicowych z kontrolą impedancji impedancja końcowa może znajdować się na matrycy, więc symulacja oparta na rodzinie logicznej na etapie post-layout nie jest skuteczna, ponieważ nie opisuje poprawnie impedancji magistrali. Przesłuch można nadal symulować, ponieważ obejmuje on tylko sprzężenie między dwoma połączeniami w funkcji czasu narastania, a wielkość przesłuchu będzie odwrotnie skalować się odpowiednio do czasu narastania, nawet jeśli zostanie przypisana tylko rodzina logiczna.

W przypadku symulacji na etapie post-layout pod kątem odbić i naruszeń impedancji symulacja w tym przypadku powinna przynajmniej wykorzystywać modele IBIS do definiowania zachowania bufora, a nie polegać na opisach rodziny układów logicznych. O ile opis bufora jest znany i dostępny, można go zastosować do modelowania zachowania komponentu w edytorze PCB. Standardowe narzędzie integralności sygnału w edytorze PCB dla przesłuchów i kształtu fal odbiciowych może pomóc w wielu wstępnych kwalifikacjach zachowania sygnału (czas narastania/opadania, przeregulowanie, przesłuch, spójna impedancja i dzwonienie) przed przejściem do bardziej zaawansowanego narzędzia analitycznego.

Aby symulować takie elementy, jak wykres oczkowy, przesłuchy wielu sieci i odchylenia impedancji wzdłuż długości siatki, istnieją dodatkowe narzędzia, których można użyć. Jedną z opcji są solvery polowe, a dostępnych jest wiele takich narzędzi o różnych poziomach specjalizacji. Takie narzędzie jak pełnofalowy solver pola nie zawsze jest konieczne, chyba że planujemy symulowanie emisji promieniowanych, coś głębszego z SI/PI lub wyodrębnianie parametrów S w symulowanej sieci.

Zaawansowane narzędzia do projektowania i analizy PCB w programie Altium Designer® zapewniają użyteczny punkt wyjścia do analizy integralności sygnału za pomocą narzędzi do symulacji integralności sygnału na etapie pre-layout i post-layout. Te dokładne obliczenia dają podstawę do porównania pomiarów. Umożliwiają również dostęp do pełnego zestawu funkcji planowania produkcji i dokumentacji na jednej platformie.

Teraz możesz pobrać bezpłatną wersję próbną oprogramowania Altium Designer i dowiedzieć się więcej o najlepszej w branży symulacji układu, integralności sygnału i narzędziach do planowania produkcji. Aby dowiedzieć się więcej o programie Altium Designer, porozmawiaj z ekspertem Altium już dziś.