Jak zapobiegać typowym problemom z integralnością sygnałów

Czy robisz wszystko, co możliwe, aby rozwiązać problemy związane z integralnością sygnału w projektach high-speed design? Przeczytaj, jak zapobiegać najbardziej typowym problemom z integralnością sygnału dzięki rozwiązaniom w zakresie stosu i prowadzenia ścieżek w systemie Altium Designer®.

Projektom o wysokiej wydajności towarzyszy ich specyficzny zestaw wyzwań w świecie projektowania układów elektronicznych.

Narodziny High-Speed Design

Wzrost liczby projektów z sygnałami o wysokiej częstotliwości jest ściśle związany ze stałym wzrostem wydajności układów elektronicznych na przestrzeni lat. W miarę wzrostu wydajności układów spiętrzają się wyzwania dotyczące płytek PCB. Matryce są coraz mniejsze, zagęszczenie podzespołów na płytkach jest coraz większe i stale poszukujemy chipów, które zapewnią najmniejsze możliwe zużycie energii. Ze względu na te wszystkie gwałtowne postępy technologiczne znaleźliśmy się w samym jądrze projektowania high-speed design wraz z całą jego złożonością i wszystkimi problemami.

Spojrzenie wstecz dla uzyskania perspektywy

W ciągu ostatnich 30 lat wiele się zmieniło w projektowaniu PCB. W 1987 myśleliśmy, że technologia 0,5 mikrona była szczytem możliwości, a dziś technologia 22 nm zdaje się nam być „przerośnięta”. Szybkości zboczy w 1985, które przyczyniały się do komplikowania projektów (zazwyczaj 30 ns), bledną w zestawieniu ze współczesnymi szybkościami (1 ns), co widać na ilustracji poniżej:

Szybkości zboczy zmieniły się w ciągu ostatnich 30 lat

Postęp nękany problemami

Postęp nie przebiega bezproblemowo. Wraz ze zwiększeniem wydajności układów oraz przyjęciem praktyk projektowania high-speed design napotkaliśmy szereg kwestii, z którymi trzeba sobie poradzić w środowisku projektowym. Zestawmy te wyzwania:

Jakość sygnału

Decyzja producentów o obniżeniu podstawowych napięć i zwiększeniu częstotliwości pracy spowodowała gwałtowne zwiększenie szybkości zboczy. Te szybkości mogą powodować odbicia oraz problemy z jakością sygnału w projektach, jeśli pozostaną nierozwiązane.

Przesłuch

W projektach high-speed design o gęsto upakowanych ścieżkach często dochodzi do przesłuchu. Jest to zjawisko związane z niezamierzonym sprzężeniem częstotliwości fal elektromagnetycznych między ścieżkami na płytce drukowanej.

Do przesłuchu może dochodzić między ścieżkami sąsiadującymi ze sobą krawędziami (sprzężenie krawędziowe) na tej samej warstwie lub między płaszczyznami ścieżek na sąsiadujących warstwach (sprzężenie burtowe). Sprzężenie jest trójwymiarowe. Ścieżki, których krawędzie lub płaszczyzny są równolegle do ścieżek sąsiadujących, powodują większe przesłuchy niż ścieżki poprowadzone obok siebie.

Sprzężenie burtowe (góra) w porównaniu do sprzężenia krawędziowego (dół)

Emisje promieniowania

Większe szybkości zboczy w zastanych projektach, które wykorzystują tę samą częstotliwość i długość ścieżek co przedtem, powodują dzwonienie w niezakończonej linii długiej. To prowadzi do drastycznie większych emisji promieniowania, które znacznie przekraczają limity Klasy B normy FCC/CISPR dla niezakończonych linii długich.

Emisje promieniowania przy szybkości zbocza 10 ns (lewa strona) oraz 1 ns (prawa strona)

Rozwiązania projektowe

Ponieważ problemy dotyczące integralności sygnału i zasilania zwykle objawiają jako przerywane działanie, mogą być trudne do zdiagnozowania. Zawsze lepiej jest wykryć te problemy na etapie projektowania i wyeliminować je u źródeł, zamiast próbować rozwiązać je później, co może spowodować opóźnienie produkcji. Dzięki narzędziu do planowania stosu możemy znacznie łatwiej wdrożyć rozwiązania w zakresie integralności sygnału w naszych projektach.

Planowanie stosu warstw płytki

Absolutnie pierwszą sprawą, którą trzeba się zająć przy projektowaniu high-speed design, jest stos warstw płytki. Substrat stanowi najbardziej krytyczny komponent zespołu i trzeba starannie zaplanować jego specyfikacje, aby nie dopuścić do nieciągłości impedancji, sprzężenia sygnałów i nadmiernych emisji promieniowania. Przygotowując stos warstw płytki, trzeba uwzględnić następujące wskazówki i zalecenia:

- Wszystkie warstwy sygnałowe powinny przylegać i być blisko sprzężone z nieprzerwaną płaszczyzną odniesienia, co pozwala zapewnić jasną ścieżką powrotną i wyeliminować przesłuch burtowy.

Substrat ze wszystkimi warstwami sygnałowymi sąsiadującymi z płaszczyzną odniesienia

- Płaszczyzna musi mieć dobrą pojemność, żeby zredukować impedancję AC przy wysokich częstotliwościach. Blisko sprzężone płaszczyzny redukują impedancję AC w górnym zakresie i drastycznie obniżają poziom promieniowania elektromagnetycznego.

- Sygnały o dużej prędkości należy prowadzić pomiędzy płaszczyznami, żeby zmniejszyć promieniowanie.

- Zmniejszenie wysokości dielektryka spowoduje duże obniżenie przesłuchu bez negatywnego wpływu na dostępną przestrzeń na płytce.

- Substrat powinien umożliwiać korzystanie z szeregu różnych technologii. Przykładowo: impedancja 50/100 omów dla sygnałów cyfrowych, impedancja 40/80 omów dla DDR4, impedancja 90 omów dla USB.

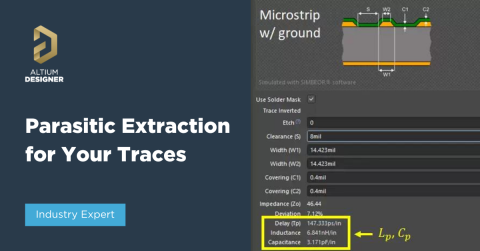

Prowadzenie ścieżek i przepływy pracy

Po starannym zaplanowaniu stosu warstw czas przejść do prowadzenia ścieżek na płytce. Po dokładnym skonfigurowaniu reguł projektowych i przestrzeni roboczej jesteśmy dobrze przygotowani do pomyślnego poprowadzenia ścieżek w jak najbardziej wydajny sposób. Skorzystaj z tych wskazówek, żeby łatwiej poprowadzić ścieżki, jednocześnie unikając zbędnych przesłuchów, promieniowania oraz problemów z jakością sygnału:

- Uprość widok, aby dobrze widzieć podzielone płaszczyzny i ścieżki powrotne prądu. W tym celu określ, które płaszczyzny miedzi (masa albo zasilanie) stanowią odniesienie dla poszczególnych warstw sygnałowych. Następnie włącz warstwę sygnałową i warstwę płaszczyzny, aby widzieć je jednocześnie. Dzięki temu będziesz dobrze widzieć ścieżku przecinające podzielone płaszczyzny.

Wiele warstw sygnałowych (lewa strona) w porównaniu do widoku górnej warstwy i sąsiadującej płaszczyzny (prawa strona)

- Jeśli sygnały cyfrowe muszą przebiegać przez przerwę w płaszczyźnie odniesienia integralności zasilania, można w ich pobliżu umieścić jeden lub dwa płaskie kondensatory odsprzęgające (100 nF). To zapewni ścieżkę dla prądu powrotnego między dwoma doprowadzeniami.

- Unikaj prowadzenia ścieżek, których krawędzie lub płaszczyzny są równolegle do ścieżek sąsiadujących, ponieważ powodują one większe przesłuchy niż ścieżki poprowadzone obok siebie.

- Równoległe odcinki ścieżek powinny być jak najkrótsze, aby zmniejszyć przesłuch, chyba że zostanie zastosowana magistrala synchroniczna Zachowaj odpowiednie odległości między grupami sygnałów: odległość między ścieżkami sygnałów adresowych i danych musi być trzy razy większa niż szerokość ścieżki.

- Zachowaj ostrożność, stosując warstwy mikropaskowe na górze i na spodzie płytki. Mogą one być przyczyną przesłuchu powodowanego przez ścieżki poprowadzone na sąsiadujących warstwach, co może zagrażać integralności sygnału.

- Zawsze prowadź ścieżkę zegara (lub strobu) odpowiednio do największego opóźnienia w grupie sygnałów. To pozwoli na ustalenie się danych zanim zostaną odczytane przez zegar.

- Prowadzenie ścieżek sygnałów zagnieżdżonych między płaszczyznami pomoże zminimalizować emisje promieniowania, a także zapewni ochronę elektrostatyczną.

Czystość sygnału

Poziom skomplikowania projektów elektronicznych bez wątpienia zwiększy się w przyszłości, stawiając przed projektantami PCB nowe wyzwania i problemy do rozwiązania. Prawidłowe skonfigurowanie stosu, impedancji i ścieżek powrotnych zapewnia stabilną podstawę dla projektu. Trzeba pochwalić nowe funkcje do projektowania high-speed design w systemie Altium Designer, takie jak xSignals®, za umożliwienie bardziej precyzyjnego wdrażania dopasowania krytycznych sygnałów dzięki weryfikacji za pomocą solvera elektromagnetycznego 2D.

Z jakich narzędzi korzystasz do projektów high-speed design? Sprawdź Altium

Odsyłacz: Beyond Design: Signal Integrity 1-3, PCB Design Magazine