O que especificar para a integridade de canal: checklists práticos para links de alta velocidade

A maioria das equipes descobre problemas de integridade de canal na fase de bring-up: um diagrama de olho que parecia limpo na simulação se fecha na bancada, um conector que era especificado para a taxa de dados falha na topologia real, ou uma mudança no stackup propaga uma perda de margem que ninguém havia previsto. Cada um desses casos é uma falha de especificação que se manifesta como uma falha de integridade de sinal (SI). A correção é definir a integridade de canal como um conjunto de requisitos mensuráveis cedo o suficiente para influenciar a arquitetura e, então, verificar esses requisitos em todas as fases do projeto.

Principais conclusões

- A integridade de canal é, antes de tudo, um problema de requisitos. Você ganha ou perde margem com as escolhas de topologia, stackup e interconexão.

- Retimers, redrivers, conectores e cabos consomem, cada um, parte do orçamento do canal. Especifique-os com números de IL, RL, diafonia e jitter que se relacionem diretamente à margem do seu link.

- Um plano de medição faz parte da especificação do canal. A estratégia de fixture e o de-embedding devem ser definidos antes que o layout seja congelado.

O que a integridade de canal realmente abrange

Um canal de alta velocidade engloba todo o caminho elétrico, dos pinos do transmissor aos pinos do receptor, incluindo breakouts de encapsulamento, vias, transições de plano de referência, trilhas, conectores, cabos e qualquer condicionamento ativo ao longo do percurso. Integridade de canal é a capacidade desse caminho de atender a uma taxa de erro de bit (BER) alvo em diferentes condições de tensão, temperatura, variação de processo e condições reais de interconexão. Sua topologia, componentes e método de validação precisam se sustentar, e os resultados precisam ser reproduzíveis.

Cada elemento no caminho consome parte do orçamento de margem. Quando qualquer um deles é subespecificado, os problemas aparecem tarde, e o ciclo de depuração fica caro. Neste artigo, apresentamos um processo de oito etapas para ajudar você a entender o que especificar, como especificar e o que exigir dos fornecedores de componentes para que seus resultados de simulação e de laboratório convirjam. Além disso, estamos fornecendo checklists práticos para cada etapa do processo.

Para uma análise mais detalhada de como PCIe 7.0, Ethernet 800G, USB4 e Wi-Fi 7 estão elevando esses requisitos a montante, veja Os padrões de alta velocidade continuam elevando o nível.

Etapa 1. Defina o link que você está realmente construindo

Comece com um bloco curto de definição do link incluído nos seus requisitos e no seu plano de testes.

Checklist de definição do link

- Padrão e meta de velocidade (exemplo: PCIe, Ethernet, USB4 ou um SerDes proprietário).

- Contagem de lanes e expectativas de lane bonding.

- Alcance e topologia. Apenas on-board, placa a placa, cabeado ou flyover.

- Orçamento de latência (especialmente se você puder adicionar retimers).

- Restrições de potência e térmicas nos prováveis pontos de condicionamento.

- Restrições ambientais e mecânicas (vibração, acesso para manutenção).

Essas decisões formam a linha de base de requisitos para cada escolha posterior. Defina-as cedo e mantenha-as no seu plano de testes.

Etapa 2. Monte um orçamento antes do início do layout

Um orçamento de canal é a espinha dorsal da especificação. Ele transforma expectativas otimistas em números concretos que seu stackup, suas escolhas de conectores e seu plano de condicionamento podem realmente atender.

Itens do orçamento a incluir

- Perda por inserção (IL) em função da frequência.

- Perda de retorno (RL) em função da frequência.

- Metas de diafonia: NEXT, FEXT e métricas de modo misto (se você as utilizar).

- Orçamento de skew: incluindo contribuições da trama de fibra de vidro e dos conectores.

- Metas de conversão de modo porque energia em modo comum frequentemente aparece como EMI.

- Premissas de orçamento de jitter e quanto você espera recuperar com equalização.

Se você não consegue expressar um requisito como uma linha de orçamento e um plano de referência, não conseguirá validá-lo de forma limpa.

Etapa 3. Retimers. O que especificar quando você precisa de CDR

Quando você precisa de recuperação de clock e dados (CDR), um retimer fornece um ponto de reinicialização no canal. Ele retransmite uma versão limpa do sinal, restaurando margem que a equalização sozinha não consegue recuperar. Essa capacidade vem com restrições de projeto que você precisa especificar desde o início.

Checklist de especificação de retimer

- Taxas de dados e protocolos suportados.

- Contagem de lanes e flexibilidade de mapeamento de lanes.

- Latência (típica e de pior caso).

- Tolerância a jitter e comportamento de transferência de jitter (como o dispositivo filtra ou deixa passar jitter).

- Comportamento e controles de equalização: presets estáticos versus comportamento adaptativo; como você o configura e monitora.

- Estados de potência e características térmicas.

- Requisitos de clock de referência, se houver.

- Requisitos do caminho de sinal: expectativas de acoplamento AC, restrições de escape do encapsulamento e orientações de roteamento.

- Disponibilidade de modelos: IBIS-AMI quando relevante, além de projetos de referência e material de avaliação.

Retimer em destaque

Broadcom BCM85667 é um retimer PCIe Gen 6 e CXL 3.1 de 16 lanes, em 5 nm, operando a 64 GT/s PAM4. Seu resumo do produto documenta taxas de dados suportadas, opções de bifurcação, controles de EQ e compatibilidade de footprint. Esse é o nível de detalhe de especificação que você deve esperar de qualquer retimer que qualificar.

Etapa 4. Redrivers. O que especificar quando você quer EQ linear

Um redriver fornece equalização linear e condicionamento de saída. Ele não faz recuperação de clock. Essa troca normalmente significa menor latência e integração mais simples, com menor capacidade de recuperar um canal seriamente degradado.

Checklist de especificação de redriver

- Taxa de dados e largura de banda suportadas.

- Faixa de equalização e tamanho dos passos.

- Faixa de swing de saída e controles de ganho plano.

- Comportamento de ruído e linearidade, especialmente se houver possibilidade de amplificar ruído junto com o sinal.

- Sensibilidade de entrada e tratamento de modo comum.

- Interface de configuração e telemetria.

- Encapsulamento e restrições de escape.

- Disponibilidade de modelos e orientações de layout de referência.

Redriver em destaque

PI3EQX32908ZRIEX da Diodes é um redriver linear PCIe 5.0 de 8 canais, com suporte de 5 a 32 Gbps, com EQ programável por canal, swing de saída e controles de ganho plano; ele também oferece suporte aos protocolos SAS4 e CXL.

Etapa 5. Conectores como componentes do canal

Em altas velocidades, o conector e suas transições para a PCB podem consumir uma parcela desproporcional da margem, por isso merecem o mesmo rigor de especificação que qualquer outro componente do canal.

Checklist de especificação de conectores

- Meta de impedância diferencial e tolerância.

- IL e RL em função da frequência para o par acoplado e para as transições na PCB.

- Comportamento de diafonia e orientações de isolamento no campo de pinos.

- Opções de altura de empilhamento e tolerâncias acumuladas.

- Ciclos de acoplamento e premissas de durabilidade mecânica.

- Footprint de PCB e restrições de breakout.

- Disponibilidade de parâmetros S e qualquer orientação de projeto de referência.

- Plano de segunda fonte no nível da interface.

Conectores em destaque

Molex Mirror Mezz 202828-1506 é um conector mezzanine placa a placa hermafrodita com 404 circuitos, altura de empilhamento de 2,50 mm e montagem BGA, suportando taxas de dados de até 56 Gbps por par diferencial. Ele usa um footprint recomendado pela OCP compartilhado em toda a família Mirror Mezz, o que oferece dados de parâmetros S, documentação de footprint e visibilidade junto a distribuidores que você pode anexar ao seu modelo de canal e à revisão da BOM.

Etapa 6. Cabos e flyovers: especifique a extensão do canal

Conjuntos de cabos de cobre e flyovers ópticos ativos ampliam o alcance do canal além do que as trilhas on-board conseguem oferecer, mas resolvem problemas diferentes. Cabos de cobre se comportam como linhas de transmissão com restrições de impedância, blindagem e raio de curvatura. Flyovers ópticos eliminam completamente a perda dielétrica, mas introduzem considerações de conversão eletro-óptica, potência, térmicas e de latência. Especifique a abordagem exigida pelo orçamento do seu link e defina o que significa desempenho equivalente para quaisquer alternativas consideradas.

Checklist de especificação de cabos

- Impedância diferencial e skew.

- IL e RL em função da frequência, incluindo transições em cada extremidade.

- Eficácia da blindagem e abordagem de aterramento.

- Restrições de raio de curvatura e alívio de tensão.

- Requisitos de ciclos de acoplamento e acesso para manutenção.

- Comportamento passivo versus ativo, se aplicável. Para flyovers ópticos, especifique comprimento de onda, orçamento de potência óptica, latência e consumo de potência por lane.

- Requisitos de qualificação e lista de cabos aprovados.

Conjunto de flyover óptico ativo em destaque

Samtec ECUO-B04-14-015-0-2-1-2-01 (o FireFly ECUO) é um conjunto de flyover óptico ativo disponível como transceptor full-duplex de 4 canais a 28 Gbps por canal, ou como transmissor ou receptor de 12 canais a 16 Gbps por canal. Com fibra multimodo OM3, eles podem alcançar até 100 metros. Ele contorna completamente a perda em trilhas de PCB e usa o mesmo sistema de microconector que os conjuntos de flyover de cobre da Samtec, de modo que o footprint permanece o mesmo se você alternar entre óptico e cobre.

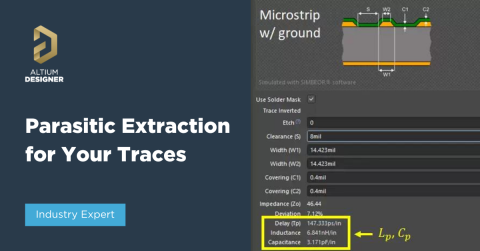

Etapa 7. Materiais de baixa perda e cobre: coloque o stackup na especificação

Links de maior largura de banda exigem que o stackup seja uma entrada de projeto controlada. Sua especificação de canal deve incluir metas de material e faixas aceitáveis, e deve indicar claramente o que você está assumindo sobre rugosidade do cobre e capacidade do processo.

Checklist de especificação de material e stackup

- Metas de Dk e Df nas frequências relevantes, além da variação permitida.

- Premissas sobre o perfil da folha de cobre quando a perda no condutor for o fator limitante.

- Controles de risco de trama de fibra de vidro e skew para trechos diferenciais longos.

- Tg, Td e CTE no eixo Z se o seu ambiente ou perfil de montagem for exigente.

- Premissas sobre a capacidade do fabricante: razões de aspecto de furação, registro, preenchimento de vias e ciclos de laminação.

- Defina o sistema de laminado e exija revisão explícita antes de qualquer substituição.

Laminados de baixa perda em destaque

As famílias de laminados Panasonic MEGTRON 7 e Isola’s I-Tera MT40 são exemplos representativos de materiais ultra-low-loss e very-low-loss usados em canais digitais de alta velocidade. Use esses produtos como referências para definir o que você espera de qualquer laminado selecionado: dados elétricos estáveis, orientação de processamento e uma identidade de produto clara que possa ser fixada nas notas de fabricação.

Etapa 8. Plano de Medição. Faça da Correlação o Objetivo

Seu plano de medição precisa de planos de referência definidos, fixtures, calibração e de-embedding, para que você possa comparar os resultados da simulação com os dados de bancada sem ambiguidades. IEEE 370-2020 é uma referência prática para esse trabalho, cobrindo qualidade dos dados, considerações sobre fixtures e de-embedding para caracterização de PCBs e interconexões até 50 GHz.

Checklist do Plano de Medição

- O que você vai medir: TDR para perfil de impedância, parâmetros S de VNA para segmentos de interconexão e diagrama de olho ou jitter em pontos definidos.

- Onde você vai medir: Defina os planos de referência e nomeie-os.

- Como você vai calibrar: Indique o método de calibração e a rastreabilidade.

- Como você vai fazer o de-embedding: Escolha métodos que você consiga executar com seus fixtures e ferramentas.

- Como você vai correlacionar: Defina critérios de aceitação para o alinhamento entre simulação e medição.

Plataforma de Medição em Destaque

Analisadores de Rede Keysight PNA-X cobrem faixas de frequência de 900 Hz até 67 GHz (dependendo do modelo), com múltiplas fontes internas, receptores de parâmetros S e ruído, e compatibilidade com o software PLTS da Keysight para caracterização de interconexões e de-embedding.

Onde o Octopart se Encaixa no Fluxo de Trabalho

Componentes de integridade de canal frequentemente têm menos alternativas reais. Famílias de conectores, ICs especializados de condicionamento e certos conjuntos de cabos podem se tornar os itens que atrasam uma montagem. Use o Octopart e a BOM Tool para manter três coisas conectadas enquanto o projeto ainda está flexível:

- O número da peça e o status de ciclo de vida atualizado.

- A documentação de suporte: datasheets, modelos e projetos de referência.

- Produtos alternativos e opções de fornecedores antes que footprints e interfaces sejam definidos de forma rígida.

Quanto mais cedo você vincular dados reais de componentes ao seu modelo de canal, menos suposições sobreviverão até o layout. Um arquivo de parâmetros S de conector, um resumo técnico de produto de retimer ou uma tabela de Dk/Df de laminado vale mais do que um placeholder e um plano de finalizar tudo depois. O Octopart oferece um local conveniente para verificar disponibilidade, obter datasheets e confirmar o status do ciclo de vida enquanto o projeto ainda é flexível o suficiente para absorver o que você encontrar.

A Disciplina que Evita Re-Spins

A integridade de canal é construída por meio de um conjunto de decisões tomadas durante a arquitetura, o stackup e a seleção de interconexões, e depois verificada por simulação, medição e correlação antes e depois do layout. O fio condutor em tudo isso é o mesmo: defina o que você precisa, especifique isso em números, escolha componentes que venham com dados para sustentar esses números e escreva o plano de medição antes que o layout seja congelado. As equipes que fazem isso de forma consistente são as que evitam uma nova revisão da placa.