Cálculo de Resistor de Terminação em Série

Com linhas de transmissão, algumas coisas nunca parecem ser simples. Determinar a técnica de terminação e os valores dos componentes em uma rede de terminação não deveria ser uma tarefa difícil. A maioria dos programas de design de PCBs obriga você a procurar calculadoras online, ou você terá que realizar os cálculos manualmente. Em vez disso, seu software de design deveria facilitar o teste de uma gama de valores de componentes na sua rede de terminação.

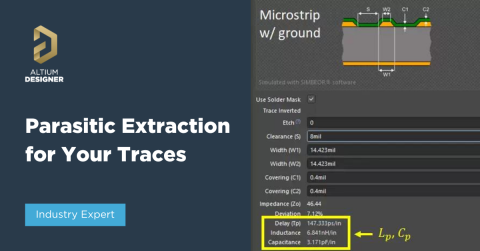

Alguns componentes, trilhas, pares diferenciais e interconexões que passam por vias devem ser compatibilizados em impedância para evitar que efeitos de linha de transmissão surjam em circuitos de alta velocidade ou alta frequência. Embora seja possível lidar com pequenas incompatibilidades de impedância, alguns drivers de sinal terão uma impedância que não corresponde ao valor padrão de 50 Ohms, tipicamente usado com trilhas de sinal. Deve-se notar que alguns padrões de roteamento e arquitetura de computadores (ou seja, PCIe Gen 2 e Gen 3) também usam um valor diferente para a impedância de pares diferenciais.

Se você determinou que sua trilha começará a exibir efeitos de linha de transmissão. Neste artigo, mostrarei como usar as ferramentas de integridade de sinal no Altium Designer® para determinar o valor correto para um resistor em série.

Qual Rede de Terminação Devo Usar?

Existem várias respostas para esta questão, pois existem várias redes possíveis ou terminadores. Para sinais digitais, preferimos a terminação resistiva porque os resistores são componentes de banda larga. Eles podem ser usados para terminar drivers até larguras de banda muito altas quando colocados diretamente no pino do driver de um CI. Em contraste, uma saída RF ou uma antena preferiria uma rede LC porque não queremos ter perda de potência resistiva, e a colocação exata do indutor e do capacitor (seja em série ou como um elemento shunt) depende de como você precisa alterar a impedância para corresponder à frequência de ressonância.

Quanto à terminação resistiva, os dois métodos comuns usados são a terminação em série (colocada no pino do driver) e a terminação paralela (colocada no receptor para GND). Há duas coisas importantes a lembrar sobre os efeitos da terminação em série:

|

Algumas razões para usar resistência de terminação em série no driver incluem:

- Se a linha for longa o suficiente que você esteja esperando reflexões de uma carga não terminada, é necessário entre um driver não terminado e o traço, e a impedância do driver de sinal é menor do que a impedância do seu traço

- Você quer aumentar o amortecimento visto na saída para ajudar a suprimir o salto de terra,NEXT, SSN, ou oscilação em uma linha muito curta

- Se o sinal produzido pelo driver precisa ser desacelerado, o que pode ser usado em uma interface rápida instanciada em um FPGA ou quando os sinais produzidos são sinais de controle que não fornecem um fluxo de dados contínuo

No ponto #1, você pode colocar um resistor em série na saída do seu driver, mas isso é muito incomum, a menos que um barramento digital unipolar padrão (como SPI) seja roteado por uma distância muito longa e tenha um tempo de subida baixo. O ponto #1 também pode ser usado no caso em que componentes especializados de RF são usados, e esses componentes não possuem terminação no próprio chip. O ponto #2 é mais comum, especialmente quando o sinal é fornecido por um processador moderno como um MCU, FPGA, ou MPU.

Se você determinou que precisa de terminação em série, como baseado em um cálculo de comprimento crítico, o pacote de resistores deve ser o menor pacote possível que você planeja montar na placa e é mais simples colocá-lo exatamente no pino de saída do driver. Para determinar a resistência em série, você precisa saber a impedância da fonte já existente, ou precisa ter um modelo de simulação para o buffer de saída do driver (como IBIS). Se você conhece a impedância de saída da fonte, então o requisito de impedância de terminação em série é:

Aqui está como fazer isso em simulação se você conhece a família lógica ou se você tem um modelo IBIS para o pino de saída do driver.

Determinando a Resistência de Terminação em Série

O método comum para determinar a resistência de terminação em série a partir da simulação é iterar através de uma gama de valores de resistores em série. Uma vez que você executa o simulador, você verá um gráfico que mostra como cada valor de componente na rede afeta seu sinal. Isso permite que você determine visualmente os melhores valores de componentes para usar em sua rede de terminação.

- Saiba mais sobre como a terminação em série afeta os níveis de tensão

O processo abaixo aplica-se tanto a sinais diferenciais quanto a sinais de extremidade única que não fazem parte de uma interface padronizada. Lembre-se, um sinal diferencial pode ser tratado como dois sinais de extremidade única separados, cada um com impedância de modo ímpar definida, então o método de terminação em série mostrado abaixo aplica-se a um traço em um par diferencial, desde que você considere o pequeno desvio entre a impedância de modo ímpar e a impedância de extremidade única.

Configuração da Ferramenta de Integridade de Sinal

Uma vez que você capture seu esquemático e organize sua placa, você está pronto para determinar o resistor de terminação apropriado para seus traços. Uma vez que sua placa esteja preparada, você pode acessar a ferramenta de integridade de sinal no Altium Designer a partir do menu Ferramentas -> Integridade de Sinal…

Acessando a ferramenta de Integridade de Sinal no Altium Designer

A ferramenta de Integridade de Sinal precisa ser configurada selecionando a família lógica para os pinos no driver e receptor, ou adicionando modelos IBIS ao componente. Você também pode modificar o estímulo de sinal sendo usado no diálogo de Integridade de Sinal.

|

Uma vez que você tenha aberto a ferramenta de Integridade de Sinal, você deve ver o diálogo de Integridade de Sinal mostrado na imagem abaixo. Aqui, você precisará selecionar quais redes de sinal deseja examinar. Você pode clicar duas vezes nas redes de sinal que deseja examinar, e estas serão adicionadas à tabela no lado direito do diálogo.

Escolhendo redes e redes de terminação para sua simulação de integridade de sinal

Você também verá uma lista de redes de terminação. No exemplo que segue, vamos examinar dois traços de extremidade única (NC1 e NC2). Note que você pode mudar o número de varreduras, bem como os parâmetros na rede de terminação. Você também poderia examinar um dos pares diferenciais (ou seja, NC3_P e NC3_N) usando os mesmos passos apresentados aqui.

Resultados de Extremidade Única

Vamos analisar uma rede de terminação em série, bem como a rede de terminação "Resistência Paralela & Capacitor para GND". Note que você pode escolher os valores máximos e mínimos para sua varredura, assim como sua tensão VCC.

Aqui, você pode modificar os valores dos resistores de terminação na sua rede de correspondência

Agora que você configurou a simulação, clique no botão “Formas de Onda de Reflexão…” para iniciar a simulação. O Altium Designer iterará através dos vários valores de resistores e gerará uma série de gráficos. Os resultados para as redes NC1 e NC2 são mostrados na figura abaixo.

Resultados de reflexão de sinal para várias redes de correspondência

A partir dos resultados acima, podemos ver que o resistor de correspondência em série (dois primeiros gráficos) e a combinação de resistores para VCC e terra na verdade não são as melhores escolhas para esta placa. Ambos os resultados ajudam a reduzir um pouco o ringing, mas também precisamos compensar o tempo de subida lento. Portanto, devemos tentar uma rede diferente e repetir o processo.

Aqui, podemos voltar e escolher a rede "Resistor & Capacitor Paralelos ao GND" e verificar como essa rede afeta os sinais nas malhas NC1 e NC2. Os resultados para esta rede são mostrados abaixo. Para ver os valores de cada componente na rede, basta clicar em um dos rótulos na legenda no lado direito do gráfico. Nesta placa, verifica-se que a rede de traços ótima usa um resistor de 56,67 Ohms e um capacitor de 83,33 pF (o sinal vermelho no gráfico inferior).

Resultados da reflexão de sinal para a rede resistor/capacitor

Processo para um Par Diferencial

Para examinar um par diferencial, você pode voltar ao diálogo de Integridade de Sinal e examinar cada traço no par diferencial. Se considerarmos a fórmula de terminação em série mostrada acima, temos que lembrar que a impedância diferencial é definida em termos de sua impedância de modo ímpar; essa é o valor usado para a terminação do resistor em série. Como a impedância característica de um traço em um par diferencial é sempre maior que a impedância de modo ímpar, podemos escrever a seguinte relação:

Com base nessa variação, o valor do resistor em série necessário para um traço em um par diferencial será ligeiramente menor do que o valor da resistência em série determinado pela ferramenta de integridade de sinal:

Avançando com o Roteamento Controlado por Impedância

Sem dúvida, sua melhor opção é usar roteamento controlado por impedância para que você possa garantir que seus traços terão valores de impedância consistentes em toda a sua placa. Idealmente, isso ajudará a evitar a necessidade de aplicar uma rede de terminação a cada traço em sua placa, economizando uma quantidade significativa de tempo de design.

Determinar a rede de terminação correta a ser usada em seu PCB é muito mais fácil quando você trabalha com um pacote de design de PCB que inclui ferramentas de design e simulação de energia. Com Altium Designer, você terá controle total sobre a disposição e o design de suas camadas, e suas ferramentas de simulação tomarão dados diretamente do seu layout. Essas ferramentas são diretamente adaptáveis a sistemas rígido-flexíveis e de múltiplas placas.

Baixe uma versão de avaliação gratuita do Altium Designer para ver como as poderosas ferramentas de integridade de sinal podem ajudá-lo. Você terá acesso às melhores funcionalidades de design que a indústria exige em um único programa. Fale hoje com um especialista da Altium para saber mais.