Como Fazer: Correspondência de Impedância e Terminação de Cargas Capacitivas

A correspondência de impedância e a terminação de carga capacitiva são examinadas neste artigo.

Para aqueles de vocês que prestam atenção nos canais do Youtube da Altium, sabem que a integridade de sinal é um tópico quente e gera muitas perguntas. Recentemente, recebi uma pergunta interessante de um espectador que perguntou sobre a terminação de cargas capacitivas:

Vejo que há muitos vídeos excelentes sobre correspondência de impedância e design da largura de trilhas para combinar com qualquer impedância de cabo entrante, mas e sobre combinar com cargas capacitivas?

Os MOSFETs de geração atual e os GaN HEMTs são capazes de comutação sub 100 ns neste momento e, por isso, sinto que a correspondência com o gate de um dispositivo de potência vai se tornar um problema muito maior no futuro…

Como explicarei abaixo, a ideia de uma carga puramente capacitiva é algo de uma falácia. Sim, os capacitores existem, mas todos os capacitores são não ideais, e é esse desvio de uma capacitância teórica que determina como fazer a correspondência de impedância de uma carga que exibe comportamento capacitivo. Vamos dar uma olhada neste aspecto importante do design de interconexão e ver o que realmente significa terminar uma carga capacitiva.

O Que é uma Carga Capacitiva?

Muito simplesmente, cargas puramente capacitivas não existem. Mesmo bancos de capacitores não são verdadeiramente "capacitivas", pelo menos sob a perspectiva de potência reativa. Em eletrônica, e especificamente em PCBs, uma carga que parece ser capacitiva só o será em uma certa faixa de frequência, e a capacitância pode não surgir devido a capacitores colocados intencionalmente.

Em vez disso, em eletrônica, quando dizemos que uma carga é capacitiva, estamos provavelmente nos referindo à impedância de um componente, ou especificamente à sua impedância de entrada. Uma impedância de entrada capacitiva geralmente diminui com o aumento da frequência e faz com que a corrente lidere a tensão em fase. Alguns exemplos incluem:

- Circuitos RC ou alguns circuitos RLC

- I/Os em circuitos integrados

- O terminal de gate em MOSFETs

- Stubs em linhas de transmissão, dependendo do seu comprimento e terminação

- Redes de casamento de impedância

Em outras palavras, o elemento é aproximado como um capacitor, mesmo que não aja exatamente como tal. Com isso em mente, vamos explorar dois casos principais onde a impedância capacitiva e a terminação são consideradas: sinais analógicos de banda estreita e sinais digitais de banda larga.

Sinais Analógicos

Se você está trabalhando apenas em uma frequência específica, ou em uma faixa muito estreita de frequências, então você vai querer usar um circuito de filtro LC padrão. Especificamente, um grupo de dois capacitores ou um filtro L normalmente será usado para determinar que a parte real da impedância de carga deve ser maior que zero. Isso reflete o fato de que, para uma carga real, ela não será puramente capacitiva.

Para combinar completamente a impedância de um interconexão inteira, você deve usar o seguinte processo:

- Determinar o circuito de filtro LC necessário para ajustar a impedância equivalente (carga + filtro) à impedância alvo. Isso é facilmente feito com uma transformação série/paralela e resolvendo os valores de L e C.

- Calcular a impedância de entrada para sua linha de transmissão particular como vista na extremidade de entrada usando a fórmula padrão.

- Ajustar a impedância da fonte para corresponder à impedância de entrada calculada no Passo 2.

As diferentes impedâncias usadas para uma carga capacitiva são mostradas abaixo. Tipicamente, a rede de casamento será uma rede L-match ou um par de capacitores/indutores em uma disposição pi com a carga. O projetista pode escolher a funcionalidade de passa-alta ou passa-baixa na rede de casamento e aplicar análise de circuito para obter Zeq.

O Passo 1 é fundamental na análise de circuitos, então eu não vou mostrar uma explicação completa aqui, provavelmente cobrirei isso em outro artigo. Você pode encontrar um ótimo tutorial neste link (começando na Página 3). No Passo 2, a impedância (equivalente) alvo que você calculou no Passo 1 se torna a carga usada no cálculo da impedância de entrada no Passo 2. Finalmente, no Passo 3, você pode precisar aplicar uma rede de casamento adicional para casar a impedância da fonte com a impedância de entrada (linha + filtro).

Casamento com a Impedância de Entrada da Linha de Transmissão

Mencionei acima que a fonte pode precisar ser ajustada à entrada. O que quero dizer é, se a linha for um pouco mais longa que o limite para uma linha eletricamente curta e houver algum desajuste residual, a impedância de entrada (linha + filtro) pode ser bastante diferente da impedância característica da linha de transmissão. Portanto, você precisa ajustar a impedância de saída da fonte para corresponder à impedância de entrada da linha na frequência requerida. Isso é feito com outra rede de casamento (veja abaixo). Isso pode ser tão simples quanto um resistor em série, embora em circuitos reativos com uma linha de transmissão às vezes faça sentido também usar um circuito LC para o casamento de impedâncias na frequência requerida.

Você pode estar pensando: por que posso usar apenas indutores e capacitores para casar com uma carga capacitiva arbitrária se eu preciso ter uma impedância de carga real? A verdade é que a impedância de carga terá uma parte real muito pequena. Mesmo para componentes impressos ou impedâncias arbitrárias, o circuito de carga sempre terá alguma resistência parasita em algum lugar do circuito. Isso surgirá nos terminais dos componentes, trilhas do PCB e qualquer outra estrutura no layout do PCB usada para fazer uma conexão.

Linhas Curtas

Se a linha de transmissão for curta, então as coisas são muito mais fáceis. Neste caso, você não precisa da rede de Correspondência de Entrada mostrada acima. Com uma linha curta, a impedância da fonte Zs vê apenas a carga, então você pode usar a impedância da fonte como seu alvo de impedância ao projetar o bloco de circuito de Correspondência de Saída. Em circuitos RF, isso não é o que você normalmente vê, há propagação para outro bloco de circuito (cabo, transmissor, etc.), então haverá alguma desvio de impedância de entrada a considerar.

Circuitos Lógicos de Alta Velocidade

Não sempre mencionamos isso ao discutir circuitos lógicos de alta velocidade, mas as entradas para circuitos lógicos CMOS têm alguma capacitância que é determinada pelas dimensões do transistor e da embalagem do receptor. Todos os circuitos lógicos baseados em transistor são capacitivos, assim como os traços que são usados para guiar o sinal até as entradas. O traço e a embalagem juntos têm alguma capacitância parasita que precisa ser carregada para que o sinal propagado seja interpretado como o estado lógico desejado.

A diferença entre uma linha de transmissão e uma carga capacitiva é que uma linha de transmissão é realmente um circuito LC agrupado (na verdade, um circuito RLC) com constante dielétrica complexa. Portanto, sua impedância é aproximadamente real. No entanto, a capacitância da carga cria efeitos reais; os valores típicos de capacitância de carga podem variar de 1 pF a 100 pF para componentes digitais modernos, dependendo da embalagem e do nó tecnológico. A capacitância da carga está em paralelo com um circuito lógico de alta impedância (ordem de 1 MOhm), então juntos eles agem como um circuito RC uma vez que recebem a onda entrante. Portanto, só nos preocupamos em aplicar terminação como se tudo fosse feito de resistores; só nos importamos com frequências até os limites onde a capacitância da carga prevalece.

Claramente, esta é uma carga "capacitiva". Em circuitos digitais, reconhecemos que a capacitância da carga é um fator limitante de largura de banda; isso só se torna importante quando você entra nas altas frequências de GHz, o que significa que só nos importamos quando a faixa de frequência de corte para essa impedância de entrada se sobrepõe com uma fração significativa da largura de banda do sinal digital. Não é prático aplicar terminação de banda larga nesses circuitos para suprimir completamente as reflexões. Sempre haverá alguma reflexão que ocorre quando o sinal em trânsito atinge a carga.

Portanto, a indústria tem se concentrado em coisas como equalização e esquemas de sinalização multinível para recuperar sinais e aumentar as taxas de dados para um dado tempo de subida. Em qualquer caso, o elemento de terminação pode estar presente no die do componente, a menos que uma lógica especial esteja sendo usada. Um exemplo com terminação paralela é mostrado abaixo.

Uma alternativa aqui é o uso de terminação RC no receptor, mas isso é menos comum e exigiria um par externo de componentes. A ideia aqui é desacelerar o tempo de subida, que normalmente seria limitado pela construção do dispositivo no die (normalmente uma entrada de alta impedância). A terminação RC geralmente não é preferida para esse propósito, pois é melhor desacelerar o sinal no driver em vez de no receptor. No entanto, você pode não ter escolha em alguns casos, por exemplo, quando o driver não está localizado em sua PCB e você só tem a opção de colocar uma terminação RC no receptor.

A conclusão é esta: para circuitos integrados digitais, não nos preocupamos necessariamente com terminação capacitiva porque estamos tentando combinar a impedância ao longo da maior largura de banda possível em vez de em uma frequência específica. Isso coloca a maior ênfase no design do canal físico para garantir que as perdas de retorno sejam mínimas em canais curtos e que as perdas de inserção sejam mínimas em canais longos. Se nos preocupássemos apenas em combinar em uma frequência específica, poderíamos perder a maior parte da potência do sinal e ele poderia ser completamente perdido.

Resumo

Apenas para resumir, aqui estão alguns pontos importantes:

- Não existe uma carga puramente capacitiva. Até mesmo capacitores deixam de agir como capacitores ideais em frequências suficientemente altas. Cargas reais podem se comportar de maneira aproximadamente capacitiva.

- Sinais analógicos podem ser combinados de impedância a uma carga capacitiva com um circuito padrão de filtro LC.

- Em circuitos digitais, não podemos realmente terminar a capacitância de carga devido à natureza de banda larga dos sinais digitais.

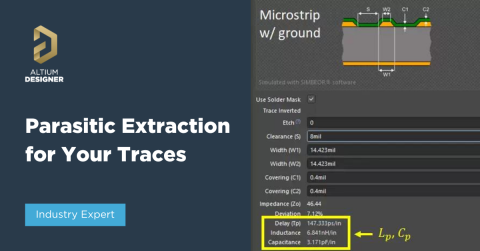

Uma vez que você determinou os requisitos de conversão de modo de par diferencial, você pode criar sua geometria de par diferencial e regras de roteamento usando os melhores recursos de layout de PCB da indústria no Altium Designer. O Layer Stack Manager integrado inclui um solucionador de campo ultra-preciso para cálculos de impedância em geometrias padrão, e você pode instantaneamente impor os resultados como uma regra de design em suas ferramentas de roteamento. Quando você terminar seu design e quiser liberar os arquivos para seu fabricante, a plataforma Altium 365™ facilita a colaboração e o compartilhamento de seus projetos.

Apenas começamos a explorar o que é possível com o Altium Designer no Altium 365. Inicie seu teste gratuito do Altium Designer + Altium 365 hoje mesmo.