Os Fundamentos da Análise de Integridade de Sinal em Sua PCB

Os fundamentos da análise de integridade de sinal em sua PCB podem ser tudo, menos básicos. Ferramentas de simulação de integridade de sinal são excelentes para calcular o comportamento dos sinais em diferentes redes durante o projeto esquemático e de layout, mas você ainda precisará tomar algumas medidas para interpretar os resultados. Por mais avançadas que algumas ferramentas de simulação de integridade de sinal e EM possam ser, elas simplesmente não se comparam às informações que você pode obter a partir de medições. Independentemente do método que você usar para examinar a integridade do sinal em sua placa (você deve fazer ambos), existem alguns passos importantes que você pode tomar para analisar o comportamento dos seus sinais e identificar problemas em sua placa.

Iniciando a Análise de Integridade de Sinal

A análise de integridade de sinal começa com simulações na fase de pré-layout. Uma vez que você construa seu layout, você pode usar algumas simulações pós-layout importantes para analisar a integridade de sinal dependente da geometria em sua placa. Em algum momento, você precisará comparar seus resultados de simulação de integrididade de sinal com medições reais, então mantenha seus resultados à mão para comparação.

Análises de Pré-Layout

Esta parte é realmente sobre o projeto de circuitos, seleção de componentes e análise de como os sinais viajam entre os I/Os em dois componentes. Existem três análises importantes que fornecem uma quantidade significativa de informações sobre o comportamento da sua placa.

-

Comportamento transitório. As respostas transitórias na conexão entre dois buffers também podem ser modeladas no domínio do tempo usando análise transitória, ou você pode determinar o comportamento dos transientes a partir da análise de polo-zero. Isso mostrará a você o overshoot/undershoot devido ao ringing e a abordagem ao nível de sinal pretendido. As versões mais precisas dessas simulações com circuitos integrados envolvem modelos IBIS, embora subcircuitos SPICE possam ser usados para modelar buffers I/O.

-

Parâmetros-S e função de transferência. Blocos funcionais específicos na sua placa podem ser modelados como redes multiportas, o que significa que seu comportamento linear pode ser descrito em termos de parâmetros-S em uma frequência específica. Você pode determinar os parâmetros-S a partir de um coeficiente de reflexão no domínio do tempo, o que, em linhas de transmissão, envolve a impedância de entrada dada pela capacitância de carga. Você pode calcular a função de transferência para sua rede a partir dos parâmetros-S, e vice-versa. Aqui está um excelente guia que mostra toda a matemática envolvida.

-

Resposta ao impulso. Esta simulação envolve dois objetivos: qualificar modelos de parâmetros S/função de transferência quanto à causalidade na sua largura de banda definida e examinar o comportamento da resposta ao pulso para um tempo de subida definido. As respostas ao impulso também permitem extrair dispersão e atraso de propagação ao longo do seu projeto de interconexão. Isso qualifica um modelo de canal pretendido para um dado par de buffer de entrada/saída em uma situação ideal antes de você projetar a PCB.

-

Diagrama de olho. Modelos de buffer e o projeto de interconexão podem ser usados para simular um diagrama de olho. O diagrama de olho é uma parte importante da conformidade do canal, pois mostrará o nível de sinal esperado, overshoot, interferência entre símbolos (ISI), jitter e taxa de erro de bit esperada sob uma sequência de bits pseudorrandômica.

Em canais mais complexos, o conjunto acima de análises pré-layout pode ajudá-lo a qualificar coisas como transições de via planejadas,

Contanto que você conheça a estrutura de cada um desses elementos antes de criar o design, você pode

Análises Pós-Layout

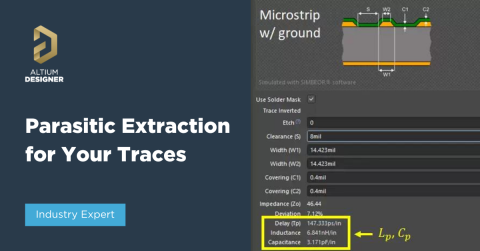

Esta parte é realmente sobre examinar como os parasitas na sua placa afetam a integridade do sinal. Como os efeitos de integridade de sinal parasitários são funções da geometria da placa, você precisará examinar os seguintes problemas de integridade de sinal dependentes de geometria:

-

Diafonia.O flagelo de muitos designers, o crosstalk surge de acoplamentos indutivos e capacitivos. Se você está examinando os efeitos do crosstalk em uma trilha vítima e outra agressora, o acoplamento capacitivo só ocorrerá quando as duas estiverem adjacentes. O crosstalk indutivo não é limitado por alcance, e todas as trilhas em sua placa podem se acoplar entre si através do campo magnético.

-

Comportamento da linha de transmissão. Embora você possa usar modelos de linha de transmissão para examinar trilhas de sinal durante a fase de pré-layout, é melhor fazer isso diretamente a partir do seu layout. Se suas linhas não forem controladas por impedância, então você precisará examinar se reflexões na linha (se houver) degradam os níveis de sinal no receptor e levam a uma resposta em degraus com sinais digitais. Com sinais analógicos, isso pode ser mais complicado, pois você está procurando por interferências e formação de ondas estacionárias na linha. No entanto, o simulador de integridade de sinal correto pode separar as ondas incidentes e refletidas, permitindo que você examine o comportamento de cada uma individualmente. Você pode então determinar o nível de reflexão e ver se o nível de sinal atende aos seus requisitos de sinalização.

-

Tudo o que você examinou antes do layout! O ponto aqui é verificar se parasitas, tecido de fibra, etc., não alteram drasticamente o comportamento dos sinais na sua placa. Se múltiplos traços estão falhando, então seu layout precisará ser modificado. O primeiro lugar para começar é com seu empilhamento e geometria de traço.

Ferramentas para Análise de Integridade de Sinal

Os pontos acima podem parecer como se você precisasse de um programa simulador complexo para construir e executar essas ferramentas de análise de integridade de sinal. As ferramentas exatas de que você precisará dependerão do que você deseja simular e avaliar. Dentro da sua ferramenta EDA, algumas dessas simulações são simplesmente feitas com algo como IBIS, enquanto simulações mais complexas com múltiplas redes podem requerer um solucionador de campo 3D ou uma ferramenta solucionadora 2D comparável.

Barramentos de Terminação Única Sem Especificação de Impedância

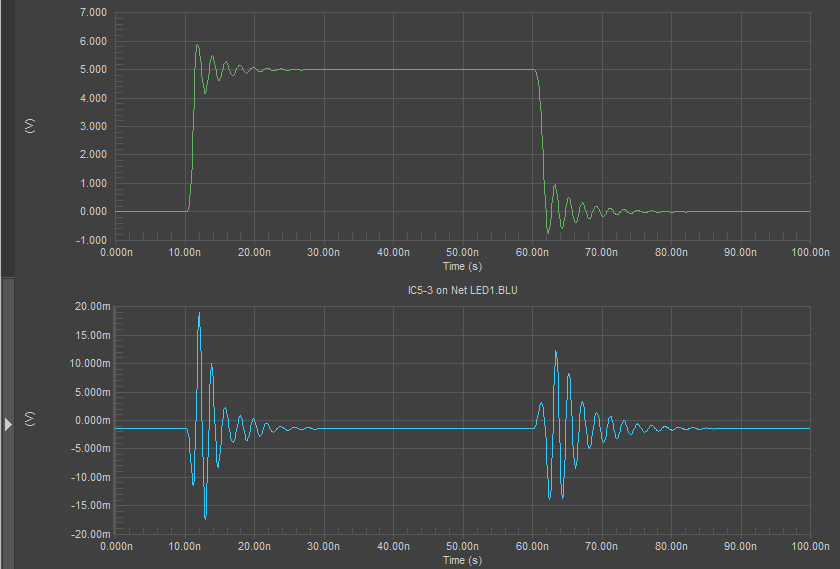

Em barramentos de extremidade única mais lentos sem terminação, é possível observar algum comportamento transitório (ressonância) que pode ser devido à estrutura da interconexão (sua capacitância e indutância). Isso é algo que pode ser observado no SPI quando o traço é eletricamente curto. Nesses barramentos, é possível observar a ressonância antes do layout, desde que você tenha um modelo de linha de transmissão aplicado em seus esquemáticos e desde que a especificação do pino esteja definida (seja subcircuito SPICE ou modelo IBIS).

Quando o barramento de extremidade única é efetivamente roteado, você pode executar uma simulação pós-layout com o analisador de integridade de sinal em suas ferramentas de EDA. Esses analisadores podem usar ou uma atribuição de família lógica ou um modelo IBIS para os pinos/redes relevantes para simular:

- Formas de onda de diafonia e para identificar regiões de acoplamento forte

- Formas de onda de reflexão

- Outras métricas de comportamento de sinal (tempo de subida/queda, overshoot/undershoot, etc.)

- Calcular a impedância média ao longo do comprimento da trilha

Em barramentos de terminação única sem uma especificação de impedância, é possível observar reflexões na extremidade do driver quando o barramento se torna longo, ou ringing devido à capacitância e indutância no barramento. Se o ringing produzir overshoot excessivo, então reduzir a indutância da trilha e adicionar amortecimento são os dois principais caminhos a seguir para reduzir a amplitude do ringing. A outra é aumentar o amortecimento por adicionar um resistor em série, algo que você faria com uma saída de buffer de baixa impedância em uma linha de transmissão desadaptada mais longa.

Barramentos Controlados por Impedância

Em barramentos de terminação única e diferencial controlados por impedância, a impedância de terminação pode estar no próprio chip, então uma simulação baseada em família lógica em pós-layout não é eficaz, pois não descreve corretamente a impedância do barramento. A diafonia ainda pode ser simulada porque você está apenas olhando para o acoplamento entre dois interconectores como uma função do tempo de subida, e a magnitude da diafonia vai escalar inversamente com o tempo de subida de acordo, mesmo que você só atribua uma família lógica.

No caso de uma simulação pós-layout para reflexões e violações de impedância, uma simulação neste caso deve pelo menos usar modelos IBIS para definir o comportamento do buffer em vez de depender de descrições de famílias lógicas. Contanto que a descrição do buffer seja conhecida e disponível, ela pode ser aplicada para modelar o comportamento do componente no Editor de PCB. A ferramenta padrão de integridade de sinal em um editor de PCB para crosstalk e formas de onda de reflexão pode ajudar com muita qualificação prévia do comportamento do sinal (tempo de subida/queda, overshoot, crosstalk, impedância consistente e ringing) antes de passar para uma ferramenta de análise mais avançada.

Para simular coisas como diagramas de olho, crosstalk multi-net e desvios de impedância ao longo do comprimento de uma rede, existem ferramentas externas que podem ser usadas. Solucionadores de campo são uma opção, e há muitas dessas ferramentas disponíveis com diferentes níveis de especialização. Algo como um solucionador de campo de onda completa nem sempre é necessário, a menos que você queira simular emissões irradiadas, algo mais profundo com SI/PI, ou extrair parâmetros S na rede simulada.

As poderosas ferramentas de design e análise de PCB em Altium Designer® oferecem um ponto de partida útil para a análise de integridade de sinal com ferramentas de simulação de integridade de sinal pré-layout e pós-layout. Esses cálculos precisos fornecem uma base para comparar suas medições. Você também terá acesso a um conjunto completo de recursos de planejamento de fabricação e documentação em uma única plataforma.

Agora você pode baixar uma versão de avaliação gratuita do Altium Designer e aprender mais sobre as melhores ferramentas de layout, simulação de integridade de sinal e planejamento de produção do setor. Fale com um especialista da Altium hoje para saber mais sobre o Altium Designer.