接地反弹减少技术可最大限度地减少信号完整性问题

与我父亲学生时代在篮球队中生龙活虎不同,我在试训时几乎无法将球拍起。不言而喻,一切还没开始便已结束。在成为NBA职业球员的梦想破灭后,我发现了自己对武术的热情。我从来没有真正掌握篮球技术,但在武术中,至少我可以用脚掌弹跳起来迎击对手。

不会拍球无足轻重。然而,不了解电子设备中的接地反弹可能会给您的电路带来很大的难题。要成为一名出色的PCB布局工程师,了解接地反弹对电路和信号完整性的影响很有必要。通过考虑接地反弹降低技术,您可以最大限度地减少设计中PCB信号完整性中的接地反弹。

什么是接地反弹?

要了解接地反弹,您需要深入了解构成集成电路(IC)核心的休眠晶体管和接地引脚方面的基础知识。下图显示的是CMOS缓冲电路,该电路构成了微控制器和随机存取存储器(RAM)等IC中的典型I/O。

PCB中的接地反弹噪声是一个难以测量的问题,它对电源门控和信号完整性的影响与PCB中的迹线阻抗和PDN阻抗有关。在大多数高速设计中,驱动器电路的输出引脚通常连接到具有一些输入电容的负载。当输出引脚判断为逻辑电路“1”时,负载处的寄生电容被完全充电至VCC。当输出缓冲电路关闭至逻辑“0”时,电容负载放电,向驱动器提供浪涌电流;这种快速电流会流过驱动器的接地引脚。

在理想情况下,IC封装和电路板的接地电压保持一致。不过,在实际设计中,由于PDN中的接合线、引线框架和寄生电感,管芯接地和电路板接地之间存在一些寄生电感。来自这些元素的总封装电感可以建模为一组串联的电感器,如上图所示。

当电流冲过接合线/引线框架/PDN上的电感时,管芯接地和电路板接地之间会产生反电动势。这会导致管芯接地和电路板接地在瞬间处于不同电压电平的现象,从而导致接地反弹噪声。然后,由于这些元件的直流电阻和IC封装/管芯中的寄生效应,这种积累会被抑制。更好地准确理解这如何影响信号行为,有助于理解这种寄生效应和迹线的排列形成了具有某些定义的阻抗和谐振频率的等效RLC电路。

PCB中的接地反弹如何影响电路和信号

当PCB中的接地反弹最小时,可能不会对管芯接地或信号行为造成任何干扰。它仍然会发生,但可能足够小以至于注意不到。不过,当接地反弹产生的反电动势较大时,尤其是同时切换多个输出时,器件的接地电平会上升到可能影响IC上其他引脚组的电平。

观察将驱动元件连接到电容负载的迹线时,您将发现迹线电感和电容也会影响接地反弹对信号的影响。请记住,由于其寄生电容和电感,所有迹线都具有一定的阻抗。由于真实迹线具有这些寄生效应,因此需要将其包含在由迹线、驱动器接地引脚处的电感以及负载电容形成的集总RLC网络中。

管芯上的电平位移

例如,遇到接地反弹的微控制器的接地电位可能会发生变化,使电源轨和接地之间测得的电压比没有接地反弹的情况高1.5V。换句话说,电源轨和管芯接地之间的电位差将比电源轨和电路板接地之间测得的电位高1.5V。说明这一点的另一种方式是,管芯接地和PCB接地平面之间存在瞬时1.5 V电位(即,在驱动器接地引脚上测量的值)。

在此示例中,连接到微控制器、工作电压为3.3 V的逻辑IC可能会将逻辑“0”信号解释为“1”,因为由于器件接地的电位电平发生偏移,它正在接收1.5 V逻辑“低”信号。继续此示例,遇到接地反弹的器件也可能误读来自其他元件的输入,因为输入电压电平是相对于管芯接地而言的。例如,逻辑“高”信号可能会被误解为“低”,因为由于管芯接地电压升高,输入引脚上的电压为1.8 V,而不是3.3 V。该值低于2.31 V的最低逻辑高电压。

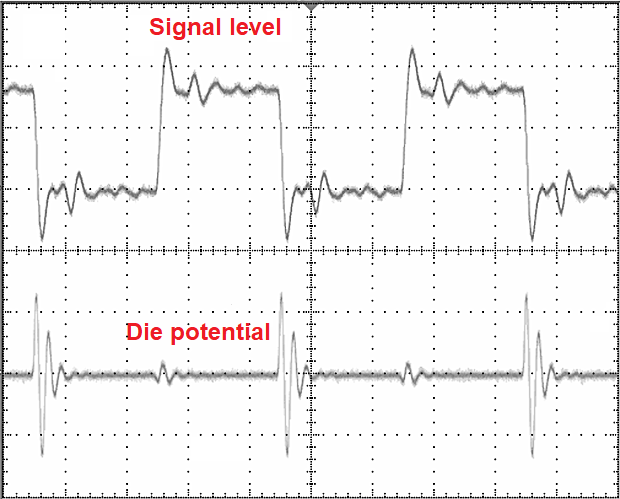

当所有输出同时被驱动为低电平时,接地反弹的影响最差(见上图)。这时管芯接地的电压差急剧增加。此外,这种电平转换的作用类似于RLC网络中的快速上升信号,在某些条件下会表现出欠阻尼瞬态振荡。

电平位移中的振荡

管芯接地上的电平偏移不会永远持续,管芯接地和PCB接地之间的电位差最终会回落到零。由于迹线和负载会提供一些寄生电容,因此该电平偏移会表现出阻尼振荡,就像您在RLC电路中观察到的那样。这些振荡可以表现出不同程度的阻尼,具体取决于电流环路中的总电阻。如果管芯接地存在振荡,则该振荡将叠加在输出信号上,从而产生瞬态振铃现象。下图显示了由于接地反弹引起的此类欠阻尼瞬态振荡。

在不实际情况下,驱动器的输出阻抗为零,负载输入阻抗为无穷大,迹线上产生的任何瞬态都将具有零阻尼。在实际情况下,由于通过驱动器的直流电导及其在低状态和高状态下的阻抗,阻尼将不为零。阻尼等于(R/2L),其中R是下沉电流环路周围的总电阻,L是包含下沉电流的电路的集总等效电感。

如果迹线电感足够低,阻尼常数就会很大,任何接地反弹振荡都会迅速衰减。如果集总迹线电感足够低且集总电容足够大,则接地反弹引起的瞬态可能会被过阻尼。这是DDR通道选择稍低迹线阻抗(40欧姆单端阻抗)的众多原因之一,因为它们的电感较低。输入电容较高的电容负载将具有较大的阻尼,这在高速PCB设计中会成为问题:边缘速率较快的元件往往具有较低的输入电容和更多的接地反弹问题。

减少PCB接地反弹的技巧

减少PCB接地反弹影响的最简单方法是将旁路电容器靠近受影响的元件放置。从物理层面而言,旁路电容器的作用类似于电池,可补偿相对于电源轨测量的管芯接地电位的变化。当驱动器切换时,旁路电容器还会接受来自放电负载电容的一些电流。必须将旁路电容器尽可能靠近元件的VCC引脚,以最大限度地减少接地迹线的总电感。将电容器放置在通过两个过孔连接到接地层的焊盘上也恰如其分,这将为通往PCB接地平面提供较低的电感路径。

将电阻与输出负载串联也是低阻抗驱动器的标准策略。如果您的迹线足够长,可以像传输线一样工作,那么您可能需要这样操作,以便在源端提供阻抗匹配(假设您的I/O处未应用片上端接);标准信令协议(例如DDR)无论如何都会这样操作。这将增加驱动器输出信号的阻尼常数,从而减慢变化信号的瞬态上升时间,并使瞬态振荡进入过阻尼状态。这通常仅适用于输出仍在接收器设置时间内(适用时)的情况,例如RAM芯片中的地址总线。

一般来说,您应避免将RESET、CHIP SELECT或SET等故障敏感型信号放置在容易出现接地反弹问题的同一逻辑IC上。总体而言,靠近GND引脚的输出引脚会因接地反弹而遇到较小的电平变化和较弱的振荡。

设计您的电路板以实现低接地反弹

归根结底,放置旁路电容器和正确设计迹线宽度是适用于各种设计的有效方法。如果操作正确,可以同时确保阻抗匹配和信号完整性。低阻抗PDN还可以减少高速PCB设计中出现的接地反弹和其他电源完整性问题。要最大限度地减少设计中不受控制的电压降并发现其他潜在的功耗问题,请尝试使用Altium Designer来准确设计PCB。

Altium 365的Altium Designer为电子行业提供了前所未有的集成度,直到现在才被归入软件开发领域,让设计人员能够在家办公,并达到空前的效率水平。

我们仅仅触及了在Altium 365上使用Altium Designer可能实现的功能的皮毛。请查看产品页面或点播网络研讨会,以获取更为深入的功能描述。

Back

Back