Directrices y topologías de enrutamiento DDR3

Sin memoria volátil, tu computadora necesitaría leer y escribir constantemente en la memoria no volátil como discos duros o Flash. La memoria no volátil es una de las cosas que hacen que las computadoras modernas sean tan poderosas y les otorga la adaptabilidad requerida para tareas avanzadas. Aunque DDR3 ahora es obsoleto, la memoria basada en DDR está aquí para quedarse y continuará jugando un papel central en la arquitectura de computadoras modernas. Con las herramientas de diseño adecuadas, puedes diseñar para la nueva generación de memoria basada en DDR y más allá. Ven a ver lo que Altium Designer puede hacer por ti.

ALTIUM DESIGNER®

El estándar de la industria en diseño electrónico para PCBs de alto rendimiento y arquitectura de memoria.

La tasa de datos doble tres (DDR3) es un tipo de memoria de acceso aleatorio dinámico (DRAM) que sucede a generaciones anteriores de DDR. Estas memorias tienen velocidades de reloj que alcanzan los 1066 MHz y soportan hasta 24 GB de memoria. Esta alta velocidad de reloj y gran capacidad de almacenamiento aseguraron que DDR3 permaneciera como un pilar en la computación moderna, pero eventualmente fue mejorado a DDR4. Cada nueva generación continúa empujando los límites de las tasas de datos y velocidades de reloj en PCBs de alta velocidad, y no es probable que las memorias basadas en DDR sean reemplazadas por una nueva arquitectura en el corto plazo.

Con esto en mente, los diseñadores de memorias necesitan estar conscientes de las diversas reglas de diseño de PCB para memorias basadas en DDR y cómo estas reglas están siendo llevadas al límite con DDR4. Los diseñadores también deben mantenerse informados sobre las diferentes topologías de enrutamiento para PCBs, ya que la implementación de nuevas topologías ha mejorado la funcionalidad de las memorias basadas en DDR, incluyendo DDR3.

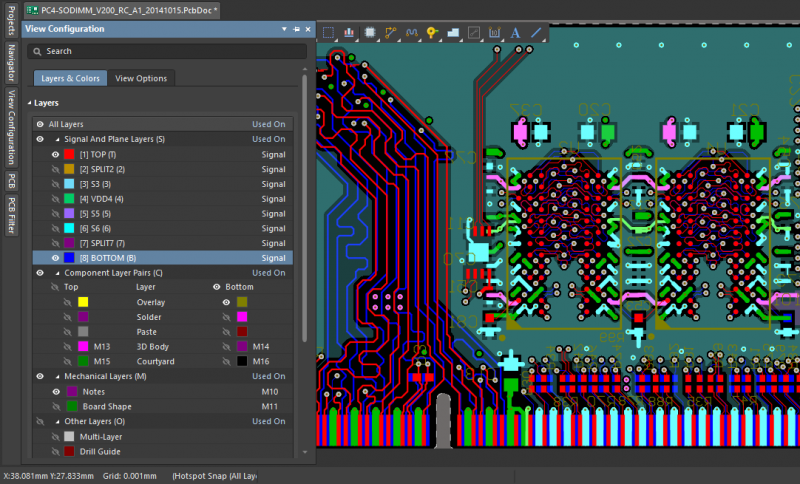

Trabajar con un excelente paquete de diseño de PCB como Altium Designer permite a los ingenieros de diseño implementar la mejor topología de enrutamiento para avanzar el rendimiento de DDR3, DDR4 y futuras generaciones de memoria. Altium Designer incluye diseño, enrutamiento interactivo, análisis de entrega de energía y herramientas de simulación que necesitas para asegurar que tus diseños basados en DDR operen al máximo rendimiento.

Guías de Diseño de Enrutamiento y Topología para Enrutamiento DDR3

DDR3 utiliza topología fly-by para el reloj diferencial, dirección, comando y señales de control. Originalmente, DDR3 usaba T-Topology para conectar bancos de memoria al controlador, pero las memorias DDR3 de mayor rendimiento usan topología fly-by para mejorar la compatibilidad con cargas altamente capacitivas y arquitecturas de IC.

Implementar la arquitectura correcta para DDR3 o DDR4, así como colocar interconexiones con paquetes de die de DDR SDRAM, requiere herramientas de enrutamiento adaptables que no restrinjan tu topología. Las trazas de señal se enrutan como pares diferenciales y deben coincidir precisamente dentro de tolerancias ajustadas en comparación con otros estándares de periféricos de computadora como PCIe.

Integridad de señal en el enrutamiento de DDR3 y DDR4

Muchas de las reglas de diseño estándar para asegurar la integridad de señal en otros dispositivos también se aplican a DDR3 y más allá. Las memorias de mayor rendimiento utilizan una topología de paso, que viene con requisitos específicos. Las pistas deben tener longitudes emparejadas con tolerancias ajustadas, los pares diferenciales deben estar estrechamente acoplados en la misma capa, y las longitudes de los stubs a cada dispositivo de memoria deben ser lo más cortas posible para prevenir efectos de línea de transmisión y resonancia en un stub. Todas las señales dentro de un grupo de carriles dado deben ser enrutadas en la misma capa ya que esto previene diferencias en el retraso de propagación y sesgo.

Para verificar la efectividad de su enrutamiento y diseño a lo largo de su placa, necesita herramientas de simulación que incorporen directamente sus datos de diseño. Trabajar dentro de una herramienta de integridad de señal que calcula formas de onda de reflexión y diafonía asegura que sus diseños cumplan con importantes estándares de rendimiento en DDR3 y memorias más nuevas.

- No todas las topologías son intuitivas, pero las herramientas de enrutamiento en su software de diseño de PCB deberían facilitar la implementación de la topología de enrutamiento DDR3 que necesita. Aprenda más sobre la implementación de topologías DDR3 en su software de diseño de PCB.

- Enrutar memorias DDR3 y CPUs no tiene que ser difícil cuando se trabaja con el software de diseño adecuado. Aprenda cómo enrutar memorias DDR3 y el fanout de su CPU en Altium Designer.

- Aunque DDR3 está obsoleto, DDR4 está vivo y bien, y muchas de las mismas ideas se aplican a las memorias DDR4. Aprende más sobre el enrutamiento DDR4 para dispositivos de memoria.

Configuración de diseño de layout para dispositivos de memoria

De DDR3 a DDR4 y más allá: Qué esperar

Con la memoria DDR3 siendo obsoleta y reemplazada por DDR4, y eventualmente DDR5, los diseñadores solo pueden esperar que los requisitos de enrutamiento y la topología se vuelvan más complejos. Las velocidades de señalización aumentarán y la topología de enrutamiento para dispositivos de memoria en chips impondrá nuevas restricciones de layout. Con esto en mente, necesitas software de diseño que sea adaptable a cualquier topología de enrutamiento mientras aún te ayuda a satisfacer importantes restricciones de diseño.

Integridad de señal como parte del diseño

Con cualquier nuevo layout de alta velocidad o alta frecuencia, una gran herramienta de simulación puede ayudarte a diagnosticar posibles problemas de integridad de señal a lo largo de tu placa. Los problemas potenciales pueden surgir en cualquier punto de tu layout, y las herramientas adecuadas de integridad de señal facilitan el diagnóstico de diafonía, determinar dónde se requiere terminación y determinar cómo los parásitos están afectando tu placa. Luego puedes probar rediseños potenciales y comparar directamente los resultados durante cada iteración.

- El diseño de DDR3 y DDR4 requiere ambos análisis de entrega de energía para asegurar que los dispositivos de memoria reciban los niveles de energía apropiados y para prevenir la formación de puntos calientes alrededor de su placa. Vea cómo puede incorporar el análisis de entrega de energía en su flujo de trabajo de diseño.

- Cuando sus herramientas de simulación están incorporadas en su software de diseño, puede validar rápidamente los cambios de diseño propuestos e identificar problemas de integridad de señal antes de que arruinen la funcionalidad de su placa. Aprenda más sobre la incorporación de simulaciones en su proceso de diseño.

- Con DDR siendo una arquitectura de memoria tan popular, hay muchos expertos que pueden ofrecer consejos de diseño. Consulte estos consejos de enrutamiento DDR para asegurar la integridad de la señal.

La integridad de la señal como parte del diseño en Altium Designer

Altium Designer: Unificando las Características de Diseño y Verificación

Dado las complejas demandas sobre las memorias DDR, los diseñadores necesitan programas que faciliten la fase de enrutamiento y diseño mientras aún aseguran que su diseño cumpla con los estándares básicos de diseño para DDR3, DDR4 y más allá. Cuando su software de diseño está construido sobre un motor de diseño basado en reglas, las características de su diseño verificarán su diseño contra los estándares de diseño mientras construye su placa. Sus herramientas de simulación construirán modelos directamente desde sus datos de diseño, y no tendrá que mover sus datos entre múltiples programas.

Diseño de Memoria DDR en Altium Designer

Con Altium Designer, tendrás acceso a las herramientas de enrutamiento, simulación y verificación que necesitas para diseñar arquitecturas de memoria DDR3, DDR4 y más nuevas que cumplan o superen los estándares de diseño. Solo Altium Designer coloca estas características en un solo programa, mientras que otras plataformas de diseño separan estas características en diferentes entornos. Todo lo que necesitas para el diseño DDR se puede encontrar en Altium Designer.

- Altium Designer coloca todas tus características importantes de diseño, enrutamiento, simulación y verificación para el diseño DDR en un solo entorno. Aprende más sobre el entorno de diseño unificado de Altium Designer.

- DDR3 y DDR4 ya son arquitecturas de memoria de alta velocidad, y solo deberías esperar que las velocidades de señalización y las tasas de transferencia de datos aumenten en las generaciones posteriores. Aprende más sobre el diseño de alta velocidad en Altium Designer.

- Con las complejidades de la arquitectura y el enrutamiento basados en DDR, los diseñadores necesitan herramientas de enrutamiento que ayuden a automatizar el proceso de enrutamiento mientras aún te dan control sobre tu diseño. Aprende más sobre el enrutamiento auto-interactivo en Altium Designer.

Otras plataformas de software de diseño de PCB dividen estas importantes características de diseño en diferentes programas. Con Altium Designer, tendrás acceso a las mejores características de enrutamiento y disposición de topología en una sola plataforma. Altium también te proporciona recursos para asegurar tu éxito. Tendrás acceso instantáneo a podcasts y seminarios web con expertos de la industria, el foro AltiumLive, una extensa base de conocimientos y tutoriales de diseño.

En lugar de quedarte atascado con una nueva versión de software de diseño obsoleto, intenta trabajar en el entorno de diseño integrado de Altium Designer. Tendrás acceso a las herramientas que necesitas para el enrutamiento y la disposición de DDR dentro de un único entorno. Podrás mantenerte a la vanguardia del diseño DDR cuando uses Altium Designer.