Dominando el control de EMI en el diseño de PCB: Estrategias de desacoplamiento para PDN

Mastering EMI Control in PCB Design Series

Decoupling Strategies for PDN

| February 6, 2025Bienvenido al quinto artículo de nuestra serie, Dominando el Control de la Interferencia Electromagnética (EMI) en el Diseño de PCBs. En este artículo, profundizaremos en las estrategias de distribución de energía y discutiremos cómo optimizarlas para mejorar el rendimiento de la Interferencia Electromagnética (EMI) en tus proyectos de PCB.

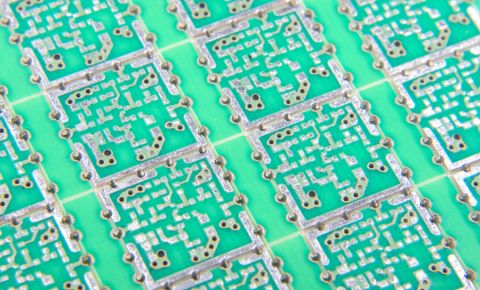

Figura 1 - Ejemplo de una estrategia de desacoplamiento en Altium Designer®

Un factor clave en el control de la EMI y la mejora de la integridad de la señal en una placa de circuito impreso digital es implementar estrategias de desacoplamiento efectivas. Estos enfoques aseguran un suministro de energía limpio y estable para los Circuitos Integrados (ICs) en tu placa.

Para lograr esto, los diseñadores de PCB necesitan crear una red de entrega de energía (PDN) fuerte que satisfaga las necesidades energéticas de los ICs de conmutación rápida, asegurando que reciban la cantidad correcta de corriente del suministro de energía. Diseñar una PDN que entregue energía de manera eficiente y a tiempo puede ser un desafío. Requiere reducir pérdidas y satisfacer las necesidades de impedancia para un alto rendimiento.

A medida que las tasas de datos y las velocidades de señal continúan aumentando, diseñar una Red de Entrega de Energía (PDN) con baja impedancia se vuelve más importante y también más difícil. Esto se debe a que el perfil de impedancia está estrechamente relacionado con la frecuencia de las señales transmitidas. Equilibrar estos factores es esencial para mantener el buen rendimiento de tus diseños de PCB y minimizar los problemas de EMI. Cuando se trata de diseñar una PDN efectiva, se utilizan varias técnicas comunes, como incorporar capacitores de desacoplamiento o usar planos de potencia y polígonos de cobre en el apilado.

Sin embargo, algunos métodos ampliamente aceptados y mitos han demostrado no solo ser ineficaces, sino también perjudiciales para el rendimiento de la placa.

Antirresonancia

Una técnica popular implica usar múltiples capacitores de diferentes tamaños, típicamente desde 10nF hasta 1µF. La idea es que los capacitores más grandes suministran energía a los Circuitos Integrados (ICs), mientras que los capacitores más pequeños filtran el ruido de alta frecuencia. Aunque este enfoque parece lógico, en realidad puede ser contraproducente al intentar reducir la impedancia total de la PDN. La razón por la que puede ser contraproducente es que los capacitores reales no se comportan de manera ideal; tienen efectos parásitos que se vuelven significativos a frecuencias más altas.

Los capacitores exhiben una impedancia capacitiva solo hasta su frecuencia resonante. Más allá de este punto, los parásitos en el paquete del capacitor comienzan a afectar la impedancia, causando que los capacitores se comporten de manera más inductiva. Usar capacitores de diferentes tamaños en un intento de lograr una capacitancia total más alta y una impedancia más baja puede presentar desafíos significativos. Esto se debe a que cada capacitor tiene su propio perfil de impedancia distinto, el cual es influenciado por sus características únicas. Cada capacitor también posee una frecuencia resonante diferente, llevando a una situación donde estos perfiles de impedancia se solapan entre sí. Este solapamiento de perfiles de impedancia resulta en picos de impedancia más altos en frecuencias específicas. Estos picos ocurren debido a la interacción entre las diversas frecuencias resonantes de los capacitores.

Figura 2 - Anti-resonancia — Efecto de colocar capacitores de diferentes tamaños con diferentes perfiles de impedancia en paralelo. Fuente: fresuelectronics.com

Como resultado, el efecto combinado de estas diferentes frecuencias resonantes puede crear regiones de impedancia aumentada, lo cual puede impactar negativamente el rendimiento general de la PDN y la efectividad de la estrategia de desacoplamiento.

Para abordar este problema, es mejor usar capacitores de Dispositivo de Montaje Superficial (SMD) del mismo tipo y paquete, con la menor inductancia de plomo posible. Colocar estos capacitores en paralelo ayuda a cumplir con los requisitos de capacitancia mientras se minimiza la inductancia en altas frecuencias. Además, alternar las polaridades de los terminales de los capacitores puede reducir la inductancia mutua y disminuir la inductancia total de la PDN.

Colocación de Capacitores

Cuando se trata de la colocación de capacitores de desacoplamiento, es esencial abordar el problema de la inductancia, que se vuelve cada vez más significativo a medida que las frecuencias de señal aumentan. Para mitigar esto, los capacitores deben posicionarse lo más cerca posible de los pines de alimentación de los Circuitos Integrados (ICs) que consumen corriente para su operación. Al colocar los capacitores cerca de los ICs, podemos minimizar la distancia que la corriente tiene que recorrer, reduciendo así los efectos inductivos que pueden obstaculizar el rendimiento a altas frecuencias.

En este contexto, la principal preocupación del diseñador no debería limitarse a la distancia física que debe recorrer la corriente, sino que debería considerar cuidadosamente el camino exacto que sigue la corriente. Aunque es importante reducir la distancia entre el capacitor de desacople y el pin al que está conectado, la razón subyacente de esto es minimizar la inductancia parásita asociada con las pistas. Esta colocación cercana ayuda a asegurar que los capacitores puedan suministrar efectivamente la carga necesaria a los ICs, ayudando a estabilizar la fuente de alimentación y mantener la integridad de la señal.

Figura 3 - Ejemplo de colocación del capacitor de desacople junto al IC con Altium Designer

Optimizando el camino, en lugar de solo enfocarse en acortarlo, el diseñador puede asegurar que la corriente fluya de la manera más eficiente, reduciendo el potencial de interferencia electromagnética (EMI) y mejorando el rendimiento general del circuito.

Por lo tanto, una planificación adecuada del camino puede ser tan crítica como minimizar la distancia en sí, ya que ambos afectan directamente los efectos parásitos que podrían comprometer la estabilidad y funcionalidad del circuito.

Además de asegurar que los capacitores estén colocados en proximidad cercana a los circuitos integrados (ICs), es altamente recomendable elegir capacitores con la menor Resistencia en Serie Equivalente (ESR) posible. La ESR es un parámetro crítico porque afecta directamente la eficiencia del capacitor en filtrar el ruido de alta frecuencia. Una ESR más baja reduce la impedancia total entre el capacitor y los pines de alimentación de los ICs, permitiendo una supresión más efectiva de las fluctuaciones de voltaje y el ruido en las líneas de suministro de energía. Además, los capacitores con menor ESR tienden a exhibir un mejor rendimiento en un rango de frecuencia más amplio, contribuyendo aún más a la reducción de la interferencia electromagnética (EMI) y mejorando la integridad de poder general del diseño.

Planos de Potencia

Cuando se diseña una tarjeta de circuito impreso (PCB) multicapa, es muy aconsejable posicionar un par de planos de potencia y de referencia de retorno, a menudo referidos como planos de “tierra”, cerca uno del otro dentro del apilado. Colocar estos planos en proximidad cercana aumenta la capacitancia distribuida entre ellos, lo que a su vez reduce la impedancia total de la red de distribución de potencia (PDN).

La configuración ideal implica posicionar las capas de señal adyacentes al plano de referencia de retorno, comúnmente referido como el “Plano de Tierra de Señal”. Esta colocación estratégica permite que la corriente de retorno fluya con un área de bucle mínima, lo que ayuda a confinar los campos electromagnéticos generados por las señales, controlando así la interferencia electromagnética (EMI) y reduciendo el ruido. Esta configuración mejora significativamente la integridad de la señal, ya que minimiza el diafonía y el acoplamiento electromagnético entre pistas, asegurando una mayor calidad de señal y una comunicación fiable a través del PCB. En el lado opuesto del plano de referencia de retorno, se debe colocar el plano de potencia. Esta disposición asegura que el plano de potencia pueda suministrar energía de manera efectiva a los circuitos integrados (ICs) sin interferencias del ruido causado por señales de conmutación rápida. Al separar el plano de potencia de las capas de señal mientras se mantiene una proximidad cercana al plano de referencia de retorno, puedes mitigar el acoplamiento de ruido y crear un ambiente estable para la entrega de potencia, contribuyendo finalmente a la operación eficiente de todo el circuito. Esta disposición mejora tanto la integridad de potencia como la integridad de señal, convirtiéndola en una práctica de diseño fundamental para PCBs multicapa de alto rendimiento.

Figura 4 - Ejemplo de un apilado optimizado de 6 capas con Altium Designer®

Usar tanto capacitores localizados, colocados cerca de los pines de alimentación de los ICs, como tener planos de alimentación y tierra cercanos entre sí proporciona una solución completa. Esta combinación mejora la Red de Entrega de Energía, reduce la Interferencia Electromagnética (EMI) y mantiene una mejor calidad de señal a través de la placa. Además, este enfoque ayuda a distribuir la energía de manera más uniforme a lo largo del PCB y reduce la inductancia que ocurriría si se utilizara un método de enrutamiento de energía tradicional.

Al combinar capacitores bien colocados con planos de alimentación y tierra espaciados de cerca, se crea un sistema de distribución de energía más confiable y eficiente, asegurando que su PCB funcione bien y esté libre de interferencias.

Mirando hacia el futuro, nuestro próximo artículo profundizará en el tema de la prevención de diafonía. Exploraremos estrategias para minimizar la interferencia entre señales y asegurar una comunicación más limpia y confiable en sus diseños de PCB, con un enfoque particular en las mejores prácticas de EMI. Puede asegurarse de no perdérselo siguiendo las páginas y redes sociales de Altium, así puede mantenerse actualizado con valiosos conocimientos y consejos prácticos para mejorar sus diseños.

Conclusión

Al trabajar en diseños avanzados de PCB, Altium Designer® ofrece un conjunto completo de herramientas que pueden simplificar enormemente el proceso para los diseñadores de PCB y ayudarte a crear una Red de Entrega de Energía (PDN) eficiente. Una de las características clave de Altium Designer® es el Administrador de Configuración de Capas. Esta herramienta te ayuda a seleccionar la configuración de apilamiento óptima para tu PCB basada en las necesidades específicas de tu sistema.

Además, Altium Designer® incluye herramientas integradas poderosas que te permiten realizar simulaciones detalladas de tu PDN. Estas simulaciones te ayudan a analizar y tomar decisiones informadas sobre cómo mejorar el diseño de tu placa de manera efectiva.

Para elevar tus proyectos de diseño de PCB y aprovechar estas herramientas avanzadas, te animamos a iniciar tu prueba gratuita de Altium Designer® y Altium 365™.

Esto te dará la oportunidad de experimentar de primera mano cómo esta herramienta CAD completa puede mejorar tus capacidades de diseño y llevar a diseños de PCB más eficientes y efectivos.