Maîtrise du contrôle des interférences électromagnétiques dans la conception de PCB : Stratégies de découplage pour le réseau de distribution d'énergie

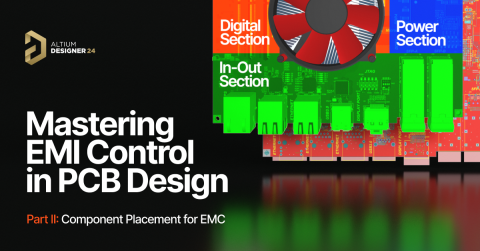

Mastering EMI Control in PCB Design Series

Decoupling Strategies for PDN

| February 6, 2025Bienvenue dans le cinquième article de notre série, Maîtriser le contrôle des interférences électromagnétiques (EMI) dans la conception de PCB. Dans cet article, nous allons approfondir les stratégies de distribution d'énergie et discuter de la manière de les optimiser pour améliorer la performance des interférences électromagnétiques (EMI) dans vos projets de PCB.

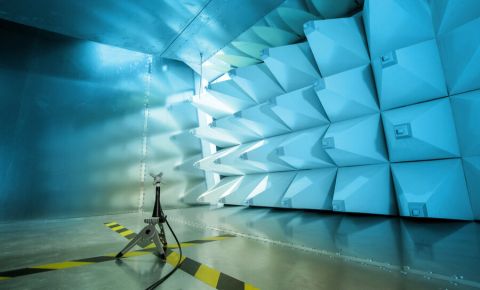

Figure 1 - Exemple d'une stratégie de découplage dans Altium Designer®

Un facteur clé dans le contrôle des EMI et l'amélioration de l'intégrité du signal sur un circuit imprimé numérique est la mise en œuvre de stratégies de découplage efficaces. Ces approches garantissent une alimentation en énergie propre et stable pour les circuits intégrés (IC) sur votre carte.

Pour y parvenir, les concepteurs de PCB doivent créer un réseau de distribution d'énergie (PDN) solide qui répond aux besoins énergétiques des IC à commutation rapide, en s'assurant qu'ils reçoivent la bonne quantité de courant de l'alimentation. Concevoir un PDN qui fournit l'énergie de manière efficace et en temps voulu peut être un défi. Cela nécessite de réduire les pertes et de répondre aux besoins d'impédance pour une haute performance.

Alors que les débits de données et les vitesses de signal continuent d'augmenter, concevoir un réseau de distribution d'énergie (PDN) à faible impédance devient plus important et également plus difficile. Cela est dû au fait que le profil d'impédance est étroitement lié à la fréquence des signaux transmis. Équilibrer ces facteurs est essentiel pour maintenir vos conceptions de PCB performantes et minimiser les problèmes d'EMI. Lorsqu'il s'agit de concevoir un réseau de distribution d'énergie (PDN) efficace, plusieurs techniques courantes sont utilisées, telles que l'incorporation de condensateurs de découplage ou l'utilisation de plans d'alimentation et de polygones en cuivre dans l'empilement.

Cependant, certaines méthodes largement acceptées et mythes se sont avérés non seulement inefficaces mais aussi préjudiciables à la performance de la carte.

Anti-résonance

Une technique populaire implique l'utilisation de plusieurs condensateurs de différentes tailles, allant typiquement de 10nF à 1µF. L'idée est que les plus gros condensateurs fournissent de l'énergie aux circuits intégrés (IC), tandis que les plus petits filtrent le bruit haute fréquence. Bien que cette approche semble logique, elle peut en fait se retourner contre vous lorsqu'il s'agit de réduire l'impédance globale du PDN. La raison pour laquelle cela peut être contre-productif est que les vrais condensateurs ne se comportent pas de manière idéale ; ils ont des effets parasites qui deviennent significatifs à des fréquences plus élevées.

Les condensateurs présentent une impédance capacitive uniquement jusqu'à leur fréquence de résonance. Au-delà de ce point, les parasitiques dans le boîtier du condensateur commencent à affecter l'impédance, provoquant un comportement plus inductif des condensateurs. Utiliser des condensateurs de tailles variées dans le but d'atteindre une capacité globale plus élevée et une impédance plus faible peut présenter des défis significatifs. Cela est dû au fait que chaque condensateur possède son propre profil d'impédance distinct, influencé par ses caractéristiques uniques. Chaque condensateur possède également une fréquence de résonance différente, conduisant à une situation où ces profils d'impédance se chevauchent les uns avec les autres. Ce chevauchement des profils d'impédance résulte en des pics d'impédance plus élevés à des fréquences spécifiques. Ces pics se produisent en raison de l'interaction entre les différentes fréquences de résonance des condensateurs.

Figure 2 - Anti-résonance — Effet de placer des condensateurs de différentes tailles avec différents profils d'impédance en parallèle. Source : fresuelectronics.com

En conséquence, l'effet combiné de ces fréquences de résonance divergentes peut créer des régions d'impédance accrue, ce qui peut impacter négativement la performance globale du PDN et l'efficacité de la stratégie de découplage.

Pour aborder ce problème, il est préférable d'utiliser des condensateurs à Montage en Surface (SMD) du même type et du même boîtier, avec la plus faible inductance de sortie possible. Placer ces condensateurs en parallèle aide à répondre aux exigences de capacité tout en minimisant l'inductance à haute fréquence. De plus, alterner les polarités des fils des condensateurs peut réduire l'inductance mutuelle et diminuer l'inductance globale du PDN.

Placement des condensateurs

Lorsqu'il s'agit du placement des condensateurs de découplage, il est essentiel de traiter le problème de l'inductance, qui devient de plus en plus significatif à mesure que les fréquences des signaux augmentent. Pour atténuer cela, les condensateurs devraient être positionnés aussi près que possible des broches d'alimentation des Circuits Intégrés (CI) qui consomment du courant pour leur fonctionnement. En plaçant les condensateurs près des CI, nous pouvons minimiser la distance que le courant doit parcourir, réduisant ainsi les effets inductifs qui peuvent entraver la performance à haute fréquence.

Dans ce contexte, la préoccupation principale du concepteur ne devrait pas se limiter à la distance physique que le courant doit parcourir, mais plutôt, il devrait considérer attentivement le chemin exact que le courant suit. Bien que réduire la distance entre le condensateur de découplage et la broche à laquelle il est connecté soit important, la raison sous-jacente est de minimiser l'inductance parasite associée aux pistes. Ce placement rapproché aide à garantir que les condensateurs peuvent fournir efficacement la charge nécessaire aux CI, aidant à stabiliser l'alimentation électrique et à maintenir l'intégrité du signal.

Figure 3 - Exemple de placement d'un condensateur de découplage à côté du CI avec Altium Designer

En optimisant le chemin, plutôt que de se concentrer uniquement sur sa réduction, le concepteur peut s'assurer que le courant circule de la manière la plus efficace, réduisant le potentiel d'interférence électromagnétique (EMI) et améliorant la performance globale du circuit.

Ainsi, une planification adéquate du chemin peut être tout aussi critique que la minimisation de la distance elle-même, car les deux affectent directement les effets parasites qui pourraient compromettre la stabilité et la fonctionnalité du circuit.

En plus de veiller à ce que les condensateurs soient placés à proximité immédiate des circuits intégrés (CI), il est vivement recommandé de choisir des condensateurs présentant la plus faible Résistance Série Équivalente (ESR) possible. L'ESR est un paramètre critique car il affecte directement l'efficacité du condensateur dans l'élimination du bruit de haute fréquence. Une ESR plus faible réduit l'impédance globale entre le condensateur et les broches d'alimentation des CI, permettant une suppression plus efficace des fluctuations de tension et du bruit sur les lignes d'alimentation. De plus, les condensateurs avec une ESR plus faible ont tendance à présenter de meilleures performances sur une plage de fréquences plus large, contribuant ainsi à la réduction de l'interférence électromagnétique (IEM) et à l'amélioration de l'intégrité globale de l'alimentation du design.

Plans d'alimentation

Lors de la conception d'un circuit imprimé (PCB) multicouche, il est fortement conseillé de positionner une paire de plans d'alimentation et de retour de référence, souvent désignés sous le nom de plans de "masse", à proximité l'un de l'autre dans l'empilement. Placer ces plans à proximité immédiate augmente la capacité distribuée entre eux, ce qui à son tour réduit l'impédance globale du réseau de distribution d'énergie (PDN).

La configuration idéale implique de positionner les couches de signal adjacentes au plan de retour de référence, communément appelé le « Plan de Masse du Signal ». Ce placement stratégique permet au courant de retour de circuler avec une aire de boucle minimale, ce qui aide à confiner les champs électromagnétiques générés par les signaux, contrôlant ainsi les interférences électromagnétiques (EMI) et réduisant le bruit. Cette configuration améliore considérablement l'intégrité du signal, car elle minimise le diaphonie et le couplage électromagnétique entre les pistes, assurant une qualité de signal supérieure et une communication fiable à travers le PCB. Du côté opposé du plan de retour de référence, le plan d'alimentation devrait être placé. Cette disposition assure que le plan d'alimentation peut fournir efficacement de l'énergie aux circuits intégrés (CI) sans interférence du bruit causé par les signaux à commutation rapide. En séparant le plan d'alimentation des couches de signal tout en maintenant une proximité étroite avec le plan de retour de référence, vous pouvez atténuer le couplage de bruit et créer un environnement stable pour la livraison de puissance, contribuant finalement au fonctionnement efficace de l'ensemble du circuit. Cet arrangement améliore à la fois l'intégrité de la puissance et l'intégrité du signal, ce qui en fait une pratique de conception fondamentale pour les PCB multicouches à haute performance.

Figure 4 - Exemple d'un empilement optimisé de 6 couches avec Altium Designer®

L'utilisation à la fois de condensateurs localisés, placés près des broches d'alimentation des CI, et de plans d'alimentation et de masse rapprochés offre une solution complète. Cette combinaison améliore le réseau de distribution d'énergie, réduit l'interférence électromagnétique (EMI) et maintient une meilleure qualité de signal sur l'ensemble du circuit imprimé. De plus, cette approche aide à répartir l'énergie de manière plus uniforme à travers le PCB et réduit l'inductance qui se produirait si une méthode de routage d'alimentation traditionnelle était utilisée.

En combinant des condensateurs bien placés avec des plans d'alimentation et de masse étroitement espacés, vous créez un système de distribution d'énergie plus fiable et efficace, garantissant que votre PCB fonctionne bien et reste exempt d'interférences.

Dans notre prochain article, nous aborderons le sujet de la prévention du diaphonie. Nous explorerons des stratégies pour minimiser les interférences entre les signaux et assurer une communication plus propre et fiable dans vos conceptions de PCB, avec un accent particulier sur les meilleures pratiques en matière d'EMI. Vous pouvez vous assurer de ne rien manquer en suivant les pages et les réseaux sociaux d'Altium, afin de rester informé des insights précieux et des conseils pratiques pour améliorer vos conceptions.

Conclusion

Lorsque vous travaillez sur des conceptions de PCB avancées, Altium Designer® offre un ensemble complet d'outils qui peuvent grandement simplifier le processus pour les concepteurs de PCB et vous aider à créer un réseau de distribution d'énergie (PDN) efficace. L'une des caractéristiques clés d'Altium Designer® est le Gestionnaire de Configuration de Couches. Cet outil vous aide à sélectionner la configuration de superposition optimale pour votre PCB en fonction des besoins spécifiques de votre système.

De plus, Altium Designer® inclut des outils intégrés puissants qui vous permettent d'effectuer des simulations détaillées de votre PDN. Ces simulations vous aident à analyser et à prendre des décisions éclairées sur la manière d'améliorer efficacement la conception de votre carte.

Pour élever vos projets de conception de PCB et profiter de ces outils avancés, nous vous encourageons à commencer votre essai gratuit d'Altium Designer® et d'Altium 365™.

Cela vous donnera l'opportunité de vivre en première main comment cet outil CAO complet peut améliorer vos capacités de conception et conduire à des conceptions de PCB plus efficaces et efficaces.