PCB設計におけるEMI制御の習得:PDNのためのデカップリング戦略

PCB設計におけるEMI制御をマスターするシリーズの第5回目へようこそ。この記事では、電力分配戦略についてさらに深く掘り下げ、PCBプロジェクトにおける電磁干渉(EMI)性能を向上させるための最適化方法について議論します。

図1 - Altium Designer®でのデカップリング戦略の例

デジタルプリント基板上でEMIを制御し、信号整合性を向上させる上での重要な要素は、効果的なデカップリング戦略を実装することです。これらのアプローチは、基板上の集積回路(IC)にクリーンで安定したエネルギー供給を保証します。

これを達成するために、PCB設計者は、高速スイッチングICのエネルギー需要を満たす強力な電力供給ネットワーク(PDN)を作成する必要があります。これにより、電源から適切な電流量をICが受け取ることを保証します。効率的かつタイムリーにエネルギーを供給するPDNを設計することは挑戦的です。これには、損失を減らし、高性能のためのインピーダンスニーズを満たすことが求められます。

データレートと信号速度が増加し続ける中、低インピーダンスのPDN(Power Delivery Network)を設計することがより重要かつ困難になっています。これは、インピーダンスプロファイルが送信される信号の周波数と密接に関連しているためです。これらの要因をバランスさせることは、PCB設計の性能を維持し、EMI(電磁干渉)の問題を最小限に抑えるために不可欠です。効果的なパワーデリバリーネットワーク(PDN)を設計する際には、デカップリングキャパシタの組み込みや、スタックアップ内でのパワープレーンや銅ポリゴンの使用など、いくつかの一般的な技術が使用されます。

しかし、広く受け入れられている方法や神話の中には、実際には効果がないだけでなく、ボードの性能に悪影響を及ぼすものもあります。

アンチレゾナンス

一つの人気のある技術は、10nFから1µFまでの異なるサイズの複数のキャパシタを使用することです。大きなキャパシタが集積回路(IC)にエネルギーを供給し、小さなキャパシタが高周波ノイズをフィルタリングするという考え方です。このアプローチは論理的に思えますが、PDNの全体的なインピーダンスを減らそうとするときに実際には逆効果になることがあります。逆効果になる理由は、実際のキャパシタは理想的に振る舞わず、高周波数で顕著になる寄生効果を持っているためです。

コンデンサは、その共振周波数までのみ容量性インピーダンスを示します。この点を超えると、コンデンサのパッケージ内の寄生成分がインピーダンスに影響を与え始め、コンデンサの振る舞いがより誘導性を帯びるようになります。全体の容量を高め、インピーダンスを低くするために異なるサイズのコンデンサを使用する試みは、重大な課題を提示することがあります。これは、各コンデンサが独自のインピーダンスプロファイルを持ち、その特有の特性によって影響を受けるためです。各コンデンサは異なる共振周波数も持っており、これらのインピーダンスプロファイルが互いに重なる状況につながります。このインピーダンスプロファイルの重なりは、特定の周波数でより高いインピーダンスピークを引き起こします。これらのピークは、コンデンサのさまざまな共振周波数間の相互作用によって発生します。

図2 - アンチレゾナンス — 異なるインピーダンスプロファイルを持つ異なるサイズのコンデンサを並列に配置する効果。出典: fresuelectronics.com

その結果、これらの異なる共振周波数の組み合わせ効果により、インピーダンスが増加する領域が生じ、PDNの全体的な性能とデカップリング戦略の効果に悪影響を及ぼす可能性があります。

この問題に対処するためには、可能な限りリードインダクタンスが低い、同じタイプおよびパッケージの表面実装デバイス(SMD)キャパシタを使用することがより良いです。これらのキャパシタを並列に配置することで、高周波でのインダクタンスを最小限に抑えながら、容量要件を満たすことができます。さらに、キャパシタのリードの極性を交互にすることで、相互インダクタンスを減少させ、PDNの全体的なインダクタンスを低下させることができます。

キャパシタの配置

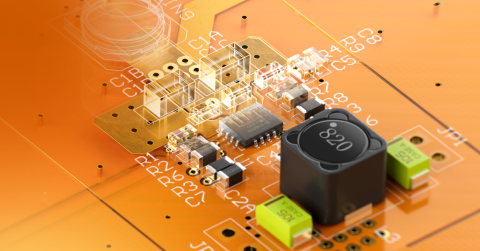

デカップリングキャパシタの配置に関しては、信号周波数が上昇するにつれてますます重要になるインダクタンスの問題に対処することが不可欠です。これを軽減するために、キャパシタは電流を消費する集積回路(IC)の電源ピンにできるだけ近い位置に配置するべきです。ICの近くにキャパシタを配置することで、電流が移動する距離を最小限に抑え、高周波での性能を阻害する可能性のある誘導効果を減少させることができます。

この文脈では、設計者の主な懸念事項は、電流が移動する物理的距離に限定されるべきではなく、むしろ電流がたどる正確な経路を慎重に考慮すべきです。デカップリングキャパシタとそれが接続されているピンとの間の距離を短くすることが重要ですが、その背景にある理由は、トレースに関連する寄生インダクタンスを最小限に抑えることにあります。この近接配置により、キャパシタがICに必要な電荷を効果的に供給できるようになり、電源を安定させ、信号の整合性を維持するのに役立ちます。

図3 - Altium Designerを使用したICの隣に配置されたデカップリングキャパシタの例

経路を最適化することで、単に短くすることに焦点を当てるのではなく、設計者は電流が最も効率的な方法で流れるようにすることができ、電磁干渉(EMI)の可能性を減らし、全体的な回路性能を向上させることができます。

したがって、適切な経路計画は、距離自体を最小限に抑えることと同じくらい重要であり、どちらも回路の安定性と機能性を損なう可能性のある寄生効果に直接影響します。

コンデンサを集積回路(IC)の近くに配置することを確実にするだけでなく、できるだけ低い等価直列抵抗(ESR)を持つコンデンサを選択することが強く推奨されます。ESRは、高周波ノイズをフィルタリングする際のコンデンサの効率に直接影響を与える重要なパラメータです。ESRが低いほど、コンデンサとICの電源ピンの間の全体的なインピーダンスが減少し、電源ライン上の電圧変動とノイズの抑制がより効果的になります。さらに、ESRが低いコンデンサは、より広い周波数範囲での性能が向上する傾向があり、電磁干渉(EMI)の低減と設計の全体的な電力整合性の向上にさらに寄与します。

電力平面

多層プリント回路基板(PCB)を設計する際には、「グラウンド」平面としてしばしば参照される一対の電力およびリターン参照平面をスタックアップ内で互いに近接して配置することが非常に望ましいです。これらの平面を近接して配置することで、それらの間の分散容量が増加し、結果として電力分配ネットワーク(PDN)の全体的なインピーダンスが低下します。

理想的な構成では、シグナル層を返信参照平面の隣に配置し、一般に「シグナルグラウンド」と呼ばれます。この戦略的な配置により、返信電流が最小限のループ領域で流れることができ、これによりシグナルによって生成される電磁場を制限し、電磁干渉(EMI)を制御し、ノイズを減少させます。この設定は、トレース間のクロストークと電磁結合を最小限に抑えることで、信号の整合性を大幅に向上させ、PCB全体での高品質で信頼性の高い通信を保証します。返信参照平面の反対側には、電源平面を配置するべきです。このレイアウトにより、電源平面が高速スイッチング信号によって引き起こされるノイズの干渉なしに、集積回路(IC)に効果的にエネルギーを供給できることが保証されます。電源平面をシグナル層から分離しつつ、返信参照平面に近接させることで、ノイズ結合を軽減し、電力供給の安定した環境を作り出すことができ、結果として回路全体の効率的な動作に貢献します。この配置は、電力の整合性と信号の整合性の両方を向上させ、高性能な多層PCBの基本的な設計実践となります。

図4 - Altium Designer®を使用した最適化された6層スタックアップの例

ICの電源ピンに近い位置に配置された局所的なキャパシタと、電源層とグランド層を近接させることにより、完全なソリューションが提供されます。この組み合わせは、電力供給ネットワークを改善し、電磁干渉(EMI)を減少させ、ボード全体でより良い信号品質を維持します。さらに、このアプローチはPCB全体に電力をより均等に分散させ、従来の電力ルーティング方法を使用した場合に発生するであろうインダクタンスを減少させます。

適切に配置されたキャパシタと密接に配置された電源層とグランド層を組み合わせることで、より信頼性が高く効率的な電力分配システムを作り出し、PCBが良好に機能し、干渉のない状態を保証します。

次回の記事では、クロストーク防止に関する話題に深く潜り込みます。信号間の干渉を最小限に抑え、EMIのベストプラクティスに特に焦点を当てながら、PCB設計におけるよりクリーンで信頼性の高い通信を確保する戦略を探求します。Altiumのページやソーシャルメディアをフォローすることで、貴重な洞察と実践的なヒントを提供し、設計を強化するための最新情報を逃さずに確認できます。

結論

高度なPCB設計に取り組む際、Altium Designer®はPCB設計者のプロセスを大幅に簡素化し、効率的なパワーデリバリーネットワーク(PDN)を作成するのに役立つ包括的なツールセットを提供します。Altium Designer®の主要な特徴の一つは、レイヤースタックアップマネージャーです。このツールは、システムの特定のニーズに基づいて、PCBの最適なスタックアップ構成を選択するのに役立ちます。

さらに、Altium Designer®には、PDNの詳細なシミュレーションを実行できる強力な統合ツールが含まれています。これらのシミュレーションは、ボード設計を効果的に改善する方法について分析し、情報に基づいた決定を行うのに役立ちます。

これらの高度なツールを活用し、PCB設計プロジェクトを向上させるために、Altium Designer®およびAltium 365™の無料トライアルを開始することをお勧めします。

これにより、この完全なCADツールが設計能力をどのように向上させ、より効率的で効果的なPCB設計につながるかを直接体験する機会を得られます。