Interfejsowanie pamięci DDR z FPGA AMD/Xilinx

Dowiedz się, jak zintegrować pamięć DDR z FPGA AMD/Xilinx.

Wstęp

Interfejsowanie ulotnej pamięci DDR z FPGA bez wcześniejszego doświadczenia może początkowo wydawać się dość zniechęcające. Pomimo inherentnej elastyczności FPGA, gdzie moglibyśmy założyć, że możemy podłączyć I/O zewnętrznej pamięci DDR praktycznie do dowolnych wolnych pinów, musimy nadal rozważyć wiele ograniczeń.

Na przykład, gdzie umieścić pewne grupy pinów pamięci DDR, jakie napięcia użyć do zasilania banków, jakie zegary są potrzebne i gdzie je podłączyć, jak unikać naruszeń czasowych i tak dalej.

Oprócz interfejsowania na poziomie schematów, musimy również zwrócić uwagę na 'rzeczywisty' interfejs na płytce drukowanej, takie jak zasilanie i dostarczanie energii, odłączanie, terminacja, impedancja i długość ścieżek, dopasowanie opóźnień i więcej.

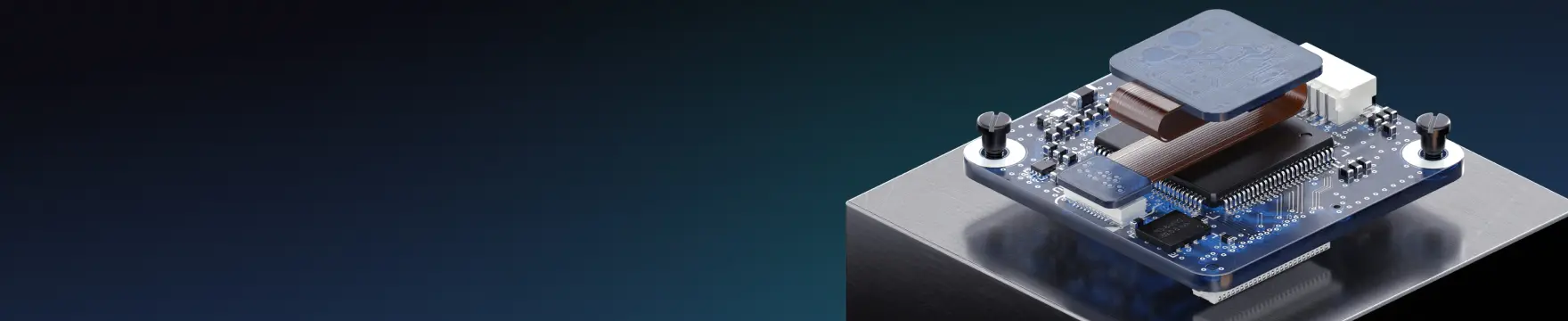

W tym artykule przyjrzymy się interfejsowaniu pamięci DDR z FPGA z punktu widzenia systemowego i schematycznego. Jako praktyczny przykład weźmiemy pod uwagę projekt audio DSP oparty na AMD/Xilinx Spartan-7 (nazwany ‘Xerxes’), który interfejsuje się z pewną pamięcią DDR2.

Sprzęt audio DSP Xerxes (FPGA AMD/Xilinx Spartan-7 z pamięcią DDR2)

Typ pamięci

Typ używanej pamięci zależy od projektu. Zależy to od naszych wymagań dotyczących pojemności i przepustowości pamięci, jak również od możliwości wybranego przez nas FPGA.

Ogólnie rzecz biorąc, większość nowoczesnych FPGA może interfejsować się z pamięcią DDR2 i DDR3 (oraz ich niskonapięciowymi, niskoenergetycznymi wariantami). Oczywiście, szybsza pamięć DDR4 i wyższa jest również możliwa, ale zazwyczaj tylko dla bardziej zaawansowanych FPGA.

Nie tylko maksymalna możliwa szybkość transmisji danych jest ważna, ale także napięcie i wymagania energetyczne, typ obudowy, koszt i dostępność są ważne. To wszystko należy wziąć pod uwagę na wczesnym etapie projektowania.

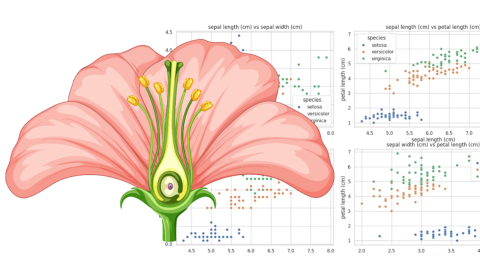

Porównanie pamięci DDR (Źródło: synopsys.com)

Wybierając typ naszej pamięci, musimy również zwrócić uwagę na klasę szybkości urządzenia pamięciowego oraz ocenę szybkości kontrolera pamięci w FPGA. Możemy zdecydować się na ‘zaniżenie’ naszej pamięci lub kontrolera, nie wykorzystując pełnej przepustowości, co z kolei daje nam więcej luzu czasowego.

Typowa tabela zaniżania pamięci (Źródło: AMD/Xilinx UG933)

Specjalnie dla FPGA AMD/Xilinx, sugerowałbym pobranie ich środowiska IDE Vivado i eksperymentowanie z darmowym IP Memory Interface Generator (MIG).

To szybko pokaże Ci, jakie typy pamięci, klasy prędkości i kompatybilne części możesz użyć.

Przykład kompatybilnych części pamięci Vivado MIG

Możesz zapytać, dlaczego zdecydowałem się na pamięć DDR2 dla płyty Xerxes?

Mimo że jest to dość stary standard, użycie pamięci DDR2 oznaczało, że mogłem wykorzystać już dostępny regulator 1,8V na płycie (zasilający inne części FPGA) i nie musiałem dodawać kolejnego oddzielnego regulatora.

Ponadto, projekt Xerxes nie ma szczególnie wysokich wymagań co do przepustowości pamięci, więc interfejs DDR2 był wystarczający.

Co więcej, posiadanie interfejsu o niższej przepustowości ułatwia projektowanie PCB, terminację i ograniczenia czasowe.

Pamięć DDR i interfejs FPGA

Po wybraniu odpowiedniego urządzenia pamięciowego nadszedł czas, aby połączyć to z FPGA w schemacie.

Najpierw musimy wybrać odpowiedni bank. Jeśli używasz interfejsu danych o szerokości 16 bitów (lub mniejszej), dla większości FPGA zwykle może to pasować do jednego banku. Jeśli nie, musimy podzielić interfejs pamięci na kilka banków.

Dla uproszczenia, zdecydujemy się na interfejs pamięci o szerokości 16 bitów, jak to ma miejsce w przypadku płyty Xerxes. Wybierz wolny bank, który może pracować z tym samym napięciem co sama pamięć DDR (w przypadku Xerxes jest to bank 34 przy 1,8V ze względu na użycie pamięci DDR2).

Bank FPGA 34 z odpowiednim odciążeniem pracujący z zasilania 1,8V

Dla FPGA AMD/Xilinx, używając narzędzi Vivado i MIG, uzyskanie rozmieszczenia pinów dla naszej pamięci DDR jest bardzo proste. Narzędzie albo sugeruje odpowiednie rozmieszczenie pinów dla tego banku, albo możemy przypisać piny ręcznie i zweryfikować rozmieszczenie pinów.

Narzędzie do rozmieszczenia pinów Vivado MIG

Jeśli konfigurujesz rozmieszczenie pinów ręcznie, upewnij się, że poszczególne pasma bajtów DDR mają ten sam numer bajtu banku, a różnicowe stroby są na różnicowych pinach FPGA zdolnych do DQS.

Pamiętaj, że rozmieszczenie pinów prawdopodobnie zostanie dostosowane podczas etapu projektowania i trasowania PCB. Dzięki elastyczności FPGA, zamiana pinów podczas procesu projektowania PCB może uprościć trasowanie i zminimalizować przejścia między warstwami.

W tym przykładzie, ponieważ pracujemy z jednego banku, musimy użyć wewnętrznego VREF, ograniczając maksymalną przepustowość pamięci.

Dodatkowo, musimy uważać na taktowanie. Idealnie, źródło zegara powinno być w tym samym banku, co pin zdolny do taktowania (lub piny, jeśli używamy źródła zegara różnicowego).

Na koniec upewnij się, że używasz narzędzi dostawcy do weryfikacji projektu i czasowania. Następnie, mając początkowe rozmieszczenie pinów, w schemacie zdefiniuj klasy sieci, pary różnicowe i reguły, oraz użyj kolorów, aby ułatwić sobie projektowanie PCB.

Połączenia DDR2 i źródło zegara w banku FPGA 34

Dla pojedynczego urządzenia wystarczy zrealizować połączenia punkt-punkt na komponencie pamięci DDR.

Terminacja powinna być obecna na sygnałach adresu/komendy/kontroli (ACC); jednak przy niższych prędkościach danych często można się bez tego obejść. Zawsze dodaję terminację na parze zegarowej różnicowej. Linie bajtów danych są terminowane wewnętrznie z obu stron.

Zaleca się umieszczenie rezystorów podciągających 4,7k na liniach CKE, ODT i opcjonalnie CS#.

Połączenia sygnałowe i zasilające modułu pamięci DDR2

Oczywiście moduł pamięci musi być zasilany. W przypadku płytki Xerxes, moduł DDR2 jest podłączony do tego samego regulatora 1,8V co nasz bank FPGA 34. Wymagane jest odpowiednie odfiltrowanie – jako reguła, jeśli nie określono inaczej w kartach katalogowych lub notach aplikacyjnych, należy dążyć do użycia jednego małego kondensatora (~100nF) na każde dwa piny VDD i jednego, większego kondensatora buforowego na każde dziesięć pinów VDD.

Napięcie pinu VREF może być wygenerowane za pomocą prostego dzielnika potencjału z filtrowym kondensatorem, jak pokazano na powyższym obrazie.

Podsumowanie

W tym artykule przedstawiliśmy podstawowe strategie włączania zewnętrznej, nieulotnej pamięci DDR do naszych projektów opartych na FPGA z punktu widzenia systemowego i schematycznego.

Pamiętaj, że to są absolutne podstawy, a w zależności od wymagań systemu, projekt będzie znacznie bardziej zaawansowany. Szczególnie, jeśli planujesz używać szybszych części pamięci i interfejsów oraz wielu modułów.

Projektując zaawansowane systemy oparte na FPGA i DDR, upewnij się, że korzystasz z narzędzi i funkcji zawartych w światowej klasy narzędziach ECAD, takich jak Altium Designer. Zabezpiecz swoją darmową wersję próbną Altium Designer i Altium 365 tutaj.