Co to jest standard JESD204C dla przetworników ADC/DAC?

JESD204C zapewnia ustandaryzowany interfejs dla przetworników ADC RF o wysokiej częstotliwości próbkowania, które obecnie coraz częściej pojawiają się w zastosowaniach komercyjnych w przestrzeni kosmicznej.

Interfejsy szeregowe miały trudności z nadążaniem za potrzebami komponentów konwerterów danych o wysokiej częstotliwości próbkowania, a mianowicie ADC i DAC. Jedną z opcji do tego celu były wcześniej łącza LVDS między konwerterami danych a kontrolerem hosta. Te łącza zapewniały wysokie prędkości transmisji danych za pomocą par różnicowych do pojedynczego urządzenia, oferując szybki transfer danych z szybko próbkujących ADC. Później JEDEC wydał specyfikację JESD204, która od tego czasu została włączona do wielu komponentów jako interfejs konwertera danych.

Najnowsza iteracja standardów interfejsu JESD204, obecnie JESD204C, przynosi ekstremalne prędkości transmisji danych do szybkich komponentów ADC/DAC, które są używane do próbkowania sygnałów z bardzo wysoką częstotliwością próbkowania. Teraz, gdy najnowsza iteracja standardu jest dostępna już ponad 2 lata, dostępnych jest wiele komponentów, które mogą być używane z FPGA do zapewnienia ultrasybkiego próbkowania, transmisji i przetwarzania sygnałów DSP w systemach RF.

Przegląd JESD204C

Standard JESD204C to najnowsza iteracja ogólnego standardu JESD204, który jest publikowany i utrzymywany przez JEDEC. Standard został opracowany w celu zastąpienia użycia łączy LVDS pomiędzy przetwornikami danych a ich systemami hostów. Definiuje on interfejs szeregowy i protokół używany w przetwornikach ADC/DAC o wysokiej częstotliwości próbkowania do próbkowania sygnału, syntezy i synchronizacji. Aspekt synchronizacji jest ważny dla tego interfejsu, ponieważ pozwala pojedynczemu kontrolerowi hosta na synchronizację próbkowania sygnału i syntezy w wielu urządzeniach.

Niektóre z głównych parametrów operacyjnych zaimplementowanych w warstwie fizycznej są wymienione w poniższej tabeli. Obecna iteracja JESD204C poprawia szybkość transmisji danych i charakterystyki kodowania poprzedniej iteracji JESD204B, która używała kodowania 8b/10b z maksymalną szybkością transmisji danych 12,5 Gbps. Ten interfejs można znaleźć w przetwornikach ADC/DAC działających w zakresie od 100 MSps do 1 GSps lub wyżej.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Przykładowa topologia

Topologia interfejsu JESD204C zależy od podklasy interfejsu. JESD204B wprowadziło Podklasy 1 i 2, aby zaimplementować strategię synchronizacji znana jako deterministyczne opóźnienie. Strategia ta osiąga synchronizację między urządzeniami poprzez określenie niedopasowania fazy między strumieniami danych przesyłanymi do kontrolera hosta.

- Podklasa 0 - Brak wsparcia dla deterministycznego opóźnienia (kompatybilność wsteczna z JESD204A)

- Podklasa 1 - Deterministyczne opóźnienie osiągnięte za pomocą zewnętrznego oscylatora referencyjnego (SYSREF) jako sygnał czasowy

- Podklasa 2 - Deterministyczne opóźnienie osiągnięte za pomocą pinu SYNC między kontrolerem hosta a przetwornikiem ADC/DAC

Dwie implementacje interfejsu pokazano na poniższej grafice.

DATA1 i DATA2 są prowadzone jako pary różnicowe; każdy tor w tych grupach I/O jest parą różnicową, a dane urządzenie może mieć wiele torów (niektóre produkty mają do 8 na urządzenie). W obu podklasach, źródło zegara jest prowadzone do wszystkich urządzeń w sposób synchroniczny ze źródłem. Czas i deterministyczne opóźnienie są osiągane w każdej podklasie poprzez odpowiednie dopasowanie SYSREF i DCLK/SYNC do czasów ustawienia i trzymania, jak również do siebie, gdy są rozprowadzane między wieloma przetwornikami danych.

Routing, Deskew, i Latencja

Deterministyczne opóźnienie zostało wspomniane powyżej: jest to technika, dzięki której pojedynczy kontroler hosta może synchronizować zbieranie danych i syntezę na wielu urządzeniach z precyzyjnym czasowaniem tak, że skos czasowy między ramkami próbkowania jest znany. Jest to korygowane przez dostrojenie opóźnień ścieżek do siebie, tak aby opóźnienia między nimi były dopasowane. Interfejs JESD204B lub JESD204C używa dopasowania opóźnień w bitach kontrolnych pochodzących z SYSREF (w podklasie 1) lub z pinów SYNC (w podklasie 2).

Poniższa tabela przedstawia wymagania dotyczące dopasowania długości/opóźnień w sygnałach czasowych dla każdej podklasy w interfejsach JESD204B i JESD204C.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Główna różnica tutaj dotyczy sposobu traktowania linii SYNC. W Podklasie 1, te linie są używane tylko do synchronizacji grup kodów, podczas gdy w Podklasie 2 są również używane do czasowania. Dlatego JESD204C ma mniej sygnałów na daną liczbę kanałów I/O w przetwornikach danych.

Dlaczego JESD204C a nie LVDS?

Zaletą interfejsu JESD204C dla szybkiego próbkowania i syntezy na częstotliwościach GHz jest zdolność do eliminacji skosu i niedopasowania opóźnień między wieloma przetwornikami. Dla każdego interfejsu JESD204 istnieje pewien budżet skosu, który jest maksymalną ilością skosu, jaka może być skompensowana w schemacie czasowym systemu, aby zagwarantować deterministyczne opóźnienie w granicach szumu fazowego. Celem jest zapewnienie, aby kontroler hosta znał niedopasowania fazowe wynikających strumieni danych przychodzących i mógł kompensować je w logice, ustanawiając tym samym prawdziwe czasowanie między próbkowanymi sygnałami.

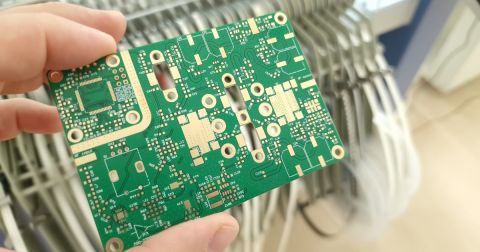

Inny powód użycia JESD204C polega na tym, że redukuje on wymagania dotyczące trasowania i czasowania w układzie PCB. W typowej implementacji, pary różnicowe DATA1 i DATA2 przychodzące z Urządzenia 1 i Urządzenia 2 będą miały pewien skos między sobą. Przy użyciu LVDS wymagałoby to dopasowania par różnicowych biegnących równolegle do siebie. W JESD204C, musimy tylko wyeliminować skos przez sieci DCLK i SYSREF/SYNC, ale nie przez sieci danych między urządzeniami. To czyni interfejs niezbędnym w urządzeniach mieszanych o wysokiej gęstości sygnałów.

Projektanci tworzący zaawansowane technologie dla przemysłu kosmicznego mogą wdrożyć standard JESD204C, korzystając z najlepszych narzędzi do projektowania produktów w Altium Designer®. Gdy zakończysz projektowanie i będziesz chciał przekazać pliki swojemu producentowi, platforma Altium 365™ ułatwia współpracę i udostępnianie projektów.

Przedstawiliśmy tylko namiastkę możliwości, jakie oferuje Altium Designer na Altium 365. Zacznij swoją darmową wersję próbną Altium Designer + Altium 365 już dziś.