The Board-Level Trends Defining Wide-Bandgap Power

Wide-bandgap switches have become the pragmatic choice when power targets collide with thermal limits and enclosure constraints. Silicon carbide (SiC) is now the default path for many high-voltage, high-power stages, where efficiency gains translate directly into reduced cooling requirements and higher usable power density. Gallium nitride (GaN) continues expanding beyond consumer fast chargers into server and telecom power, where switching speed and density drive competitive advantage.

The challenge with SiC and GaN is implementing fast, clean, and repeatable switching. Once edge rates rise, the PCB transitions from a passive interconnect to an active circuit element. Parasitic inductance and capacitance shape overshoot and ringing. Common-mode transients stress the isolation barrier. Measurement paths pick up switching artifacts. EMI becomes a layout and architecture problem before it becomes a filtering problem.

This article pulls those realities into six board-level trends you can design around. The goal is to help you spot the failure modes that typically show up on first spin, make better up-front choices on placement and partitioning, and align device selection with the driver, isolation, sensing, and packaging ecosystem you can support across projects.

Now, let’s look at the trends defining wide-bandgap development today.

Key Takeaways

- SiC and GaN adoption continues to expand, driven by higher efficiency and power density across EV, industrial, energy, and data center power applications.

- The critical design effort is shifting to the board level. Layout parasitics, isolation performance, sensing fidelity, thermal paths, and EMI containment now set the ceiling for what you can ship.

- Treat drivers, isolation, sensing, and packaging as an ecosystem choice. Standardize footprints, reserve tuning options, and pre-plan alternates early.

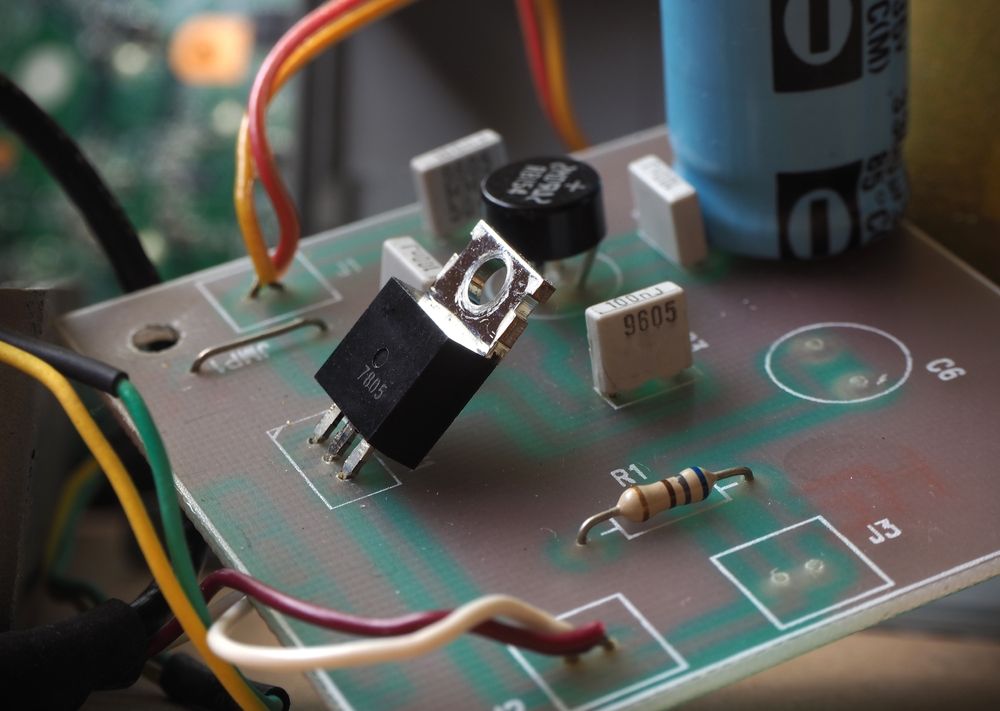

Trend 1: Rising Voltages Reshape the Entire Design Stack

Higher bus voltages are spreading from industrial and energy systems into EV platforms and charging infrastructure, affecting device selection, magnetics, sensing, spacing rules, and protection strategy. This voltage escalation amplifies design margins across the board, and layout-induced transients that were manageable at 400 V become destructive at 800 V.

Emerging board-level implications:

- Explicit voltage margin policies for overshoot become mandatory.

- Creepage and clearance decisions drive layout constraints that ripple into package choice and mechanical keepouts.

- Protection behavior is incorporated into switch selection because fault energy increases with voltage.

Example product (SiC discrete): Wolfspeed C3M0032120K is a 1200 V 32 mΩ discrete SiC MOSFET in a TO-247-4 package, a common entry point for high-voltage prototypes and early power-stage validation.

Trend 2: Faster Edges Elevate Layout Parasitics to First-Order Effects

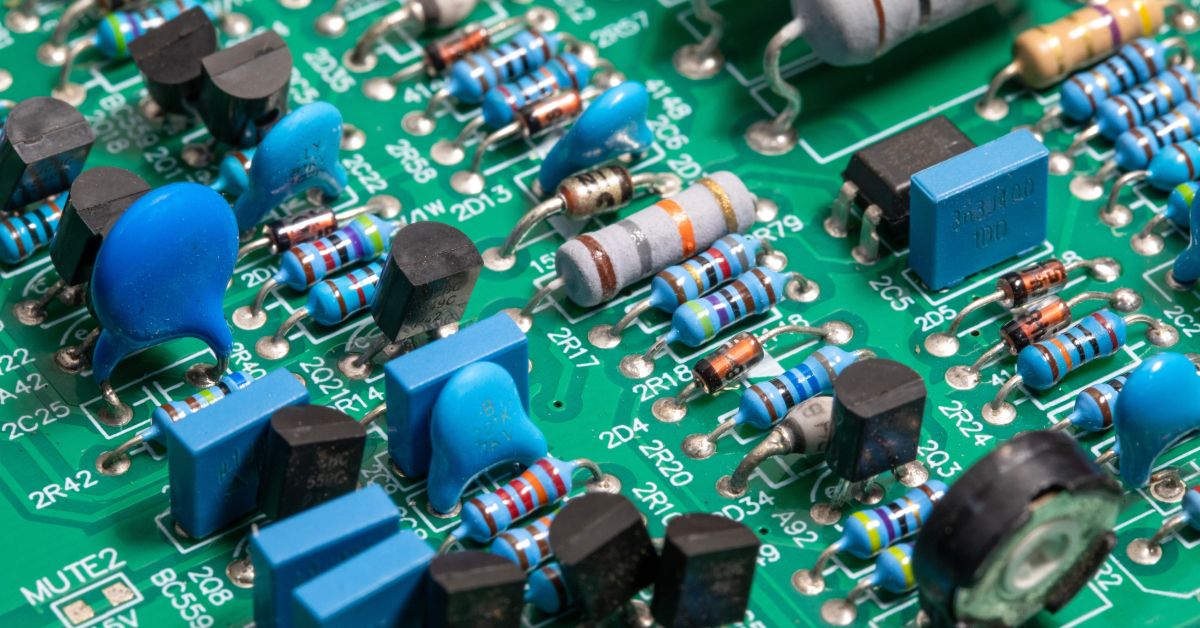

With SiC and GaN, the “layout tax” is no longer marginal. Gate-loop inductance, commutation-loop inductance, and switch-node capacitance show up as measurable overshoot, ringing, EMI, and false turn-on events. First-spin issues often trace to three factors: gate-loop geometry, DC-link capacitor placement, and switch node copper area.

Practical consequences:

- Driver placement becomes a layout constraint.

- Local DC-link decoupling becomes a mechanical packaging challenge.

- You need tuning flexibility baked into the board, including gate resistor options, snubber pads, and ferrite placeholders.

Example product (GaN reference hardware): EPC91107KIT is a 5 kW 4-level totem-pole power factor correction (PFC) evaluation board featuring EPC2304 GaN FETs. It’s a useful real-world reference for high-speed switching layout and loop control at kilowatt-class power, where loop inductance, thermal rise, and EMI trade-offs show up quickly.

Trend 3: Isolation is Now a Performance Spec

Isolation decisions used to be a compliance checkbox, but wide-bandgap edges changed that. Now, the isolation barrier must withstand both safety requirements and aggressive common-mode transients without corrupting control signals or triggering spurious protection events.

Board-level implications:

- Isolation components should be specified by working voltage, insulation class, and transient behavior.

- Common-mode transient immunity (CMTI) specifications need to align with actual switching edge rates, not idealized datasheet specs.

Example product (isolated gate driver): TI’s UCC21750 is a 5.7 kVrms, ±10 A single-channel isolated gate driver with desaturation protection and an internal Miller clamp, intended for insulated-gate bipolar transistor (IGBT) and SiC gate-drive applications where fast voltage change over time (dV/dt) is expected.

Trend 4: Current Sensing Is More Important and Challenging

As switching speeds increase, current measurement becomes a battlefield. Control loop quality, protection response, and efficiency optimization all depend on trustworthy sensing. Even when the sensor is “right,” placement and return-path errors can turn your measurement into a proxy for switching artifacts.

Practical consequences:

- Kelvin routing and reference integrity are as critical as sensor type.

- Bandwidth requirements increase for fast protection and control, raising noise susceptibility.

- Isolation choice is part of the measurement chain.

Example product (shunt-based isolated sensing): TI’s AMC1306 reinforced isolated current sensing modulator family offers precision current sensing reinforced isolated delta-sigma modulators intended for use with low-value shunts.

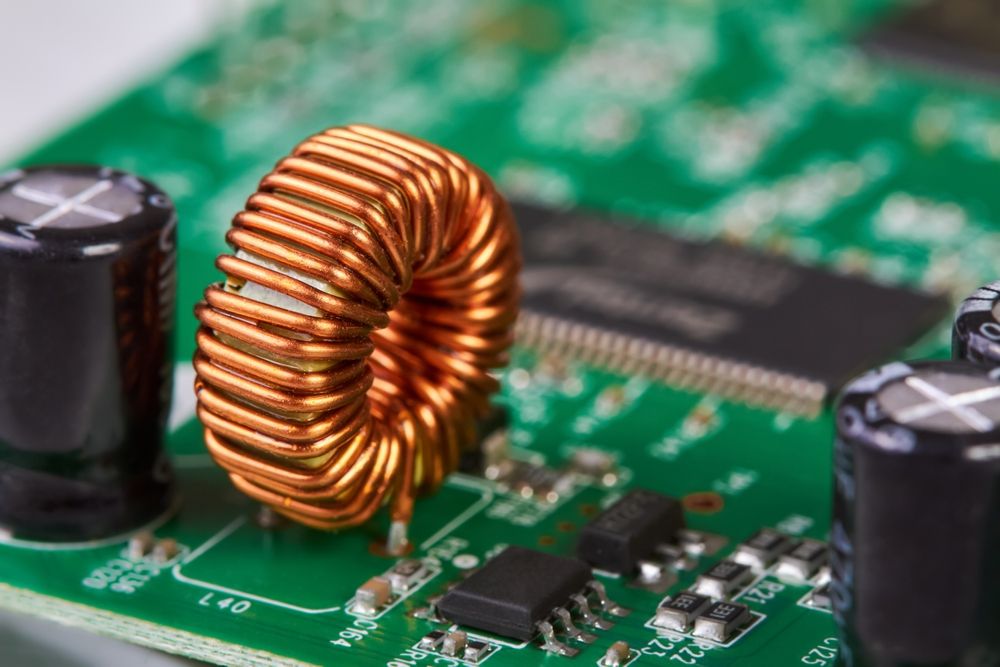

Trend 5: EMI Containment Shifts Upstream Into Architecture

Wide-bandgap designs often fail EMI late because teams treat emissions as a filter problem rather than a switching geometry problem. Filters still matter, but they work best when the source of noise is already controlled.

The board-level consequences include:

- Partitioning becomes architectural: Keep high current slew-rate loops (di/dt) physically separated from sensitive control regions.

- The switch node acts as a radiator: It needs to be minimized, intentionally routed, and isolated from low-noise nets.

- Input filtering becomes a co-design exercise with layout: Place filter parts tight to the entry path and close the return loop.

Example product (EMI suppression at the power entry): Würth Elektronik WE-CMB is a family of common-mode power line chokes with wide inductance and current options. They provide a typical building block in mains-side conducted EMI filters that becomes more critical as edge rates rise.

Trend 6: Packaging Evolution Drives Design Decisions

More vendors are pushing scale transitions – including 200 mm SiC milestones and 200 mm GaN-on-silicon partnerships – which can influence cost curves and sourcing strategies. In addition, packaging is increasingly the enabler for performance and manufacturability. Modules reduce stray inductance, simplify thermal design, and cut assembly variability. They also force early footprint commitment, which makes alternates planning and a second-sourcing strategy part of layout planning.

Example product (SiC power module): Wolfspeed’s CCB021M12FM3T is a 1200 V six-pack (three-phase) SiC power module with pre-applied thermal interface material (TIM), a packaging move aimed at repeatable assembly and thermal consistency.

What This All Means for 2026 Designs

Board-level constraints decide whether you hit performance targets and pass compliance without schedule pain. Three habits separate single-iteration teams from those requiring multiple spins:

- Lock the Physical Architecture Early: Resolve driver placement, local decoupling strategy, and the isolation boundary before you call the schematic complete.

- Design for Tuning: Plan for gate resistors, snubbers, and optional damping parts. Reserve space for measurement points that do not inject their own parasitics.

- Standardize and De-Risk: Select a reusable ecosystem of drivers, isolators, and sensors. Identify alternates that preserve footprint and key ratings.

The underlying theme is that wide-bandgap is a system build. Switch choice, driver behavior, barrier performance, measurement integrity, and layout all interact on every transition. Treat them as one design unit and the project becomes easier to validate and easier to repeat.

For insights into the spec decisions behind these habits, see What to Spec Around Wide-Bandgap Switches.

Wide-Bandgap Power: Frequently Asked Questions

When should I reach for SiC vs GaN?

SiC dominates as voltage and power increase, particularly in 1200 V applications and harsh thermal environments. GaN excels when switching speed and density drive the design, typically in AC-DC and DC-DC stages that benefit from higher-frequency operation.

What is the most common first-spin failure mode?

Layout-driven transients that trigger EMI failures, false turn-on, or protection chatter. These issues typically trace to commutation loop inductance, gate loop inductance, or excessive switch-node area.

Which spec is most often overlooked on the control side?

Isolation behavior under fast common-mode transients. If you do not align CMTI and barrier parasitics with your actual edge rates, the control chain can fail even when the power stage “works.”