PCB Via Size and Pad Size Guidelines

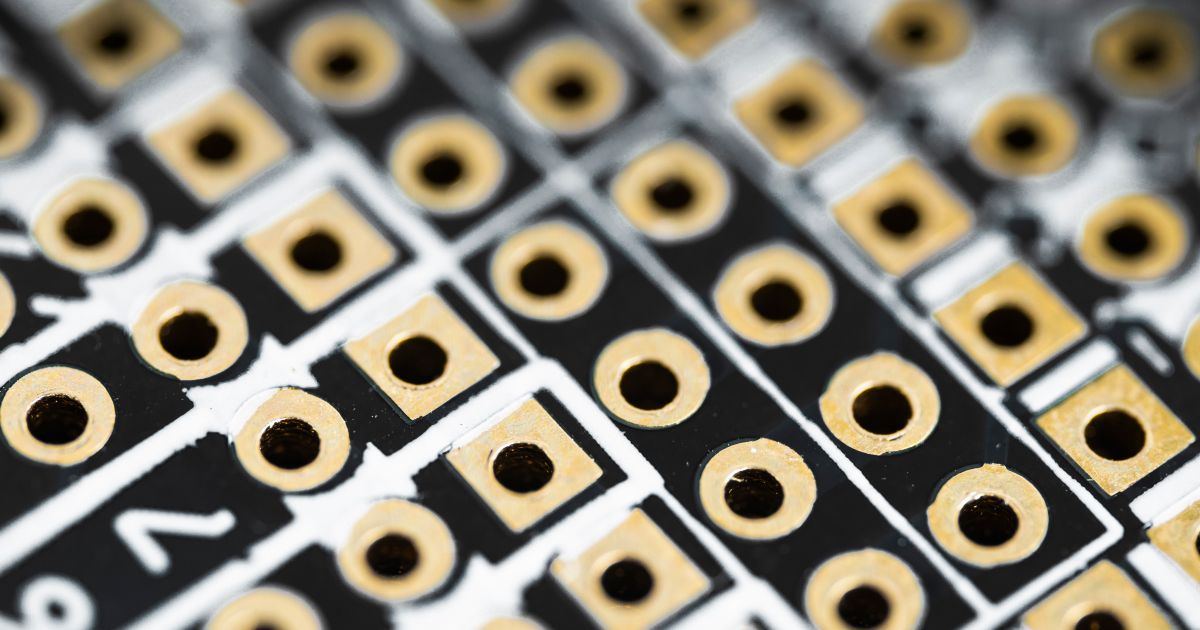

There are some aspects of PCB design and layout that seem deceptively simple, and yet they have a complex answer that is related to many important aspects of manufacturing. One of these design aspects is the match between PCB via size and pad size. Obviously, these two points are related; all PCB vias have (or should have) a landing pad that supports the via and provides a place to route traces into a via pad. However, there are some important sizing guidelines to follow when matching pad and via sizes, and this match is an important element of DFM and reliability.

The pad size you choose for your design relates to another important design aspect that is found during manufacturing, known as annular rings. Under the IPC standards, lands for PCB vias are related to the layer count, via hole size, and plating thickness, and the land should be sized so that the annular ring produced during production is sufficiently large. This is one area where it’s difficult to find concrete answers beyond just an answer to “what is an annular ring?” We’ll look at the answer and how it relates to two important IPC standards in this article.

PCB Standard Via Sizes and Pad Size Basics

Every via should have a landing pad on the surface layers where traces can make an electrical connection; the question is how large the via pad needs to be. When selecting an appropriate land size for a via, there are a few places to start looking:

- Manufacturing cost: Opting for a larger via is going to carry lower manufacturing costs, as I’ve discussed in an older article on cost estimates. Larger PCB vias will then require larger pad sizes.

- Trace width: It’s generally accepted that the pad size should be somewhat larger than the via size. Therefore, if you’re using a large trace width, such as a large controlled impedance trace, you’ll want a larger pad size. Note that this doesn’t also require a large via.

- Reliability: Larger lands will be more reliable, and as we’ll see, that is the entire point of this article… The IPC standards have plenty to say about this and will determine whether a given drill hit produces a defect in a via pad.

- Via type and layer count: As we’ll see below, the layer count will also contribute to pad size once the layer count exceeds 8 layers under IPC-2221.

With this in mind, I like to start by picking the via size that will be used throughout most of the board. Then, I’ll size the landing pad so that it hits a particular IPC Class requirement. This is where we need to consider the annular ring size that gets left in the board during manufacturing.

Size Pads Based on Annular Rings

In what follows, we’ll consider plated through-hole vias on rigid PCBs. For other types of PCBs, like flex or HDI design, we have different standards on annular rings that might be used to calculate via size. Take a look at the final section in this article to see some other standards governing PCB layout and performance qualification.

If we look at the IPC-2221 standards, there is a simple definition of annular rings that applies to external lands and internal lands. Some designers will use the term “annular ring,” “land,” “pad,” and other terms interchangeably. These definitions are shown in the graphic below, or you can find these in IPC-2221A Section 9.1.2:

You can download the IPC-2221 standards document from this link. If you want to go with the more recent IPC-6012 standards, you can download it from this link.

Here, we have two definitions for annular ring: the distance from the finished hole wall to the edge of the pad (external layers), or the distance from the drill hole wall to the edge of the pad (internal layers). When the PCB is passing through fabrication, it will be drilled after the etching process. Due to wander in a CNC drill, there is a chance that the drill does not hit dead center in the via pad. As a result, there will be some leftover annular ring as shown above. Therefore, the pad size on your PCB vias should, at minimum, be large enough to accommodate any drill wander and leave enough copper leftover to ensure the minimum annular ring shown above is accommodated and does not produce a defect. If the limits discussed in the tables and image below are violated, then that particular via may be counted as a defect and the board could be scrapped as a result.

This sizing involves an equation found in the IPC-2221 and IPC-6012 standards. The minimum via pad diameter is:

L = a + 2b + c

Where:

- a = Diameter of the finished hole (external layers) or diameter of the drill hole (internal layers)

- b = Minimum annular ring size (See above)

- c = Minimum standard fabrication allowance for interconnect lands (see the table below)

The minimum annular ring sizes as defined in the IPC-2221 and IPC-6012 standards are shown in the table below.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Finally, we have the following fabrication allowances that are used in the above formula:

|

|

|

|

|

|

|

|

*For IPC-2221: Add 20 mils if greater than 8 layers, or per oz. when copper weight is greater than 1 oz./sq. ft. These additions are ignored in the more modern IPC-6012 standard.

The IPC-A-600 and IPC-6012 standards are typically invoked for inspection criteria in PCB manufacturing rather than IPC-2221. This does not invalidate IPC-2221, it’s just that the IPC-6012 standard is a more modern standard that compiles important data from IPC 2221, IPC 4101, and other quality requirements. The goal in applying the above formula and setting fabrication limits is to eliminate the possibility of breakout. This is shown in the image below, where the drill hole lies partially off the edge of the pad. If the trace is very thin and the pad size is too small, drill wander could cause the drill hit to sever the connection between the pad and trace.

To prevent breakout in a Class 2 product, we instead aim for tangency (see above image), where we can set b = 0 in the above formula for the annular ring size.

This all leads to one useful guideline:

- To help prevent severing the trace from the pad, you can opt for an oversized pad with a drill hole diameter that is less than the trace width. If this is not possible, apply teardrops to the trace-to-pad connection to prevent breakout.

Fabricators generally aim for Class C, which is the finest fabrication tolerance limit in PCB manufacturing, so the Class A and B values generally aren’t used. This should reinforce the role of IPC standards; they don’t tell you how to design a PCB or what specific pad size to use. Instead, these guidelines state what qualifies as successful fabrication, and the design and manufacturing teams have to work to achieve those goals.

So with all this data, what’s the best way to ensure manufacturability and reliability? My view is, if you’re not worried about the annular ring size, then go with the Class 2 requirement. This means the pad size will be the diameter you put into your design tools, plus the fabrication allowance. In other words, you’re just taking b = plating thickness for external layers and b = 0 for internal layers. In the case of Class 3, the pad size needs to be just a bit larger and we need to consider the 2 mil requirement using the finished plating diameter to the pad.

Example: 10 mil Drill Hole, Class C Fabrication Allowance

Suppose we have a 10 mil drill hole for a via that we want to comply with IPC Class 3. If the via is plated up to the minimum under thickness in the hole wall (1 mil), we can now use the Class C fabrication allowance to determine the required pad size.

For a 10 mil drill hole diameter, we would have an 8 mil finished hole size with a minimum pad diameter of 20 mils on all layers. This calculation uses:

- a = 8 mil for external layers, 10 mil for internal layers

- b = 2 mil externally, 1 mil internally

- c = 8 mil on all layers

If we want to design to Class 2, then we should just use b = plating thickness (assume 1 mil for safety) on external layers and b = 0 in internal layers, meaning we would have a 18 mil diameter pad on all layers for a 10 mil drill hole with 1 mil via wall plating. For Class 2, just use L = hole + 8 mils on all PCB vias just to be safe; I would do the same on Class 1. This will also be the easiest way to define your via placements as you route without defining a custom padstack.

Beyond Through-Holes and IPC-2221/IPC-6012

The above list of requirements was only derived for through-hole vias rigid PCBs, which will be the dominant via style in most PCBs. If blind vias or buried vias are used, the requirements on annular rings will be different, and they will depend on the fabrication process (laser drilling vs. mechanical drilling). Once PCB vias get small enough to be considered microvias and are using HDI fabrication processes, you’ll have a different set of requirements governing annular ring limits and pad sizes.

The IPC-2221 standards and IPC-6012 standards are the basic standards that are most often cited for rigid PCBs, but there are other standards that are specific to different types of boards. These standards expand on the general design guidelines and standards in IPC-2220/2221 for applications like high frequency boards, HDI design, flex and rigid-flex PCBs, and other types of boards. These designs will carry many other manufacturability concerns

When you need to enforce PCB via size and pad size requirements during routing, use the complete set of routing features in Altium Develop. The integrated manufacturing tools and the Draftsman utility will automatically create the documentation you need to ensure performance requirements for your product are reflected in your fabrication instructions, including an accurate drill table that specifies drill sizes. When you’ve finished your design, and you want to release files to your manufacturer, Altium Develop makes it easy to collaborate and share your projects.

Whether you need to build reliable power electronics or advanced digital systems, Altium Develop unites every discipline into one collaborative force. Free from silos. Free from limits. It’s where engineers, designers, and innovators work as one to co-create without constraints. Experience Altium Develop today!