How to Manage Power Integrity and EMI in Complex Multiboard Systems

Every multiboard assembly introduces a set of power delivery constraints that do not exist in single-board designs. The moment power crosses a connector or cable between boards, the PDN picks up additional series resistance, contact resistance, and loop inductance that degrade voltage regulation and raise the impedance seen by downstream loads. Designers who treat the interconnect as a transparent extension of the source board's power rail will find that transient voltage droops, conducted noise, and thermal issues at the connector become the dominant failure modes in the system.

The governing design problem is that a PDN optimized on one board cannot maintain its impedance profile across a physical boundary it was never designed to cross. Connectors and cables behave as lumped parasitic elements in the power path, and their impact scales with load current and switching frequency. Addressing this requires treating each board's power delivery as an independent design problem, sizing the interconnect for both DC and AC performance, and filtering at the boundary to prevent noise from propagating between boards.

Why Do Multiboard PCB Connections Fail?

Multiboard PCB assemblies introduce failure modes that do not exist in single-board designs. The physical separation between boards, the interconnects bridging them, and the division of power and signal domains across enclosures all create opportunities for degraded performance or outright noncompliance. Designers who treat each board as an isolated design problem and then bolt them together with connectors or cables are routinely surprised when the integrated system fails EMC testing or exhibits intermittent functional errors.

The three most common categories of failure in multiboard connections are:

- Mechanical misalignment between connectors, flex circuits, or cable assemblies, resulting in intermittent contact, elevated resistance at mating interfaces, or outright open connections under vibration or thermal cycling.

- EMC failure originating from signal integrity problems, where impedance discontinuities, insufficient return paths, or excessive crosstalk at the board-to-board interface produce radiated emissions that exceed regulatory limits.

- EMC failure originating from power integrity problems, where noise on power rails conducts across the interconnect, couples into signal lines, or radiates from cables acting as unintentional antennas.

Mechanical issues are usually caught during prototyping and resolved with tolerance analysis or connector reselection. The EMC failures, however, tend to surface late in the development cycle during compliance testing, and they are far more expensive to fix because they often require layout changes, connector pinout revisions, or additional filtering that was not planned into the original design.

Signal Integrity and EMI at the Board-to-Board Interface

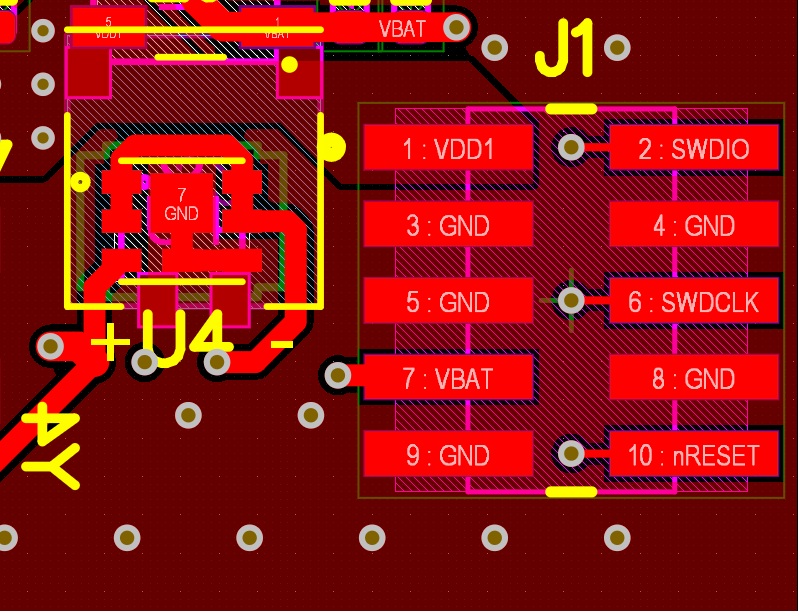

Whether the interconnect is a ribbon cable, a board-to-board connector, or a flex circuit, the mechanism linking signal integrity degradation to EMI failure is almost always the same: insufficient ground pin allocation. Every signal conductor in a multiboard interconnect needs a low-impedance return path physically adjacent to it. When ground pins are sparse or poorly distributed across the connector pinout, return currents are forced through long, inductive loops which will radiate.

At the same time, signals sharing distant return paths couple into each other, degrading signal quality and producing common-mode currents that drive emissions from the cable or connector housing. The interconnect can fail in two distinct ways: it can radiate emissions directly from the loop area formed between signal and return conductors, or it can conduct noise from one board to the other, where it then radiates from traces, planes, or I/O cables on the receiving board. Both mechanisms are common, and both are preventable with proper ground allocation and filtering at the connector interface.

Reducing EMI in Multiboard Interconnects

The following guidelines address the primary EMI risks at board-to-board interfaces. Each targets a specific coupling mechanism and should be applied during schematic and layout planning, not deferred to post-compliance remediation.

- Constrain return path loop area by ensuring every signal trace has an adjacent, uninterrupted ground reference on both sides of the interconnect. When a signal crosses from one board to another, its return current must follow a low-inductance path immediately adjacent to the signal conductor. Any gap or discontinuity in that path forces the return current into a wider loop, and loop area is directly proportional to radiated emissions.

- Interleave ground pins in the connector pinout rather than grouping all signals on one side and grounds on the other. A signal-to-ground ratio of 1:1 is preferred for high-speed interfaces; 2:1 is a practical minimum for moderate-speed connections. Distributing ground pins throughout the pinout provides each signal with a nearby, low-impedance return and reduces crosstalk between adjacent signal pins.

- Route differential pairs as true pairs through the interconnect, maintaining consistent spacing and symmetry from transmitter to receiver. The field cancellation that makes differential signaling effective only works when the two conductors are balanced in impedance and physical geometry across the entire path, including through the connector or cable.

- Bond the chassis ground to the PCB ground at defined, low-impedance points within the enclosure. In multiboard housings, the enclosure itself can serve as a shielding structure, but only if the ground bond impedance is low enough at the frequencies of concern. A single-point chassis bond with a long wire is ineffective above a few megahertz; multiple short bonds distributed around the enclosure perimeter are needed to contain radiated emissions.

These guidelines reduce risk, but they do not guarantee compliance. Multiboard systems have interaction effects that are difficult to predict from analysis of individual boards alone. Two boards that each pass radiated emissions testing independently can fail as an assembly once interconnected, because the cable or connector introduces new common-mode current paths and new antenna structures. Pre-compliance scanning of the integrated assembly, followed by formal EMC testing, is always necessary to verify that the combined system meets applicable radio emissions standards.

Power Integrity in Multi-Board Connections

Multiboard power delivery requires distinct AC and DC design strategies. High-speed AC power integrity relies on minimizing impedance by placing voltage regulators on the same board as their IC loads. Routing regulated power through cables or connectors adds inductance and resistance that decoupling capacitors cannot fully offset. Consequently, regulators should be placed locally, with only bulk DC or intermediate bus voltages crossing board-to-board interfaces.

DC power integrity, by contrast, is concerned with resistive voltage drop, current-carrying capacity of conductors and connector pins, and thermal limits under sustained load. Both AC and DC power paths through an interconnect can also act as carriers of conducted emissions. Switching noise from a regulator on one board can conduct through the cable to the second board, where it couples into sensitive circuits or radiates from traces and planes. Filtering at the interconnect boundary, on both the source and load sides, is often necessary to contain conducted emissions and prevent them from becoming radiated emissions downstream.

|

Design Parameter |

Selection Criteria |

|

Pin current rating and number of power pins |

Total load current divided across available pins, derated for temperature rise at the connector |

|

Connector contact resistance and cable gauge |

Acceptable DC drop under maximum load, verified against regulator dropout or tolerance budget |

|

Spacing and dielectric between power and signal pins |

Sufficient clearance to prevent arcing or leakage at the maximum working voltage, per IPC-2221 |

|

Filter placement at connector boundary |

Common-mode and differential-mode filtering sized for the noise spectrum of the upstream regulator |

|

Connector and cable temperature rise |

Sustained current must not exceed the temperature rating of the connector housing or cable insulation |

|

Number and distribution of ground pins for power return |

Sufficient ground pins adjacent to power pins to minimize loop inductance in the power delivery path |

Two IPC standards govern the DC power integrity aspects of conductor and connection sizing. IPC-2221 provides the spacing requirements for creepage and clearance between conductors at different voltage potentials, which directly applies to power pin spacing in connectors and to trace-to-trace clearance on the PCB near power entry points. IPC-2152 addresses current-carrying capacity of PCB conductors, providing the data needed to size traces, pours, and vias so that the design stays within its allowable temperature rise under sustained DC load. Relying on older rules of thumb for trace width versus current, rather than the thermal modeling approach in IPC-2152, frequently results in undersized conductors that overheat in enclosed multiboard assemblies where airflow is restricted.

Designing the PDN for Each Board in a Multiboard Assembly

Each board in a multiboard system should be treated as an independent power delivery problem before the interconnect is designed. Sharing regulators across boards or assuming that a single bulk capacitor bank on one board will serve loads on another leads to PDN impedance profiles that cannot meet target impedance at the frequencies where the loads demand current.

- Treat each board's PDN as a separate design when the boards carry their own high-current digital loads. A shared regulator across a cable cannot maintain low impedance at the frequencies where an FPGA or SoC draws transient current. Each board should have its own regulation stage for any rail supplying fast-switching logic.

- Place voltage regulator modules physically close to the highest-current ICs on each board, particularly FPGAs and high-speed processors with large digital I/O banks. The inductance of even a few centimeters of trace between a VRM and its load can produce voltage droops that exceed the rail tolerance during fast transient events.

- Verify that each board's stackup provides sufficient plane capacitance for the frequency range between where discrete decoupling capacitors lose effectiveness and where the VRM begins to regulate. Thin dielectric between power and ground planes lowers the impedance in this mid-frequency range and reduces the number of discrete capacitors required.

- Size copper pours and power plane regions based on the actual current draw and the allowable temperature rise per IPC-2152, not based on default pour settings or visual coverage. In enclosed multiboard assemblies with limited convective cooling, undersized pours reach thermal limits faster than in single-board designs with open airflow.

A Complete PI and EMI Workflow that Prevents Disruptions

As boards become more complex, so do the manual tasks required to update multiboard PCBs and ensure that changes are managed among multiple stakeholders. However, engineers need not isolate their boards in order to catch PI issues and EMI.

Engineers can avoid the timely and costly reworks that arise, but must become more proactive at managing changes from various angles. With various factors to consider, from sourcing to mechanical design and manufacturing—upstream to downstream—a unified platform allows for greater communication between all departments.

Altium Develop incorporates all of the tools that engineers need to manage ECAD and MCAD designs, requirements and BOMs in one design-oriented environment to enable faster iterations and create more reliable links between engineers and sourcing teams. Combining the BOM Portal, Requirements Portal, and design capabilities gives them more visibility of external factors. Designers can see how component choices will impact their workflows, and vice versa. Get started with Altium Develop →

Frequently Asked Questions

What is power integrity in PCB?

In high-performance applications, power integrity (PI) compliance is vital to ensuring that every device on the network gets the exact voltage and energy it needs to function reliably and efficiently.

How do you maintain signal integrity?

Signal integrity is primarily managed by ensuring differential pair symmetry and impedance consistency. Both traces in a pair must match exactly in length and geometry to ensure signals arrive simultaneously and cancel out noise.

How do you control EMI?

To control EMI in a multiboard system, designers must ensure continuous return paths and use differential routing to cancel out electromagnetic fields before they radiate. By integrating these strategies early and utilizing shielded, interleaved connectors, you prevent interference.