Introduction to High Speed PCB Designing: Techniques for Avoiding Crosstalk

High-speed PCB designs can bring many challenges when certain guidelines are not followed. Some of the most important (and most common) high-speed design guidelines don't just ensure correct routing with low noise, they also help prevent crosstalk.

Crosstalk in PCBs is the unintentional electromagnetic coupling between traces. In other words, crosstalk occurs when a digital pulse on one trace induces a similar signal on the other trace, even though they are not physically touching each other. This can happen when the spacing between parallel traces in PCB is tight and the reference plane is far from the traces, or when there is no reference plane below two traces that are interfering. But with some very basic design techniques, you can solve many crosstalk problems.

What is Crosstalk in High-Speed PCB Design?

Crosstalk always occurs in PCBs, it is just a matter of determining whether that crosstalk is so great that you need to do something to solve the problem. Crosstalk occurs between two parallel traces running next to each other on the same layer. There is an even greater possibility, though, for crosstalk in PCB to occur between two parallel traces running next to each other on adjacent layers; this is called broadside coupling.

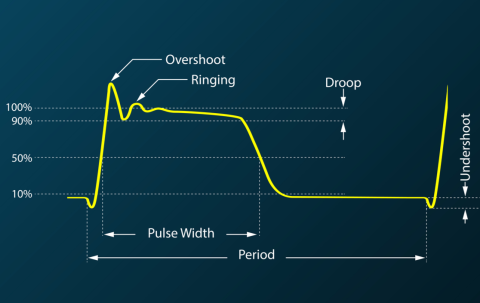

Consider two traces in PCB running parallel to each other. When the signal in one trace is switching (the "aggressor"), it will induce a voltage/current into the other trace. This induced signal will then be observed at the driver end (near-end crosstalk) and the receiver end (far-end crosstalk) of the victim interconnect. Even though the traces may be maintaining the minimum spacing for manufacturing purposes, they may not be enough for electromagnetic purposes. In general, when traces are closer together, you could have stronger crosstalk. This can be seen clearly in the example simulation results below.

As I've discussed in this other article on crosstalk, the strength of crosstalk depends on the aggressor signal's edge rate, not on data rate or clock rate.

The other point that introductory designers overlook is crosstalk between differential pairs, appropriately referred to as differential crosstalk. In general, differential pairs can create crosstalk into single-ended signals and into other differential pairs, despite myths that state otherwise. Because crosstalk occurs in linear networks, the phenomenon is reciprocal; single-ended signals can generate crosstalk into differential pairs.

Suppressing Crosstalk from Your High-Speed Design

While you can never totally eliminate crosstalk, there are simple steps you can take to reduce the intensity of any induced crosstalk so that it is less noticeable and does not create errors at I/Os on the victim line. Here is the main list of high-speed design techniques that will greatly suppress crosstalk:

-

Route digital signals over a continuous ground plane. In today's PCBs, this is a mandatory requirement anyways, regardless of whether your traces must be designed to a target impedance.

-

When the distance to ground is larger, your signals need to be spaced out by a larger distance. A conservative rule of thumb is gap = 3W (W = trace width).

-

When signals over a ground plane create too much crosstalk, bring ground closer to the signals. This might require a 4 layer board at minimum. Bringing ground closer to signals can also allow violation of the 3W rule.

-

Typically, you may need to increase the spacing between a clock line and a signal line in a source-synchronous bus so that you retain timing margins but minimize crosstalk. The same gap = 3W rule of thumb also works here.

-

Asynchronous signals or configuration signals (like RESET, INTERRUPT, ENABLE, etc.) may need to be routed away from high-speed buses. They can be routed next to on-and-off or power-up signals though because those signals are rarely used during the normal operation of the circuit board. They could also be filtered to help remove fast crosstalk pulses because they do not have a rise time requirement to toggle a pin, they can change slowly.

-

If routing signals on different signal layers, place a ground reference between these layers in order to shield the signal layers from each other.

-

If Rule #6 is not possible (such as in a 6-layer stackup with two internal signal layers). Try to carve out specific board regions for high-speed channels. If the board will fill with signals, use orthogonal routin (horizontal and vertical routing directions on different layers).

Within this list, Rule #1 is most important. It is the simplest and most effective design choice for a modern system that will help reduce crosstalk on a PCB. Following that, Rules #2 and #3 are equally important as they relate to the design of your stackup. This then brings up the question: what

How Do We Know if There is Too Much Crosstalk?

As I stated above, you will always have some crosstalk in a PCB, but many times you may not notice it is present. However, if there is a significant amount of crosstalk, how will you know if it is too much?

There are some simple ways to quickly determine if crosstalk will be a problem, and there are more complex evaluations that are typically required in standardized interfaces (such as Ethernet, Infiniband, serdes lanes, DDR, etc.). The simple method for determining if there is too much crosstalk is to look in the time domain. There are also signal integrity simulators that enable analysis of your high-speed design for potential crosstalk problems.

In the frequency domain, we would use an S-parameter mask to compare with the crosstalk we observe in a PCB signal integrity simulation. S-parameter masks basically provide an upper or lower limit on a particular signal integrity metric up to some frequency limit. For a standardized digital interface, the important point is to compare against the S-parameter limits defined by the mask, which can be inspected visually in a graph.

Whenever you need to design enclosures, wire harnesses, flex cabling, multi-board assemblies, or any other component in your electronic product, make sure you use the complete set of PCB design features in Altium Designer®. To implement collaboration in today’s cross-disciplinary environment, innovative companies are using the Altium 365™ platform to easily share design data and put projects into manufacturing.

We have only scratched the surface of what’s possible with Altium Designer on Altium 365. Start your free trial of Altium Designer + Altium 365 today.