Wytyczne dotyczące trasowania DDR3 i topologie trasowania

Bez pamięci ulotnej, komputer musiałby stale odczytywać i zapisywać dane do pamięci nieulotnej, takiej jak dyski twarde czy Flash. Pamięć nieulotna to jedna z rzeczy, która czyni nowoczesne komputery tak potężnymi i daje im zdolność adaptacji wymaganą do zaawansowanych zadań. Chociaż DDR3 jest obecnie przestarzałe, pamięć oparta na DDR pozostaje i nadal będzie odgrywać centralną rolę w nowoczesnej architekturze komputerowej. Posiadając odpowiednie narzędzia do projektowania, możesz projektować pamięci oparte na najnowszej generacji DDR i dalej. Zobacz, co

ALTIUM DESIGNER®

Standard branżowy w projektowaniu elektroniki dla wysokowydajnych PCB i architektury pamięci.

Pamięć o podwójnym szybkim transferze danych trzeciej generacji (DDR3) to typ dynamicznej pamięci o dostępie swobodnym (DRAM), która następuje po wcześniejszych generacjach DDR. Te pamięci osiągają prędkości zegara do 1066 MHz i obsługują do 24 GB pamięci. Wysoka prędkość zegara i duża pojemność przechowywania zapewniły, że DDR3 pozostało podstawą nowoczesnego przetwarzania, ale ostatecznie zostało ulepszone do DDR4. Każda nowa generacja nadal przesuwa granice szybkości transmisji danych i prędkości zegarów w szybkich PCB, a pamięci oparte na DDR prawdopodobnie nie zostaną szybko zastąpione przez nową architekturę.

Mając to na uwadze, projektanci pamięci muszą zaznajomić się z różnymi zasadami projektowania PCB dla pamięci opartych na DDR oraz jak te zasady są przesuwane do granic możliwości z DDR4. Projektanci powinni również być świadomi różnych topologii trasowania dla PCB, ponieważ implementacja nowych topologii poprawiła funkcjonalność pamięci opartych na DDR, w tym DDR3.

Praca z doskonałym pakietem projektowym PCB, jakim jest Altium Designer, pozwala inżynierom projektowym wdrażać najlepszą topologię trasowania dla poprawy wydajności DDR3, DDR4 oraz przyszłych generacji pamięci. Altium Designer zawiera narzędzia do projektowania, interaktywnego trasowania, analizy dostarczania energii i symulacji, które są potrzebne, aby zapewnić, że twoje projekty oparte na DDR pracują z maksymalną wydajnością.

Wytyczne projektowania trasowania i topologia dla trasowania DDR3

DDR3 używa topologii fly-by dla różnicowego zegara, adresu, komend i sygnałów sterujących. Początkowo DDR3 używało topologii T do łączenia banków pamięci z kontrolerem, ale wydajniejsze pamięci DDR3 używają topologii fly-by, aby poprawić kompatybilność z wysoko pojemnościowymi obciążeniami i architekturami układów scalonych.

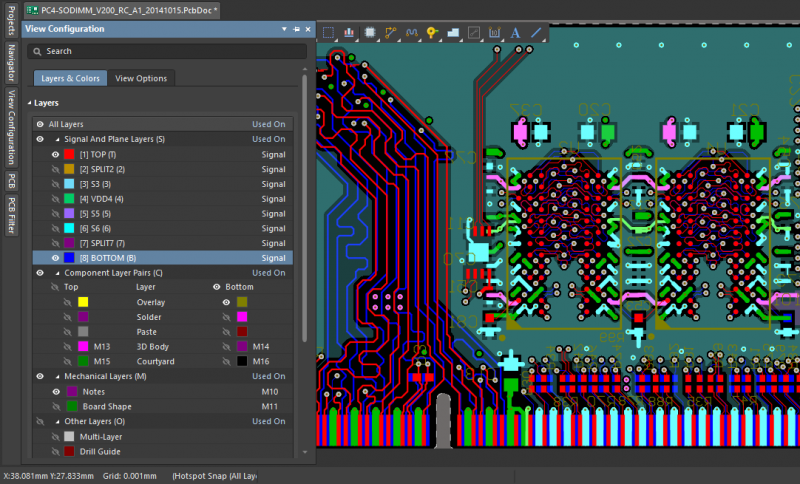

Implementacja odpowiedniej architektury dla DDR3 lub DDR4, jak również umieszczanie połączeń z pakietami die DDR SDRAM, wymaga elastycznych narzędzi trasowania, które nie ograniczają twojej topologii. Ścieżki sygnałowe są trasowane jako pary różnicowe i muszą być precyzyjnie dopasowane w ścisłych tolerancjach w porównaniu do innych standardów peryferyjnych komputera, takich jak PCIe.

Integralność sygnału w trasowaniu DDR3 i DDR4

Wiele standardowych zasad projektowania zapewniających integralność sygnału w innych urządzeniach ma również zastosowanie do DDR3 i nowszych. Wydajniejsze pamięci używają topologii fly-by, która wiąże się z konkretnymi wymaganiami. Ścieżki powinny być dopasowane długościowo z bardzo małymi tolerancjami, pary różnicowe powinny być ściśle sprzężone na tej samej warstwie, a długości odgałęzień do każdego urządzenia pamięciowego powinny być jak najkrótsze, aby zapobiec efektom linii transmisyjnej i rezonansowi w odgałęzieniu. Wszystkie sygnały w danej grupie torów powinny być trasowane na tej samej warstwie, ponieważ zapobiega to różnicom w opóźnieniach propagacji i skosom.

Aby zweryfikować skuteczność trasowania i układu na całej płycie, potrzebujesz narzędzi symulacyjnych, które bezpośrednio włączają dane Twojego projektu. Praca w narzędziu do integralności sygnału, które oblicza przebiegi fal odbitych i przeplot zapewnia, że Twoje projekty spełniają ważne standardy wydajności dla DDR3 i nowszych pamięci.

- Nie wszystkie topologie są intuicyjne, ale narzędzia trasowania w oprogramowaniu do projektowania PCB powinny ułatwić implementację potrzebnej topologii trasowania DDR3.

Dowiedz się więcej o implementacji topologii DDR3 w oprogramowaniu do projektowania PCB.

- Trasowanie pamięci DDR3 i procesorów nie musi być trudne, gdy pracujesz z odpowiednim oprogramowaniem do projektowania. Dowiedz się, jak trasować pamięci DDR3 i rozwidlenie wentylatora procesora w Altium Designer.

- Chociaż DDR3 jest przestarzałe, DDR4 ma się dobrze i wiele z tych samych pomysłów można zastosować do pamięci DDR4. Dowiedz się więcej o trasowaniu DDR4 dla urządzeń pamięciowych.

Konfiguracja układu projektowego dla urządzeń pamięciowych

Od DDR3 do DDR4 i dalej: czego się spodziewać

Wraz z przestarzałością pamięci DDR3 i zastąpieniem jej przez DDR4, a ostatecznie DDR5, projektanci mogą spodziewać się tylko, że wymagania dotyczące trasowania i topologia staną się bardziej skomplikowane. Prędkości sygnałów będą wzrastać, a topologia trasowania dla urządzeń pamięciowych na chipach nałoży nowe ograniczenia układu. Mając to na uwadze, potrzebujesz oprogramowania do projektowania, które jest dostosowalne do dowolnej topologii trasowania, jednocześnie pomagając Ci spełnić ważne ograniczenia projektowe.

Integralność sygnału jako część projektu

W przypadku każdego nowego układu wysokiej prędkości lub wysokiej częstotliwości, doskonałe narzędzie symulacyjne może pomóc Ci zdiagnozować potencjalne problemy z integralnością sygnału na całej płycie. Potencjalne problemy mogą pojawić się w dowolnym momencie Twojego układu, a odpowiednie narzędzia do integralności sygnału ułatwiają diagnozowanie przeplotów, określanie, gdzie wymagane jest zakończenie, oraz ustalanie, jak pasożyty wpływają na Twoją płytę. Możesz następnie testować potencjalne przeprojektowania i bezpośrednio porównywać wyniki podczas każdej iteracji.

- Układy DDR3 i DDR4 wymagają analizy dostarczania energii, aby zapewnić, że urządzenia pamięci otrzymują odpowiednie poziomy mocy i aby zapobiec powstawaniu punktów gorących wokół płytki.

Zobacz, jak możesz włączyć analizę dostarczania energii do swojego procesu projektowego.

- Gdy narzędzia symulacyjne są włączone do oprogramowania projektowego, możesz szybko weryfikować proponowane zmiany w projekcie i identyfikować problemy z integralnością sygnału, zanim zniszczą one funkcjonalność twojej płytki.

Dowiedz się więcej o włączaniu symulacji do procesu projektowania.

- Z DDR będącym tak popularną architekturą pamięci, jest wielu ekspertów gotowych zaoferować porady projektowe.Sprawdź te wskazówki dotyczące trasowania DDR, aby zapewnić integralność sygnału.

Integralność sygnału jako część projektowania w Altium Designer

Altium Designer: Unifikacja funkcji projektowania i weryfikacji

Ze względu na złożone wymagania stawiane pamięciom DDR, projektanci potrzebują programów, które ułatwiają fazę trasowania i układu, jednocześnie zapewniając, że ich projekt spełnia podstawowe standardy układu dla DDR3, DDR4 i dalszych. Gdy oprogramowanie projektowe jest oparte na silniku projektowym kierowanym regułami, funkcje projektowe będą sprawdzać układ względem standardów projektowych podczas budowania płytki. Narzędzia symulacyjne będą budować modele bezpośrednio z danych projektowych, i nie będziesz musiał przenosić danych między wieloma programami.

Projektowanie pamięci DDR w Altium Designer

Z Altium Designer uzyskasz dostęp do narzędzi do trasowania, symulacji i weryfikacji, których potrzebujesz do projektowania architektur pamięci DDR3, DDR4 i nowszych, spełniających lub przewyższających standardy projektowe. Tylko Altium Designer umieszcza te funkcje w jednym programie, podczas gdy inne platformy projektowe oddzielają te funkcje do różnych środowisk. Wszystko, czego potrzebujesz do projektowania DDR, znajdziesz w Altium Designer.

- Altium Designer umieszcza wszystkie ważne funkcje układu, trasowania, symulacji i weryfikacji dla projektowania DDR w jednym środowisku. Dowiedz się więcej o zintegrowanym środowisku projektowym Altium Designer.

- DDR3 i DDR4 to już architektury pamięci o wysokiej prędkości, a w kolejnych generacjach należy spodziewać się tylko wzrostu prędkości sygnalizacji i szybkości transferu danych. Dowiedz się więcej o projektowaniu wysokiej prędkości w Altium Designer.

- Złożoność architektury i trasowania opartej na DDR wymaga od projektantów narzędzi do trasowania, które pomagają automatyzować proces trasowania, jednocześnie pozostawiając kontrolę nad układem. Dowiedz się więcej o auto-interaktywnym trasowaniu w Altium Designer.

Inne platformy oprogramowania do projektowania PCB dzielą te ważne funkcje projektowe na różne programy. Z Altium Designer uzyskasz dostęp do najlepszych funkcji trasowania i układu topologii w jednej platformie. Altium zapewnia również zasoby, które gwarantują Twój sukces. Będziesz miał natychmiastowy dostęp do podcastów i webinarów z ekspertami branżowymi, forum AltiumLive, obszerną bazę wiedzy oraz samouczki projektowe.

Zamiast utknąć z nową wersją przestarzałego oprogramowania do projektowania, spróbuj pracować w zintegrowanym środowisku projektowym Altium Designer. Będziesz miał dostęp do narzędzi, których potrzebujesz do trasowania i układu DDR w jednym środowisku. Będziesz mógł pozostać na czele projektowania DDR, korzystając z Altium Designer.