Vor- und Nachteile von orthogonalen Leiterbahnenführungen in mehrlagigen Leiterplatten

Ich sehe gelegentlich Fragen in Foren, einige Blogbeiträge und sogar Anwendungshinweise, die weiterhin die Verwendung von orthogonalem Routing empfehlen, üblicherweise bei 2-6 Lagen Platinen. Wenn ich mir Anwendungshinweise anschaue, neige ich dazu, mich standardmäßig an die Ratschläge von Rick Hartley zu halten und versuche, über diesen Rat im Kontext nachzudenken. Leider werden Empfehlungen in Anwendungshinweisen nicht immer mit der nötigen Skepsis betrachtet und sie werden oft in Situationen angewendet, in denen sie nicht zutreffen.

Dieser Artikel handelt mehr davon, wann man orthogonales Leiterbahnen-Routing nicht verwenden sollte, anstatt darüber, wie es in einem Autorouter oder einem ähnlichen Thema konfiguriert werden kann. Wenn Sie lange Zeit im Bereich der ultra-hohen Geschwindigkeiten/Hochfrequenz gearbeitet haben, dann ist dies für Sie wahrscheinlich nichts Neues. Für den Rest von uns gibt es die Versuchung, auf alte Informationen zurückzugreifen, die oft ohne Kontext bereitgestellt werden. Dies gilt insbesondere für orthogonales Leiterbahnen-Routing.

Schlechte Stackups führen zu Übersprechen beim Routing

Ich denke, das erste Mal, dass ich eine Empfehlung sah, dass Designer orthogonales Routing verwenden sollten, war auf StackExchange. Diese Website ist eine ausgezeichnete Ressource zu vielen Themen und definitiv meine erste Anlaufstelle für alles, was mit Software und Programmierung zu tun hat. Mit der zunehmenden Komplexität von Elektronik und PCB-Design ist es leicht, Empfehlungen von dieser und anderen Seiten anzuwenden, ohne den Kontext zu berücksichtigen, was dazu führen kann, dass diese Designentscheidungen dazu führen, dass eine Platine versagt.

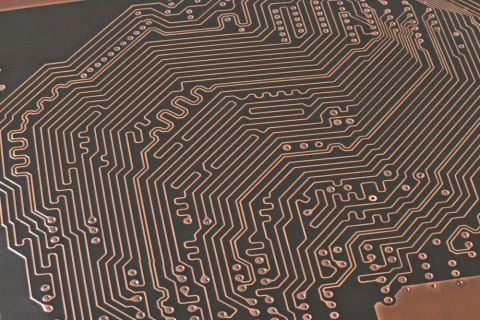

Ich hatte kürzlich einen Kunden, der Hilfe bei der Fehlersuche bei einem Upgrade eines älteren Designs suchte. Der Kunde entschied sich, die klassische Empfehlung für orthogonales Trace-Routing mit dem unten gezeigten 6-Lagen-Stackup zu verwenden. In diesem Stackup sind die zwei obersten und die zwei untersten Lagen Signallagen. Die Traces in diesen Lagen wurden orthogonal zwischen ICs geroutet, und für den Schichtwechsel wurden standardmäßige Durchkontaktierungen verwendet.

Verwenden Sie diesen einfachen 6-Lagen-Stackup nicht bei Hochgeschwindigkeitssignalen...

Der erfahrene Designer sollte bereits eine Vorstellung davon haben, was an diesem Bild falsch ist. Das Problem war, dass der Ingenieur versuchte, das Design zu verwenden eines neuen MCU zu aktualisieren, das mit 400 MHz und Hochgeschwindigkeitsschnittstellen läuft, aber ohne den Stackup zu ändern; das Design hatte übermäßiges Übersprechen und bestand die EMC-Tests nicht.

An diesem Punkt sollte die Lösung offensichtlich sein; gestalten Sie das Stackup ordnungsgemäß, und Sie müssen sich nicht ausschließlich auf orthogonales Routing verlassen, um die Signalintegrität bei der Arbeit mit hohen Flankensteilheiten zu gewährleisten. Wie sich herausstellte, handelte es sich dabei um ein Problem der Leistungsintegrität, das weniger mit orthogonalem Routing zu tun hat und mehr mit der Anordnung der Schichten. Dies wirft jedoch die Frage auf: Wann sollten Sie orthogonales Routing verwenden?

Wann ist orthogonales Trace-Routing anwendbar?

Orthogonales Routing wird in zwei möglichen Situationen verwendet:

- Um vertikale und horizontale Routingkanäle in verschiedenen Schichten auszuschneiden

- Um kapazitive Übersprechen zwischen benachbarten Schichten zu verhindern, indem der gekoppelte Bereich zwischen ihnen minimiert wird

Die erste Verwendung ist völlig angemessen, und es kann das Routing erheblich erleichtern, solange das Stackup korrekt entworfen ist (siehe unten).

Bezüglich der Signalintegrität haben Sie die folgenden fortschreitend schwierigen Übersprechprobleme, wenn Sie orthogonales Routing zwischen zwei benachbarten Signallagen verwenden:

- Bei niedrigen Flankensteilheiten wird es ohnehin weniger Übersprechen geben, auch in benachbarten Signallagen (gilt für UART, I2C usw.)

- Bei schnelleren Flankensteilheiten (wie bei SPI) können Sie Übersprechen in fortschrittlicheren Chips bemerken

- Bei differentiellen Paaren wird das Übersprechen differentiell sein, was bei einem Empfänger nicht aufgehoben werden kann

- Bei sehr schnellen Flankensteilheiten (sub-ns) werden Sie mehr Übersprechen und abgestrahlte Emissionen feststellen

Wie soll das für die Signalintegrität funktionieren? Wenn ein aggressives Digitalsignal sich ausbreitet, erzeugt es ein magnetisches Feld, und die Schaltflanken des Signals erzeugen einen sich ändernden magnetischen Fluss in der Umgebung der Leiterbahn; dies ist induktives Übersprechen. Es gibt auch ein elektrisches Feld zwischen den beiden Leitungen; wenn das aggressive Signal schaltet, induziert es einen Verschiebungsstrom in der Opferleitung; dies ist kapazitives Übersprechen.

Wenn Verbindungen auf benachbarten Schichten orthogonal (entlang senkrechter Richtungen) verlegt werden, ist das Magnetfeld von einer Leiterbahn immer parallel zur Leiterschleife ausgerichtet, die von einer beeinträchtigten Leiterbahn auf der nächsten Schicht gebildet wird, und eliminiert so effektiv direkte induktive Übersprechen. Obwohl diese Beschreibung technisch korrekt ist, ist sie übermäßig vereinfacht und berücksichtigt nicht andere wichtige Aspekte eines realen PCB-Stackups und Layouts. Die Hauptprobleme, die mit der orthogonalen Verlegung zusammenhängen, beziehen sich auf die Schaltgeschwindigkeit, Entkopplung und die Definition eines zuverlässigen Rückführungspfads. Rick Hartley diskutiert einige dieser wichtigen Verlegungs- und Stackup-Aspekte in einem kürzlichen Interview.

Trotz des Mangels an induktiver Kopplung gibt es immer noch kapazitive Kopplung, selbst mit der kleinen Schnittfläche zwischen den Leiterbahnen. Wenn Sie Ihren Rückführungspfad nicht ordnungsgemäß entworfen haben, kann das elektrische Feld zwischen Signallayer 1 und seinem Ground (siehe das obige Bild) einfach aufgrund eines Potenzialunterschieds über ihre gegenseitige Kapazität zu Signalen in Layer 2 zurückkoppeln und so kapazitives Übersprechen erzeugen. Die Impedanz, die vom kapazitiv gekoppelten Signal gesehen wird, ist niedriger, wenn die Signalflankenrate schneller ist, was einen stärkeren Stromimpuls in der beeinträchtigten Leiterbahn erzeugt.

Fortgeschrittene Designs wie dieses verwenden keine orthogonale Leiterbahnverlegung.

Bei niedrigeren Flankensteilheiten werden Sie wahrscheinlich keine kapazitive Übersprechen bemerken, unabhängig davon, ob orthogonales Routing verwendet wird. Es wird immer noch auftreten, aber es ist möglicherweise nicht ausreichend groß, um die Rauschmarge irgendwelcher mit Opferleitungen verbundenen Komponenten zu durchbrechen. Bei niedriger Geschwindigkeit sehen induktiv gekoppelte Signale eine niedrigere Impedanz, daher würden Sie orthogonales Routing auf benachbarten Signallagen verwenden wollen, um die induktive Kopplung zu minimieren. Mit niedrigen Flankensteilheiten zu arbeiten, ist ein Beispiel, bei dem orthogonales Leiterbahnrouting in benachbarten Signallagen angebracht ist. Für den Rest von uns arbeiten wir normalerweise unter einer Nanosekunde in Bezug auf die Flankensteilheit, was eine sorgfältige Abschirmung/Isolation zwischen den Signallagen, einen sorgfältig entwickelten Rückkehrpfad und ultrastabile Stromversorgung erfordert. Alles hängt vom Entwerfen des richtigen PCB-Stackups ab.

Orthogonal routen, aber Masse verwenden

Die Quintessenz hier ist einfach: Orthogonales Routing ist keine Lösung für Probleme mit der Signalintegrität, speziell Übersprechen bei schnellen Flankensteilheiten. Jedoch ist orthogonales Routing sehr nützlich, einfach um Kanäle zwischen Gruppen von Komponenten zu schaffen. Um es richtig zu verwenden, muss der Stackup Masse haben, die die zwei Signallagen trennt.

Im folgenden Beispiel zeige ich eines unserer älteren Mehrlagen-Designs mit einer Signallage auf der äußeren Oberfläche. L2 ist Masse und L3 enthält den orthogonalen Routing-Kanal. Zusammen schafft diese Art des Routings in zwei senkrechten Richtungen eine Schnellstraße für Ihre Routen in verschiedenen Lagen. Das Routing ist sehr sauber, da es in zwei verschiedene Kanäle unterteilt ist, die leicht über Durchkontaktierungen, die von Komponenten auf beiden Seiten der Platine ausgehen, zugänglich sind. Dies erleichtert das Routing zwischen dem zentralen MCU und dem RAM-Chip oben auf der Platine.

Der Stapelaufbau ist unten dargestellt. Dieser Stapelaufbau verwendet zwei interne Signallagen, aber L4 wurde für Steuerpins und Stromschienen vorgesehen. Beachten Sie, dass Sie denselben Routing-Stil auf einer 4-Lagen-Platine mit zwei internen Masseebenen implementieren könnten. Die Hauptleitlinie hier ist, dass orthogonales Routing in Ordnung ist, solange Masse die beiden Signallagen trennt.

Dies legt den Schwerpunkt auf intelligente Bauteilplatzierung im PCB-Layout, insbesondere bei Steckverbindern. Allerdings hat man nicht immer die Freiheit, Steckverbinder zu platzieren, wo man möchte. In einem echten Produkt können Sie durch Kabel, die in das Gehäuse eintreten, andere Platinen im Gehäuse, ungewöhnliche Pinbelegungen bei Bauteilen und ungewöhnliche Pinbelegungen bei Steckverbindern eingeschränkt sein. Das Problem mit den Steckverbindern ist wahrscheinlich die größte Herausforderung, da es das Routing ernsthaft einschränken kann, insbesondere wenn die Pinbelegung standardisiert ist oder wenn die Pinbelegung durch ein anderes Produkt eingeschränkt wird. In diesem Fall mit Steckverbindern, wenn Sie die Kontrolle über die Pinbelegung durch individuelles Kabel-/Kabelbaumdesign erlangen können, können Sie eine orthogonale Routingstrategie leichter umsetzen.

Die Routing- und Lagenstapel-Designfunktionen in Altium Designer® sind die erste Wahl für die Erstellung Ihrer Platine und Ihres Layouts. Der regelbasierte Designmotor bietet Rückwegprüfung und andere wichtige DRCs, während Sie Ihr Layout erstellen. Sie werden in der Lage sein, PCBs höchster Qualität für jede Anwendung zu entwerfen. Sie können auch verschiedene Aspekte des Signalverhaltens mit den Post-Layout-Simulationstools in Altium Designer simulieren.

Jetzt können Sie eine kostenlose Testversion von Altium Designer herunterladen und mehr über die branchenführenden Layout-, Simulations- und Produktionsplanungswerkzeuge erfahren. Sprechen Sie noch heute mit einem Altium-Experten, um mehr zu erfahren.