HDI vs. Ultra HDI: Was PCB-Designer in der Fertigung beachten müssen

Die HDI-Technologie (High Density Interconnect) ist seit Jahren ein fester Bestandteil des hochdichten PCB-Designs und der Leiterplattenfertigung . Die meisten Entwickler sind mit Microvias, sequentieller Laminierung sowie den Leiterbahn- und Abstandsgrenzen subtraktiver Ätzprozesse in der PCB-Fertigung vertraut. Was früher sowohl für Entwickler als auch für Fertiger wie eine steile Lernkurve wirkte, ist heute eher eine Frage der Umsetzung als der Prozessentwicklung.

Heute entwickelt sich „Ultra HDI“ zu einem neuen Paradigma in der ultrafeinen Leiterplattenfertigung und im fortschrittlichen Interconnect-Design – mit einer steilen Lernkurve für Entwickler und Fertiger gleichermaßen. Auf den ersten Blick könnte es so wirken, als sei Ultra HDI lediglich eine Weiterentwicklung der HDI-Technologie.

Ultra HDI unterscheidet sich von standardmäßigem HDI jedoch nicht nur durch kleinere Strukturgrößen, sondern auch durch den Fertigungsansatz. Während HDI auf ausgereiften subtraktiven Ätzprozessen und gut verstandenen Microvia-Strukturen basiert, erfordert Ultra HDI semiadditive Kupferprozesse, eine strengere Materialkontrolle und eine deutlich geringere Toleranz gegenüber Abweichungen, um reproduzierbare Produktionserträge zu erzielen.

Aus Sicht der Fertigung ist Ultra HDI jedoch keineswegs einfach nur die nächste Generation von HDI-Prozessen. Es ist ein neues und eigenständiges Betriebsparadigma mit völlig neuen Prozessgrenzen sowie neuen Anforderungen an Materialien und Risikobetrachtungen. Zwar lassen sich Ultra-HDI-Lagen und HDI-Lagen im selben Stack-up kombinieren, doch der erfolgreiche Einsatz von Ultra HDI erfordert fundiertes Wissen über die Prozesse und Prozessparameter.

Werfen wir einen praxisnahen Blick darauf, was HDI und Ultra HDI tatsächlich voneinander unterscheidet, sobald Ihr Design in die Produktion geht.

Zentrale Erkenntnisse

- Ultra HDI führt ein neues Fertigungsparadigma ein, bei dem traditionelle HDI-Methoden (subtraktives Ätzen, standardmäßige Lötstoppmaske, einfache Microvia-Stacks) bei ultrafeinen Geometrien instabil und unzureichend werden.

- Zuverlässige Produktion definiert den Erfolg, da UHDI semiadditive Kupferprozesse, engere Toleranzkontrolle und eine deutlich stärkere Abhängigkeit von Wiederholbarkeit über ganze Panels und Lose hinweg erfordert.

- Materialien und Registrierung werden zu den primären Yield-Begrenzern, wobei Glasgewebe, Ausdehnung in Z-Richtung, Kupferrauheit und kumulativer Maßdrift die Ausrichtung, Impedanz, Microvia-Zuverlässigkeit und die gesamte Fertigbarkeit direkt beeinflussen.

- Assemblierungs-Schnittstellen unterliegen strengeren Einschränkungen und erfordern häufig Trockenfilm-Lötstoppmasken, sorgfältig ausgewählte Oberflächenfinishs und eine frühe Zusammenarbeit mit Fertigern, um Risiken im Zusammenhang mit Microvia-Stacking, Pad-Definition und Fine-Pitch-Lötprozessen zu minimieren.

Wie Fertigungsbetriebe HDI und Ultra HDI in der Produktion unterscheiden

Aus fertigungstechnischer Sicht ist HDI weiterhin eng mit der konventionellen Multilayer-Verarbeitung verbunden. Die Strukturen sind kleiner und die Toleranzen enger, doch viele der grundlegenden Methoden bleiben vertraut. Subtraktives Ätzen, lasergebohrte Microvias und standardmäßige LPI-Lötstoppmasken können bei sorgfältiger Anwendung weiterhin gute Ergebnisse liefern.

Bei Ultra HDI schrumpfen die Strukturgrößen so weit, dass traditionelle Prozesse instabil werden, Registrierungsreserven verschwinden und Materialien, die bei HDI-Abmessungen gut funktionieren, plötzlich zum Nachteil werden. In diesem Maßstab hängt der Erfolg weniger davon ab, ob eine Regel einmal eingehalten werden kann, sondern vielmehr davon, ob sie sich über ein gesamtes Panel hinweg und von Los zu Los reproduzieren lässt. Die Fertigungsprozesse müssen sich grundlegend verändern, damit Fertiger eine zuverlässige Produktqualität sicherstellen können.

Strukturgrößen und die Realität der Musterbildung

Die meisten HDI-Designs arbeiten innerhalb von Leiterbahn- und Abstandsmaßen, die in konventionellen PCB-Fertigungsprozessen gut etabliert sind, und nutzen ausgereifte Prozesse, vorhersehbare Ausbeuten und bewährte Inspektionsmethoden. Ultra-HDI-Technologie verschiebt diese Strukturgrößen jedoch in einen deutlich anspruchsvolleren Bereich, in dem traditionelles subtraktives Ätzen aufgrund der höheren Empfindlichkeit gegenüber Faktoren wie Kupferdickenschwankungen, Ätzfaktor und Imaging-Genauigkeit Schwierigkeiten hat, konsistente Ergebnisse zu liefern.

- HDI: Nutzt ausgereifte, stabile Prozesse mit vorhersehbaren Ausbeuten.

- Ultra HDI: Erfordert Prozesse wie semiadditive oder modifiziert semiadditive Verfahren zum Aufbau von Kupferstrukturen, da subtraktives Ätzen bei extrem kleinen Strukturgrößen an seine Grenzen stößt.

- Mindest-Designregeln sind nicht gleichbedeutend mit stabiler Produktionsfähigkeit; DFM-Prüfungen garantieren bei Ultra HDI keine reproduzierbare Ausbeute.

Für PCB-Designer lautet die entscheidende Botschaft: Mindest-Designregeln garantieren selbst dann keine reproduzierbare und stabile Produktionsausbeute bei Ultra HDI, wenn sie eine DFM-Prüfung bestehen. Fertiger betonen, dass zuverlässige Produktionsfähigkeit etwas anderes ist als das absolute Minimum, das eine Regel erlaubt. Entwickler sollten daher priorisieren zu verstehen, wie ein Merkmal gefertigt wird – nicht nur, wie klein es theoretisch sein kann.

Via-Strukturen: Vertraute Formen, neue Konsequenzen

HDI-Designer sollten bereits mit Microvias vertraut sein, häufig versetzt und manchmal ein oder zwei Lagen tief gestapelt. Die Zuverlässigkeit auf diesem Niveau ist gut charakterisiert, insbesondere wenn Materialien und Galvanikprozesse gut aufeinander abgestimmt sind.

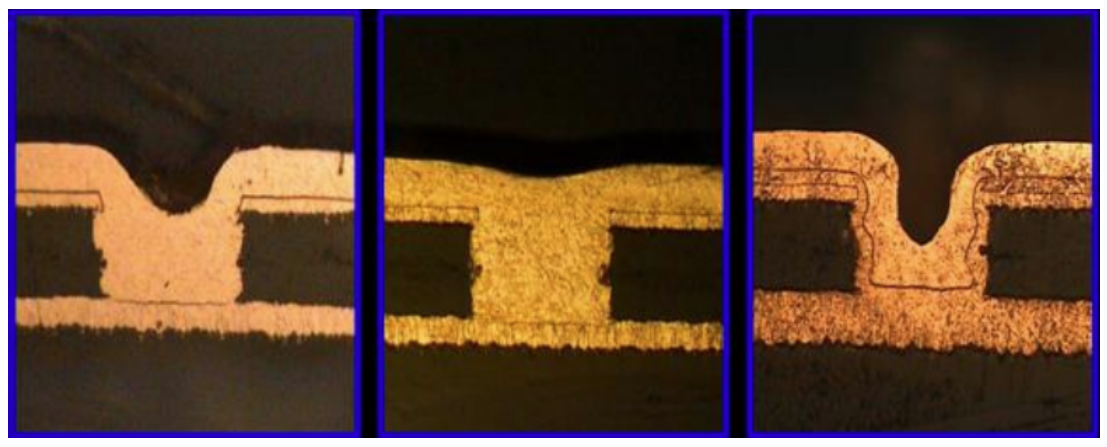

Ultra HDI ist deutlich stärker auf gestapelte Microvias angewiesen, die häufig kupfergefüllt sind und sich über mehr als 2 Build-up-Lagen erstrecken. Die Aspektverhältnisse werden kritischer, die Gleichmäßigkeit der Metallisierung wird entscheidend, und selbst kleine Hohlräume können die Zuverlässigkeit beeinträchtigen. In diesen Größenordnungen sind Via-Geometrie, Füllchemie und thermisches Verhalten untrennbar miteinander verbunden.

Aus Sicht der Fertigung erhöhen tiefere Stacks die Bohrempfindlichkeit, die Komplexität der Metallisierung und die Schwierigkeit der Inspektion. Aus Sicht des Designs erhöht jede zusätzliche gestapelte Lage das Risiko eines Microvia-Ausfalls während der Assemblierung oder im Feldeinsatz. Die Frage verschiebt sich von „Kann das gebaut werden?“ zu „Übersteht das Reflow und Feldbedingungen dauerhaft und konsistent?“

Materialien: Einschränkungen und Auswahl bei Ultra HDI

In Ultra-HDI-Designs legt die Materialauswahl die Grenzen der Leistungsfähigkeit in der Fine-Line-PCB-Fertigung fest, einschließlich Strukturgröße, Registrierungstoleranz und Interconnect-Zuverlässigkeit. Laminate und Kupferfolien, die bei konventionellem HDI akzeptabel sind, werden oft zum Yield-begrenzenden Faktor, wenn Leiterbahnbreiten, Capture-Pads und Microvia-Durchmesser in den Bereich von einigen zehn Mikrometern schrumpfen. In diesem Maßstab dominieren Maßstabilität und Oberflächeneigenschaften gegenüber den nominellen elektrischen Leistungsdaten.

Mehrere materialbezogene Effekte müssen bei der Definition von Stack-up und Layout ausdrücklich berücksichtigt werden:

- Die Ungleichmäßigkeit des Glasgewebes führt zu lokalen Maßverzerrungen und Dielektrizitätsabweichungen, die sich bei ultrafeinen Geometrien direkt auf die Impedanzkontrolle und die Ausrichtung von Strukturen auswirken.

- Die Ausdehnung in Z-Richtung summiert sich über aufeinanderfolgende Laminierungszyklen und erhöht die mechanische Belastung in gestapelten oder eng beieinanderliegenden Microvias.

- Die Kupferoberflächenrauheit verändert bei sehr geringen Kupfergewichten die effektive Leiterbreite und die Definition der Leiterkanten, wodurch die Variabilität von Impedanz und Ätzgenauigkeit zunimmt.

Für Ultra HDI geeignete Materialsysteme mindern diese Effekte durch eine strengere Kontrolle des Glasgewebes, höhere Tg-Werte zur Reduzierung thermisch bedingter Bewegung sowie sehr glatte oder reverse-treated Kupferfolien. Diese Materialien definieren die erreichbaren Geometrie- und Registrierungsgrenzen und müssen daher ausgewählt werden, bevor Leiterbahnbreiten, Via-Strukturen und Laminierungsstrategie final festgelegt werden.

Registrierung: Umgang mit kumulativen Maßfehlern

Die Registrierung wird in Ultra-HDI-Layouts zu einem primären Designrisiko, da die Überlappungsreserve zwischen Vias, Pads und Leiterbahnen begrenzt ist. Jeder Laminierungs- und Imaging-Schritt führt zu Maßbewegungen, und der daraus resultierende Fehler ist kumulativ statt zufällig. Im Gegensatz zu standardmäßigem HDI gibt es oft nicht genügend Reserve, um diese Verschiebungen durch größere Pads oder größere Abstände aufzufangen.

Die Positionsgenauigkeit des Laserbohrens beseitigt das Registrierungsrisiko nicht, da sich die Bohrposition nach dem Maßzustand des Materials zum Zeitpunkt der Bearbeitung richtet. Dehnung der Fotowerkzeuge, Relaxation des Kerns und Harzfluss tragen alle zur Fehlausrichtung zwischen den Lagen bei. Wenn Capture-Pads und Leiterbahnstrukturen im Mikrometerbereich definiert sind, können selbst eng kontrollierte Fertigungsprozesse die zulässigen Toleranzen überschreiten.

Designer beeinflussen die Robustheit der Registrierung direkt über die Layoutstruktur. Eine geringere Anzahl von Laminierungszyklen, begrenztes Via-Stacking und eine konsistente Ausrichtung kritischer Strukturen über die Lagen hinweg reduzieren die Empfindlichkeit gegenüber Maßdrift. Realistische Abstände zwischen benachbarten Strukturen schaffen Toleranz für unvermeidliche Materialbewegungen, ohne die Ausbeute zu gefährden.

Grenzen von Lötstoppmaske und Oberflächenfinish

Ultra-HDI-Padgeometrien überschreiten häufig die Auflösungsgrenzen traditioneller flüssiger fotoabbildbarer Lötstoppmasken. Wenn Padöffnungen kleiner werden und Maskenstege schmaler ausfallen, werden Dickenkontrolle und Kantendefinition entscheidend für die Assemblierungsausbeute. Variabilität, die in größeren Maßstäben akzeptabel ist, wird bei Fine Pitch zu einem dominanten Fehlermechanismus.

In vielen Ultra-HDI-Anwendungen ist eine Trockenfilm-Lötstoppmaske erforderlich, um eine konsistente Aperturgeometrie und Registrierung aufrechtzuerhalten. Das Mischen von solder-mask-defined und non-solder-mask-defined Pads bei Fine Pitch erhöht die Variabilität von Lotvolumen und Benetzungsverhalten und sollte vermieden werden, sofern dies nicht ausdrücklich mit Fertiger und Bestücker validiert wurde.

Die Auswahl des Oberflächenfinishs ist ähnlich eingeschränkt. Gleichmäßigkeit der Schichtdicke und Konsistenz der Abscheidung wirken sich direkt auf Lötbarkeit und Koplanarität aus, wenn Pads und Leiterbahnen extrem klein sind. Diese Effekte zeigen sich oft erst während Assemblierung und Inspektion, obwohl sie auf Entscheidungen auf Layout-Ebene zurückgehen.

In Ultra-HDI-Designs sind die Auswahl der Lötstoppmaske, das Oberflächenfinish, die Fertigungsprozesse und die Anforderungen der Assemblierung eng miteinander gekoppelt. Entscheidungen, die während des Layouts getroffen werden, wirken sich nachgelagert aus, wobei nur begrenzte Korrekturmöglichkeiten bestehen. Daher ist eine frühe Abstimmung über den gesamten Fertigungsablauf hinweg entscheidend.

Was Designer anders machen sollten

Erfolgreiches Ultra-HDI-Design erfordert ein Umdenken. Binden Sie Fertigungspartner früher ein, als Sie es bei HDI tun würden. Fragen Sie, wie Strukturen hergestellt werden – nicht nur, ob sie die Regeln erfüllen. Planen Sie überall dort Reserve ein, wo das System es zulässt, selbst wenn der Dichtedruck hoch ist. Ultra HDI ist eine eigene Disziplin mit eigenen Best Practices und eigenen Ausfallmechanismen.

Ganz gleich, ob Sie zuverlässige Leistungselektronik oder fortschrittliche digitale Systeme entwickeln müssen – Altium Develop vereint jede Disziplin zu einer kollaborativen Kraft. Frei von Silos. Frei von Grenzen. Hier arbeiten Ingenieure, Designer und Innovatoren als Einheit zusammen, um ohne Einschränkungen gemeinsam Neues zu schaffen. Erleben Sie Altium Develop noch heute!

Häufig gestellte Fragen

Was ist der Hauptunterschied zwischen HDI und Ultra HDI?

Ultra HDI geht weit über eine bloße Verkleinerung von HDI-Strukturen hinaus – es erfordert vollständig andere Fertigungsprozesse, Materialien und Toleranzen. Traditionelles subtraktives Ätzen, standardmäßige LPI-Lötstoppmasken und einfaches Microvia-Stacking werden bei ultrafeinen Geometrien instabil. Stattdessen ist Ultra HDI auf semiadditive Kupferprozesse, extrem enge Registrierungskontrolle und hochspezialisierte Materialien angewiesen, um zuverlässige Ausbeuten sicherzustellen.

Warum kann ein Design DFM-Prüfungen bestehen und dennoch in der Ultra-HDI-Produktion scheitern?

DFM-Prüfungen verifizieren, dass ein Design die minimal zulässigen Regeln erfüllt, doch Ultra HDI erfordert Wiederholbarkeit und nicht nur einmalige Machbarkeit. Faktoren wie Materialbewegung, Imaging-Genauigkeit, Kupferdickenschwankungen, Gleichmäßigkeit der Microvia-Füllung und kumulative Registrierungsdrift können dazu führen, dass Strukturen außerhalb der stabilen Produktionsfähigkeit liegen. Das Bestehen einer DFM-Prüfung garantiert nicht, dass das Design über Panels und Lose hinweg konsistent gefertigt werden kann.

Wie viele gestapelte Microvia-Lagen sind bei Ultra HDI realistisch, und was beeinflusst ihre Zuverlässigkeit?

Ultra-HDI-Designs erfordern häufig gestapelte, kupfergefüllte Microvias über mehrere Build-up-Lagen hinweg, doch mit zunehmender Stapelhöhe nimmt die Zuverlässigkeit stark ab. Aspektverhältnis, Galvanikchemie, thermische Zyklen, Ausdehnung in Z-Richtung und Grenzen der Inspektion beeinflussen die Überlebensfähigkeit. Die entscheidende Frage verschiebt sich von „Kann es gefertigt werden?“ zu „Übersteht es den Reflow-Prozess und die Einsatzbedingungen im Feld?“ In der Praxis verbessert eine geringere Stapeltiefe die Ausbeute, Zuverlässigkeit und Fertigungsstabilität bei der Ultra-HDI-PCB-Fertigung, bei der die Komplexität gestapelter Microvias die Prozesswiederholbarkeit direkt beeinflusst.

Welche Materialien sollte ich für eine stabile Ultra-HDI-Performance wählen?

Die Materialauswahl ist einer der wichtigsten Erfolgsfaktoren für UHDI. Dazu gehören Laminate mit hochkontrollierter Glasgewebestruktur, geringer Ausdehnung in Z-Richtung sowie sehr glatte oder rückseitenbehandelte Kupferfolien, um Leiterbahnpräzision und Registerhaltigkeit sicherzustellen. Diese Materialien helfen, Impedanzschwankungen, Leiterkantenrauheit und Maßdrift zu verringern, die die Ausbeute bei ultrafeinen Geometrien beeinträchtigen können.