PCBにおけるシグナルインテグリティー解析の基本

PCBにおけるシグナルインテグリティー解析の基本は、実に複雑となりえます。シグナルインテグリティー・シミュレーションツールは、回路図やレイアウト設計中にさまざまなネット内の信号の動作を計算するのに最適ですが、結果を解釈するにはいくつかの手順を実行する必要があります。一部のシグナルインテグリティーおよびEMシミュレーションツールは高度な機能を備えている場合がありますが、測定から収集できる情報と比較することはできません。PCBにおける信号整合性を検査するためにどの方法を使用する場合でも(両方行うことをお勧めします)、信号の動作を解析してPCBの問題を特定するために実行できる重要な手順がいくつかあります。

シグナルインテグリティー解析を始める

シグナルインテグリティー解析は、レイアウト前の段階でのシミュレーションから始まります。レイアウトを構築したら、いくつかの重要なレイアウト後のシミュレーションを使用して、PCB内のジオメトリに依存するシグナルインテグリティーを解析できます。ある時点で、シグナルインテグリティーのシミュレーション結果を実際の測定結果と比較する必要があるため、結果を比較できるように保管しておいてください。

レイアウト前の解析

ここで重要なのは、回路設計、コンポーネントの選択、および2つのコンポーネントのI/O間での信号の伝達方法を調べることです。PCBの動作について多くの情報を与えてくれる重要な解析が3つあります。

-

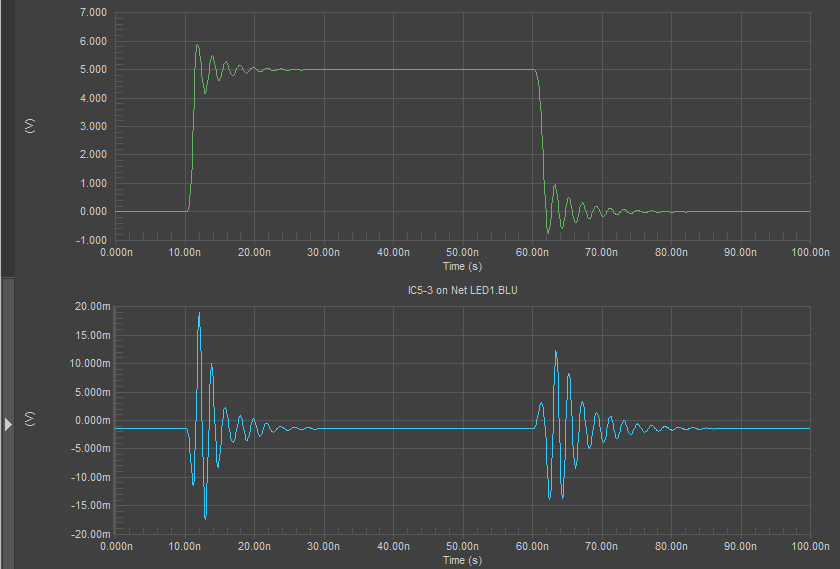

過渡動作。2つのバッファ間の接続における過渡応答については、過渡解析を用いて時間領域でモデル化することも、ポールゼロ解析から過渡応答の動作を見ることもできます。これにより、リンギングによるオーバーシュート/アンダーシュートと、意図した信号レベルへのアプローチが表示されます。集積回路を使用したこれらのシミュレーションの最も正確なバージョンにはIBISモデルが含まれますが、SPICEサブ回路を使用してI/Oバッファをモデル化することもできます。

-

Sパラメーターと伝達関数。PCB内の特定の機能ブロックはマルチポートネットワークとしてモデル化できます。つまり、それらの線形動作は特定の周波数におけるSパラメーターで説明できます。Sパラメーターは、時間領域の反射係数から決定できます。伝送線路では、負荷容量によって与えられる入力インピーダンスが関係します。Sパラメーターからネットワークの伝達関数を計算したり、伝達関数からSパラメーターを計算したりすることができます。これは、関連するすべての数学について説明する有用なガイドです。

-

インパルス応答。 このシミュレーションには2つの目標が含まれます。定義された帯域幅での因果関係についてSパラメーターモデル/伝達関数を認定することと、定義された立ち上がり時間でのパルス応答動作を調べることです。インパルス応答を使用すると、相互接続設計に沿って分散と伝播遅延を抽出することもできます。これにより、PCBをレイアウトする前に、理想的な状況で特定の入出力バッファペアに対する対象のチャンネルモデルが認定されます。

-

アイダイアグラム。バッファモデルと相互接続設計を使用して、アイダイアグラムをシミュレートできます。アイダイアグラムは、疑似ランダムビットシーケンスの下で予想される信号レベル、オーバーシュート、シンボル間干渉(ISI)、ジッター、および予想されるビットエラーレートを示すため、チャンネル・コンプライアンスに欠かせません。

より複雑なチャンネルでは、上記の一連のレイアウト前の解析が、トランジションにより計画されたものなどを評価するのに役立ちます。

設計前に、これらの各要素の構造を知っていれば、次のことができます。

レイアウト後の解析

ここで重要なのは、PCB内の寄生成分が信号の完全性にどのような影響を与えるかを調べることです。寄生的なシグナルインテグリティー効果はPCBのジオメトリの関数であるため、ジオメトリに依存する次のシグナルインテグリティーの問題を調べる必要があります。

-

クロストーク。多くの設計者の悩みの種であるクロストークは、誘導性カップリングと容量性カップリングから発生します。被害者と加害者のトレース上のクロストークの影響を調べる場合、容量性カップリングは、2つが隣接している場合にのみ発生します。誘導性クロストークは範囲に制限されず、PCB内のすべてのトレースが磁界を介して互いに結合することができます。

-

伝送線路の動作。レイアウト前の段階で伝送線路モデルを使用して信号トレースを調べることもできますが、レイアウトから直接行うほうがよいでしょう。伝送線路がインピーダンス制御されていない場合は、伝送線路の反射(もしあれば)が受信機の信号レベルを低下させ、デジタル信号で階段状の応答につながるかどうかを調べる必要があります。アナログ信号の場合、伝送線路上の干渉や定在波の形成を探すことになるため、より困難となる可能性があります。しかし、適切なシグナルインテグリティー・シミュレーターを使うと、入射波と反射波を分けることができるので、 それぞれの挙動を個別に調べることができます。その後、反射レベルから、信号レベルが信号要件を満たしているかどうかを確認できます。

-

レイアウト前に調べたものすべて。ここで重要なのは、寄生成分やファイバーの織りなどがPCB内の信号の動作を劇的に変えていないことを確認することです。複数のトレースが失敗する場合は、レイアウトを変更する必要があります。まず始めに、 スタックアップ とトレースジオメトリを作成します。

シグナルインテグリティー解析ツール

上記の点は、これらのシグナルインテグリティー解析ツールを構築して実行するのに複雑なシミュレータープログラムが必要であるかのように思われるかもしれません。必要となるツールは、何をシミュレートして評価したいかによって異なります。EDAツール内では、これらのシミュレーションの一部はIBISなどを使用して単純に実行されますが、複数のネットを使用したより複雑なシミュレーションには 3Dフィールドソルバーまたは同等の2D ソルバーツールが必要になる場合があります。

インピーダンス仕様のないシングルエンドバス

終端のない低速のシングルエンドバスでは、インターコネクトの構造(キャパシタンスとインダクタンス)に起因することもある過渡挙動(リンギング)を確認できる場合があります。これは、トレースが短絡した場合にSPIで確認されるかもしれません。これらのバスでは、回路図に伝送線路モデルを適用し、ピンの仕様(SPICEサブサーキットまたはIBISモデル)を定義していれば、レイアウト前のリンギングが確認される場合があります。

シングルエンドバスが実際に配線されると、EDAツールのシグナルインテグリティー・アナライザーを使用してレイアウト後のシミュレーションを実行できます。こうしたアナライザーは、論理回路ファミリーの割り当てまたは関連するピン/ネットのIBISモデルを使用して、以下をシミュレートできます。

- クロストーク波形、および強い結合領域を特定するため

- 反射波形

- その他の信号挙動指標(上昇/下降時間、オーバーシュート/アンダーシュートなど)

- トラックの長さに沿った平均インピーダンスを計算する

インピーダンス仕様のないシングルエンドバスでは、バスが長くなるとドライバー側での反射や、バス上のキャパシタンスとインダクタンスによるリンギングが確認される可能性があります。リンギングによって過剰なオーバーシュートが発生する場合、リンギングの振幅を低減するには、トレースのインダクタンスを減らすこととダンピングを追加することが最も一般的な2つ方法です。または、直列抵抗を追加してダンピングを高めることもできます。これは、低インピーダンスのバッファ出力をより長い不整合伝送線路に接続する場合に行います。

インピーダンス制御バス

シングルエンドおよび差動インピーダンス制御バスでは、終端インピーダンスがオンダイになる可能性があるため、ポストレイアウトでの論理回路ファミリーベースのシミュレーションでは、バスのインピーダンスが正しく記述されないため効果的ではありません。2つの相互接続間の結合を立ち上がり時間の関数としてのみ見ているため、クロストークをシミュレートでき、論理回路ファミリーのみを割り当てた場合でも、クロストークの大きさは立ち上がり時間に応じて逆比例します。

反射やインピーダンス違反に対するレイアウト後のシミュレーションの場合、論理回路ファミリーの記述に依存するのではなく、少なくとも IBISモデルを使用してバッファの動作を定義する必要があります。バッファの記述が既知で利用可能である限り、PCBエディターでコンポーネントの動作をモデル化するために適用できます。クロストークと反射波形のためのPCBエディターの標準的なシグナルインテグリティーツールは、より高度な解析ツールに移行する前に、多くの信号動作(立ち上がり/立ち下がり時間、オーバーシュート、クロストーク、一貫したインピーダンス、およびリンギング)の事前適格性チェックに役立ちます。

アイダイアグラム、マルチネットクロストーク、ネットの長さに沿ったインピーダンス偏差などをシミュレートするために使用できる外部ツールがあります。フィールドソルバーはそうしたオプションの1つで、さまざまな専門レベルで使用できるこれらのツールが多数あります。全波フィールドソルバーなどは、放射エミッションをシミュレートしたり、SI/PI を使用してさらに深いものをシミュレートしたり、シミュレートされたネットでSパラメータを抽出したりする場合を除き、必ずしも必要というわけではありません。

Altium Designer®の優れたPCB設計・解析ツールは、レイアウト前後のシグナルインテグリティー・シミュレーションツールとして使えるため、シグナルインテグリティー解析を始める方に最適です。これらの正確な計算により、測定値を比較するためのベースラインが得られます。また、単一のプラットフォームから充実した製造計画機能や文書化機能にアクセスできます。

今ならAltium Designerの無料トライアルをダウンロードして、業界最高のレイアウト、シグナルインテグリティー・シミュレーション、生産計画ツールについて詳しく学べます。Altium Designerの詳細については、Altiumのエキスパートまで今すぐご連絡ください。