Routing Requirements for a USB Interface on a 2-Layer PCB

In an earlier blog, I discussed some of the basic points in preparing routing rules for 2-layer PCBs to support routing and layout with digital signals. In particular, we looked at some of the basic stackup and routing rules needed to support a digital interface like I2C or SPI on a 2-layer PCB. When working with these interfaces, a few simple guidelines can help ensure signal integrity in your board and cut down on EMI.

What about an impedance-controlled interface like USB? The need for impedance control, and knowing when it can be violated, is the main point for routing something like USB on a 2-layer PCB. In this article, I’ll show how you should route a high speed protocol like USB. Specifically, we’ll look at the important design rules needed for routing the board, particularly the length limitation we could accept for traces carrying USB data. If you haven’t read the previous article in this series yet, take a look as it lays some of the conceptual groundwork needed to understand the limits that get set on USB routing requirements.

Getting Started: USB High Speed Routing Requirements

In the previous article on 2-layer PCB routing, we looked at a procedure to determine the longest possible line length you could use in your design without needing to apply impedance matching. We found that the length limit depends on the level of input impedance deviation you can tolerate along the length of the transmission line. In particular, depending on whether you consider 10% to 25% of the signal travel distance to be the important factor for limiting trace length.

For this demo, I want to look at USB 2.0 routing on this board under the High Speed standard, and I’m focusing on this standard for a specific reason. USB 2.0 (High Speed) is still used in some systems as it provides connectivity with older devices alongside fast data transfer rate, and it’s still used on popular platforms like Arduino with a Type B plug.

Just to illustrate two possible designs, I’ve compared the data rate and rise time of two USB 2.0 specs (Full Speed and High Speed):

|

|

|

|

|

|

|

|

|

The process I’ll show below is carried out for USB 2.0 signals with the High Speed rise time and skew, but you could apply the same process to USB 3.0 or any other high speed interface. Just remember: routing on a 2-layer board is not appropriate for every interface. For example, I don’t know anyone that would recommend routing DDR4 on a 2-layer board due to the small length limits and the radiated noise from these fast signals.

Critical Length

First, we would like to know the critical length for a USB signal being routed on a typical 2-layer PCB. For a Dk = 4.8 core of FR4 material, we would have a propagation delay of approximately 150 ps/inch, or approximately 6 inches/ns. With our 500 ps rise time for the High Speed spec, this gives a signal propagation distance of 3 inches during the rise time. If we’re very conservative and use a 10% limit on the critical length, this gives a critical length of 0.3 inches!

The topology we need to route here is just a serial line with differential pairs. So you have three elements:

- The driver component, or your processor with the USB interface

- The termination resistors (see the section on this below)

- The connector that will hold your USB cable

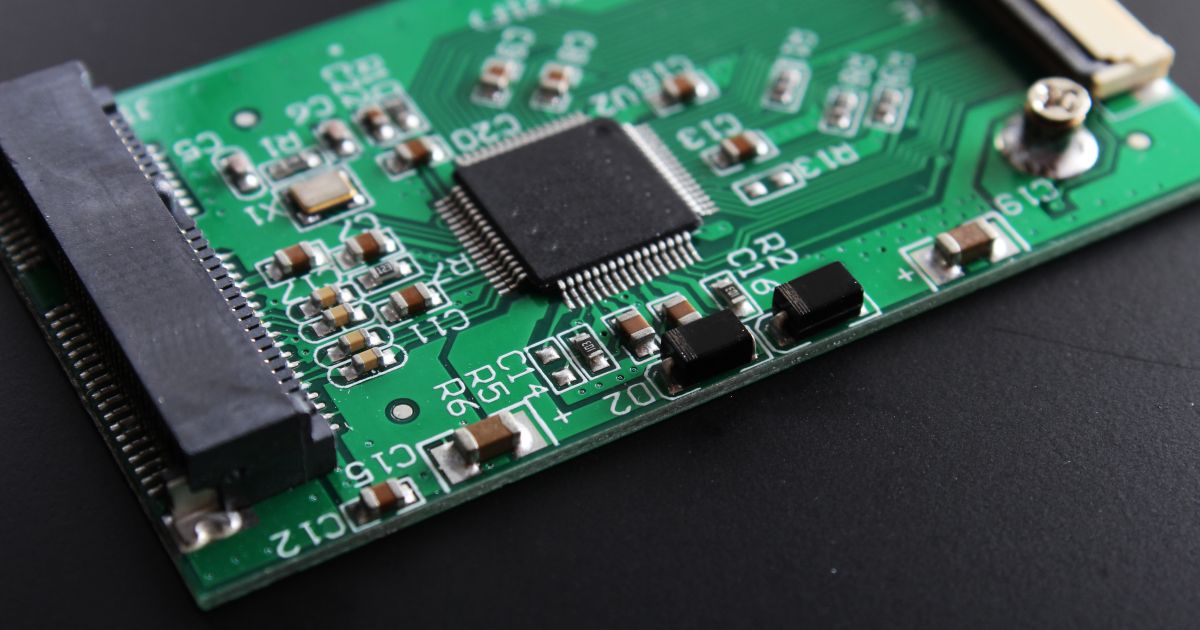

You might be wondering, how is it done on a platform like Arduino? Take a look at the image below of an Arduino Mega you can buy on Amazon. The USB controller is placed close to the connector and is definitely within 1 inch.

You’ll find similar placement and routing on other Arduino boards. In order to avoid an input impedance mismatch with the connector, cable, and receiver, we would want to follow the advice shown above and keep the route short on our 2-layer PCB. However, we don’t need to be so conservative as to apply a 10% limit. Instead, if we go with a 25% limit, we’ll have a much more comfortable routing distance of 0.75 inches, which is much more manageable on a 2-layer PCB.

Note that this is for the High Speed spec. Under the Full Speed spec, we have a more relaxed 2.4 inch critical length (10% limit) or 6 inch critical length (25% limit) for a 4 ns rise time.

One thing that is important to note is this: the critical length rule is almost never correctly used. I can tell you multiple reasons why this is the case:

- There is no set limit (10%, 25%, or otherwise) where we have a valid critical length, and depending on the size of your PCB, you might be above the critical length and now need to design directly to the target impedance.

- The actual critical length limit depends on bandwidth your channel requirement (NOT on a signal bandwidth like the knee frequency) and on the input impedance difference you can tolerate in your design.

- Calculating the correct critical length for your PCB requires knowing the trace impedance already, and then using this to calculate an input impedance.

- Any apparent relation to a signal rise time is purely for convenience and is only valid when transmission lines are already "short"

Because determining the right percentage for your critical length requires calculating mutliple impedance values, you're better off avoiding any rule based on a critical length. It is always easier to just design to the required USB impedance.

Termination Resistors

Next, we need to consider how the driver output is terminated. Since we’re talking specifically about USB here, note that the USB 2.0 spec requires some termination resistors on the D+ and D- lines near the connector to match impedances. These might be integrated into the USB transceiver on the die, or they could be required as an external component. Typical values are 15 Ohms, 22 Ohms, or 45 Ohms, although other values might be used; make sure to check your datasheet for your component to see what termination is needed. Just as an example, the TUSB2077APTR USB Hub controller uses 27 Ohm termination resistors. Make sure to check the datasheet to check whether you need these external resistors.

Differential Skew

With a 100 ps skew limit in the High Speed standard, we can now calculate the allowed length mismatch between the two sides of the differential pair (the D+ and D- signals). Taking the approximate 6 ns/inch propagation delay estimate for surface-layer routing, and multiplying by the skew limit, we get a 0.6 inch (600 mil) trace length difference. This is very large! We have a lot of freedom to allow for some trace length matching. However, there is an important point here: this includes the entire length of the interconnect (your board + cable + receiving board). Therefore, just to be safe, do your best to limit skew as much as possible by routing the pairs together and enforcing a bit of length matching where possible. This is quite easy because USB controller chips will generally place the D+ and D- signals on the same edge of the chip.

When the length difference is short, you may not need to implement length tuning as it takes up space in the PCB layout. Just to see what other functional systems will do, take a look at the image of the Arduino UNO PCB layout shown below (note: this was converted from Eagle files). The USB lines have been highlighted in the image. If we measure the lengths of the positive and negative sides of these lines (spanning each side of the termination resistors), we find that the length difference is about 180 mils. This is why these lines are not being length matched between the Arduino and the USB connector.

In this tight space, the interface will still work correctly because the difference in lengths is only about 180 mils, which is much smaller than the skew allowance. Even with worst-case fiber weave effect on a loose glass weave laminate, the total skew (in terms of length) would only amount to an equivalent of less than approximately 230 mils, still much lower than the skew allowance for this interface.

Your Routing Style: Coupled Differential Pairs or Coplanar Differential Microstrips

As I pointed out in the previous blog, you can’t use the trace width corresponding to the characteristic impedance in High Speed USB 2.0 and still meet the impedance spec. Remember, the trace width on a standard thickness PCB with two layers was about 110 mils for Dk - 4.8. How can we possibly hit the differential pair impedance spec in USB 2.0 high speed with that trace width?

In reality, we don’t need to use that trace width due to the way the traces in differential pairs will couple to each other. If you use your layer stackup calculator with a thick 2 layer board to calculate the differential impedance for microstrips, you’ll find that the actual trace width needed is much smaller and is a function of spacing. For our example microstrip lines on a 2-layer PCB, the Layer Stack Manager in Altium Designer, included in Altium Develop, tells us that the trace width is about 16 mils for 5 mils spacing.

You could use thinner traces with these differential microstrips, but you would need to use a smaller spacing. In this design, we’re close to the limit of trace-to-trace clearances for etching, so keeping the 5 mil clearance between the traces is okay as we are hitting the single-ended spec and the differential spec with these trace widths. How do we know we are hitting the single-ended portion of the spec? This is because: the trace width given above is for the odd-mode impedance of a single trace, not the characteristic impedance! This is why you need to stick with this particular value for the trace width and not use the characteristic impedance value for a single microstrip in isolation.

There is an alternative that we didn’t discuss: using coplanar microstrip differential pairs. By running ground pour up to the microstrips on the surface layer, and by placing ground pour below the signals on the bottom layer, you can achieve 90 Ohms differential impedance with 9.5 mil wide traces, 5 mil trace gap, and 5 mil spacing to ground. We can see from the values below that we nicely get to the required 90 Ohm impedance in the USB 2.0 spec with these values.

With this arrangement, we won’t have to worry so much about the critical length problem and trace width problem in a 2-layer board. However, you need to note that this width and spacing must be maintained throughout the length of the route. USB routing treats the traces as individual single-ended traces that just happen to be carrying a differential signal, so you could route them separately.

Inside the PCB Layout

The routing topology is pretty simple: route from the USB chip to the termination/pull-up/pull-down resistors, and then to the connector, all as differential pairs. The image below shows the high-level routing topology with pull-up and pull-down resistors. Some capacitors are also required under the USB 2.0 standard as shown below.

Routing is rather simple: obey the standard differential pair routing practices going between each portion of the system and you won’t have problems with signal registration or impedance matching. Keep short routes with direct connections coming off the differential pair lines to make connections to GND/VCC for the pull-down and pull-up resistors. Make sure to check the application circuit for your device in your datasheets as the D+/D- lines may have additional external capacitors on the device; you’ll see this on the TUSB2077A device I cited above.

We’ll show a real example in the PCB layout in an upcoming blog. For now, try this out yourself and see if you can get the design routed.

Summary

In this blog and our previous blog post, we looked at some of the important routing rules to follow when setting up and routing a high speed interface like USB on a 2-layer PCB. Here are our final routing guidelines:

- If you don't have access to a differential impedance calculator, or you don't know how to calculate it, then just keep trace lengths less than 0.75 inches without impedance control

- Keep the differential pair length mismatch within 0.6 inches - this is very easy to do

- If you can access a differential impedance calculator, then use differential microstrips or coplanar differential microstrips (both with controlled impedance) and design to the 90 Ohm differential impedance spec

The routing guidelines shown here won’t always guarantee EMC, there are other aspects of the design to consider, which are sometimes poorly done in 2-layer PCBs. However, these guidelines will certainly help with EMI if you’re working with the Full Speed spec. My personal preference is to use a 4-layer PCB for serial digital buses and high speed protocols, particularly if the board is larger or it’s going to go into production at volume.

If you’re using USB 3.0, then you’ve got stringent requirements on length matching due to fast edge rates, and you should place the interface close to the connector like we’ve done with the Full Speed spec listed above.

Modern PCB design programs like Altium Develop give you a complete set of routing tools for high speed impedance-controlled designs, making differential pairs without ground an easy feature to route in your PCB layout. Altium Develop delivers an unprecedented amount of integration to the electronics industry until now relegated to the world of software development, allowing designers to work from home and reach unprecedented levels of efficiency.

Whether you need to build reliable power electronics or advanced digital systems, Altium Develop unites every discipline into one collaborative force. Free from silos. Free from limits. It’s where engineers, designers, and innovators work as one to co-create without constraints. Experience Altium Develop today!