Crosstalk Analysis, Reduction, and Elimination Techniques in PCB Design

Whether you're designing a digital board with a ton of traces, or an RF board operating at very high frequencies, any electronic device with propagating signals will experience crosstalk. It's simply a matter of whether that crosstalk is so extreme that the system fails to function, or whether crosstalk is within some acceptable limit. There is no universal level of "acceptable" crosstalk levels, but if you do find through simulation and measurement that you have a problem, there are very simple methods that can be used to reduce crosstalk.

In this article, we want to look at some sure-fire ways you can reduce crosstalk in your high-speed designs. I'll outline three methods that are simple and that always produce favorable results. There is one other method that can provide improvements, but it requires some additional analysis or simulation to ensure you do not create a new signal integrity problem.

What Is Crosstalk in PCB Design?

Very simply defined, crosstalk is a phenomenon where an interconnect carrying a signal (the aggressor) will inductively or capacitively couple that signal into a neighboring interconnect (the victim). This is bidirectional: the victim and aggressor could be swapped, and all else being equal you would expect crosstalk to occur in both directions. Crosstalk only occurs while a signal is changing, meaning during the edge rate of a digital signal; for analog/RF signals, a phase shifted replica can occur on neighboring interconnects because the signal on the aggressor is always changing. Purely DC signals do not cause crosstalk, but they can be victims of crosstalk.

A simple graphic illustrating crosstalk and the equations that determine the strength of a crosstalk signal on a victim interconnect are shown below. Crosstalk as shown here is sub-divided into two types:

-

Near-end crosstalk (NEXT, red curve), sometimes called background crosstalk

-

Far-end crosstalk (FEXT, green curve), sometimes called forward crosstalk

Both types of crosstalk are mediated by the mutual inductance (Lm) and mutual capacitance (Cm) between the two traces. Together, these two effects determine the crosstalk seen at the driver side and receiver side of a victim line.

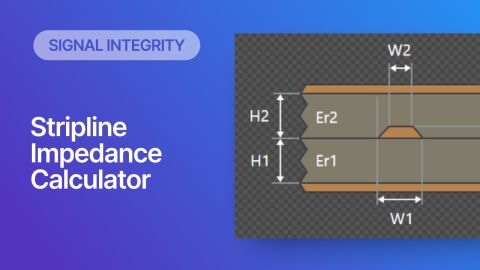

If you're into the mathematics governing crosstalk, you'll notice that FEXT could be eliminated in ideal cases, which is indicated by the negative sign in the FEXT equation. An ideal, perfectly symmetric stripline would have zero FEXT, although in reality the crosstalk is never zero.

Now that we've covered this basic introduction, let's look at the simplest crosstalk reduction techniques.

Crosstalk Reduction Techniques You Can Use in Altium

If you are designing a PCB that uses digital signals, and those signals have fast enough edge rate to create noticeable crosstalk, then you should always route these signals over a ground plane. This means, at minimum, you should use a SIG+PWR/GND/GND/SIG+PWR stackup for digital designs, particularly when the signal rise time reduces down to the ns range or lower.

Routing over a ground plane in this type of stackup provides a defined impedance that can be set to 50 Ohms as needed, so it can support standardized single-ended and differential interfaces with specified impedance requirements. This will set the trace width to a specific value, which can then be used to set a spacing value between traces.

Increased Spacing Between Traces for Crosstalk Reduction

The simplest and most effective way to reduce the strength of crosstalk received on a victim trace is to increase the spacing between traces. When traces are closer together, the electric and magnetic fields around the aggressor trace will be stronger, thus any crosstalk on the victim trace will be stronger. Therefore, increasing the spacing will certainly create crosstalk reduction between the lines.

There is a basic PCB design rule of thumb known as the "3W" rule, which states that:

-

Spacing between two traces should be at least 3x the width of the traces.

The intention behind this rule is to provide a very conservative value that generally provides for crosstalk reduction within noise margin limits that apply to most logic families. This rule is appropriate for high-speed traces above a ground plane, but with a thicker dielectric layer that was formerly used in traditional builds before the advent of HDI. I'll explain more about why this is important below.

To implement this in Altium, you can do the following:

-

Create a Net Class containing the high-speed nets that could be crosstalk aggressors.

-

Apply a width rule to the traces in your Net Class that sets the desired width. If these traces are impedance controlled, apply the impedance profile from the layer stack manager.

-

Set a trace-to-trace spacing rule in the Clearance section of the PCB Rules and Constraints Editor. Apply the larger spacing only to your Net Class.

This will ensure your spacing rules are set specifically for the high-speed traces you want to separate without enforcing the same rule on all other traces.

What about the spacing between differential pairs? This is one area where using tight coupling is beneficial as it ensures crosstalk into a differential pair is maximally received as common-mode noise. However, as I discuss below, there are more benefits to loose coupling compared to tight coupling, and there may be better strategies when differential pairs are involved.

Minimize Parallel Trace Lengths To Reduce Crosstalk

Crosstalk between two traces is weighted by the dot product of orthogonal vectors between the two coupled traces. In non-mathematician's terms, this means that crosstalk between two traces is maximized when the two traces are running parallel to each other. Therefore, one simple strategy to reduce crosstalk is to minimize the length over which two traces are parallel to each other.

If you carved out routing channels in single directions, then this is easier said than done. However, this is the basis for orthogonal routing without a ground plane, where traces on two different layers run perpendicular to each other. This works until you get to very fast edge rates; read more about orthogonal routing in this article.

If you want to enforce this practice in your routing tools, you can use the ParallelSegment rule in the PCB Rules and Constraints Editor, as shown below. Note that the ParallelSegment rule also applies a minimum clearance, just like you would do with the Clearance rule shown above.

Use a Smaller Distance to Ground for Crosstalk Reduction

The 3W rule mentioned above is an appropriate benchmark for traces routed on thicker dielectric layers. However, there is an alternative method that can be used for crosstalk reduction: bring ground closer to the traces. If you are routing on thinner layers, it is also possible to go smaller than the 3W rule, and could still see the same magnitude of crosstalk you would have seen on thicker layers when routing with the 3W rule.

As an example, take a look at the simulation results below. These curves show crosstalk results using 4-port S-parameters for striplines in a stackup built with Megtron 7 laminates. The top graph shows what happens in a typical fine-line situation on a 4 mil layer, where the spacing and linewidth between our striplines are equal. If we simply move the ground planes closer by decreasing the dielectric thickness by 50%, and then resize the traces to hit the same impedance target, we see that we get a significant reduction in nominal crosstalk without having to do any rerouting.

In this example, the resizing of the traces can be completed by regenerating the impedance profile in the layer stack management in Altium, followed by regenerating the design rules for these nets. The process takes a couple minutes and requires no re-routing. We could also swap with a different dielectric constant to get further improvements.

If your design is already complete and you're preparing for fabrication, swapping a dielectric layer is a simple materials change that can be implemented by your manufacturer. If you're still in the middle of your design, you can change the stackup in your PCB layout file, and then change the trace widths for an impedance controlled traces; no re-routing would be needed. Both options give considerable benefits for crosstalk.

Should You Use Copper Pour and Guard Traces for Crosstalk Reduction?

Finally, one method that designers might try to employ quite often is the use of copper pour between two traces, or routing of a guard trace between your two signal traces. I don't advise relying on this as a method to reduce crosstalk, and neither do many other experts. There are several reasons for this:

-

In order to fit a guard trace or copper pour between two coupled traces, you need to space them out, typically by at least 3W

-

Bringing ground closer to the traces can produce the same crosstalk reduction you might be attempting to achieve by routing a guard trace

-

There is no automated way to quickly route a guard trace, you have to route it and place its ground manually with vias

-

Copper pour is basically like a guard trace and it can be placed in an automated fashion, but stitching vias can actually increase crosstalk by creating an open resonant cavity between the two coupled traces; this is the same reason you get extreme power loss on certain coplanar waveguides as shown here.

-

Using copper pour with stitching vias requires some calculation or simulation prior to implementation to get it correct

Point #1 is most important: to even make room for appreciable copper pour or guard traces, you already need to provide enough space to hit at least a 3W spacing. This will provide significant protection against crosstalk as long as there is a ground plane present on the next layer.

Therefore, before using copper pour and guard traces method, consider the other points above first as they can provide significant improvements that bring your interconnects into compliance. To learn more about this, watch the following video.

In the video, I show a set of simulation results from Eric Bogatin and Bert Simonovich, which reveal the effectiveness of guard traces on crosstalk reduction for single-ended traces. Because the use of guard traces continues to arise in situations with high-speed designs, it's useful to examine how guard traces affect crosstalk with 50 Ohm single-ended traces as these would normally be implemented as the standard in high-speed buses and RF interconnects (for example, in SDRAM/DDR). In other instances with SPI or PPI, there is no impedance specification, but very long traces could be designed to 50 Ohms and have termination applied.

The important result that was found by Bogatin and Simonovich is that the level of crosstalk found in the simulations depended on whether the traces were routed as 50 Ohm striplines or microstrip, as well as whether the traces are shorted, open, or connected to 50 Ohm termination at each end. For convenience, I am showing their time-domain results below, which show the relative effectiveness or ineffectiveness of guard traces in both configurations.

Bogatin, E., Simonovich, B., Guard Traces: Love Them or Leave Them? Signal Integrity Journal, 5 September 2019.

The results are very clear: the only effective guard trace configuration is in stripline with both ends shorted to ground, specifically for NEXT. For FEXT, there does appear to be a crosstalk reduction for a shorted guard trace in stripline, but the crosstalk was already very low anyways.

The results shown here are valid for 50 Ohm single-ended traces, but the same results can be seen for a differential pair separated by guard traces. The difference is that we would be looking at differential crosstalk, where a differential signal can create both differential and common-mode noise on the victim interconnect.

To read the full study and to learn more about this issue with single-ended traces, read the following article in Signal Integrity Journal:

When you’re looking for the best software package for high-speed PCB design, use the complete set of design tools in Altium. The integrated design rules engine and layer stack manager give you everything you need to create a circuit board that has low crosstalk and controlled impedance. When you’ve finished your design, and you want to release files to your manufacturer, Altium makes it easy to collaborate and share your projects.