Diretrizes de Layout, Roteamento e Integridade de Sinal para PCB DDR5

O lançamento do padrão DDR5 foi anunciado em julho de 2020, cerca de 18 meses após o anúncio do desenvolvimento do primeiro módulo de RAM seguindo o padrão proposto. O padrão permite velocidades de pico superiores a 5200 MT/seg/pino (compare isso com 3200 MT/seg/pino com DDR4), com velocidades avaliadas pela JEDEC de até 6400 MT/seg/pino e largura de banda do canal aumentada para até 300 GB/s. A demanda por essa nova geração de memórias com capacidades de 8, 16 e 32 GB deve superar a das gerações anteriores à medida que a tecnologia se torna mais comercializada.

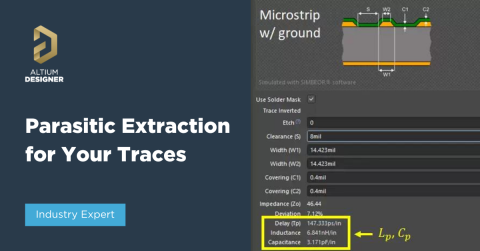

As velocidades mais rápidas, as tensões de alimentação mais baixas e as maiores perdas no canal criam margens e tolerâncias estritas no layout e design de PCB DDR5, mas a integridade de sinal dos canais DDR5 ainda pode ser avaliada com métricas comuns de integridade de sinal. Há muito a cobrir nesta área, mas neste artigo nos concentraremos nas diretrizes essenciais de layout e roteamento de PCB DDR5 que ajudarão a garantir a integridade do sinal em DDR5, bem como nas importantes métricas de integridade de sinal nos canais DDR5.

Diagramas de Olho DDR5 e Respostas de Impulso

Existem duas simulações importantes que são usadas para examinar a integridade do sinal em canais DDR5: um diagrama de olho e a resposta ao impulso. Um diagrama de olho pode ser simulado ou medido, assim como uma resposta ao impulso em um canal terminado. Ambos medem a capacidade de um canal de transmitir um único bit e um fluxo de bits através de um canal, e permitem que o modelo analítico para um canal seja avaliado em termos de causalidade. A tabela abaixo resume as informações importantes que podem ser determinadas a partir dessas medições/simulações.

|

|

|

|

|

|

|

|

|

|

|

|

Para saber mais sobre algumas das especificações técnicas de canais DDR5 em uma breve comparação com gerações anteriores de DDR, confira este artigo.

Diagramas de Olho na Integridade de Sinal DDR5

As principais métricas extraídas de um diagrama de olho são a abertura do olho e a taxa de erro de bits (BER). A abertura do olho pode ser traçada no centro do olho e é tipicamente usada como uma medida da qualidade do canal. Os pontos importantes que podem ser diretamente extraídos dos cruzamentos de sinal são o jitter de amplitude e o jitter de tempo, ambos indicativos de ISI e algumas fontes de distorção ou perdas. Quando o jitter de tempo e o ruído de amplitude são altos, o diagrama de olho será mais fechado. Melhorar as principais métricas de integridade do sinal no canal (perdas, dispersão dielétrica, estendendo a largura de banda de correspondência de impedância para frequências mais altas) deve melhorar ambas as métricas mencionadas e, assim, abrir mais completamente o olho, levando a uma menor taxa de erro de bits.

Respostas de Impulso na Integridade de Sinal DDR5

Respostas impulsivas consideram a resposta de um canal isoladamente quando alimentado com um pulso rápido. Embora seja importante avaliar um fluxo de bits pseudorrandômico como você faria em um diagrama de olho, uma resposta impulsiva é mais fundamental. Ela revela informações sobre como um canal transmite um único bit com uma taxa de borda específica (largura de banda) através do canal e para o receptor. A resposta impulsiva do canal dependerá da impedância do canal, da largura de banda de terminação comparada à largura de banda do sinal, das perdas totais no canal e da dispersão. Os sinais DDR5 têm um foco maior na perda dependente de reflexão no receptor do que os canais seriais típicos, o que pode ser visto na taxa de borda de uma resposta impulsiva.

O motivo importante para usar uma simulação de resposta impulsiva para um projeto de canal DDR5 proposto ou de um modelo de canal extraído é avaliar a causalidade do canal. O modelo determinado a partir dos parâmetros-S do canal poderia produzir uma resposta não causal no canal, e assim, alguma correção (janelamento) seria necessária para modificar o modelo do canal se artefatos não causais estiverem presentes. Leia mais sobre isso em um artigo recente de Jason Ellison.

Um processo de análise de SI em um canal DDR5 (ou qualquer outro canal de alta velocidade) incluiria:

- Projeto de canal e teste/simulação

- Extração de modelo a partir da resposta impulsiva simulada em onda completa, ou a partir de medições de parâmetros-S

- Verificação e correção da causalidade do modelo

- Simulação e teste de diagrama de olho

- Modificar o projeto do canal

- Repetir até que a conformidade do canal seja alcançada

Equalização de Feedback de Decisão (DFE) nas Linhas DQ

Uma das maiores mudanças (na minha opinião) na arquitetura DDR é o uso de equalização de feedback de decisão (DFE) para superar as perdas no canal e dispersão nas linhas DQ em um barramento DDR5. Conceitualmente, a maneira mais fácil de superar a distorção em sinais digitais é passar o sinal atenuado por um filtro de passa alta. É por isso que um filtro RC paralelo pode ser usado como um equalizador simples. Mas em DDR5, onde as larguras de banda do sinal digital são muito maiores, o DFE é mais eficaz e é incorporado no lado de recepção de um canal. A razão para o uso do DFE é que esses canais podem precisar ser relativamente curtos comparados aos canais seriais, e o DFE é eficaz quando as perdas por reflexão são significativas nas perdas totais do canal.

O DDR5 continuará a incluir redes de terminação única, mas idealmente elas deveriam ter um comprimento de canal mais curto do que uma geração anterior de DDR. Nas altas velocidades presentes nos canais DDR5, o comportamento dominado por reflexões e a dispersão se combinam para produzir uma interferência significativa entre símbolos (intersymbol interference - ISI) se as trilhas não forem adequadamente terminadas, como ilustrado acima na seção sobre respostas a impulsos. A ISI causa distorções nos níveis de sinal além da distorção de forma devido à dispersão e reflexões, e cada pulso digital começa a parecer um pulso meio-Gaussiano no lado de recepção em um canal não equalizado. O resultado final é que o diagrama de olho para o canal começa a fechar à medida que as perdas dominadas por reflexões e a distorção relacionada à dispersão se acumulam.

Para superar a distorção do sinal e a ISI, um esquema de equalização é incorporado à arquitetura DRAM, seja no lado de transmissão ou de recepção, similar ao caso de alguns controladores DDR3 e DDR4. A equalização por feedback de decisão (DFE) ou a equalização linear contínua no tempo (CTLE) podem ser usadas no lado de recepção, ou a equalização feed-forward (FFE) pode ser usada no lado de transmissão. Note que a CTLE não é ideal para canais dominados por reflexões, assim o DDR5 adota o DFE como o método de equalização.

Medição do diagrama de olho.

Diretrizes de Layout de PCB DDR5 para Redução da Degradação do Sinal

Existem outras fontes de ruído em canais DDR5 que se tornam ainda mais problemáticas do que nas gerações anteriores, especialmente considerando as velocidades mais altas necessárias para acomodar as maiores taxas de dados e larguras de banda de sinal. Há três principais diretrizes de layout de PCB DDR5 que terão prioridade nesses designs.

- Controle preciso de terminação e impedância que se estende a larguras de banda altas é necessário para suprimir reflexões dentro da largura de banda requerida.

- A entrega de energia também é crítica no design de PCB DDR5. Os módulos DDR5 incluirão um IC de gerenciamento de energia que recebe 12 V e fornece 1.1 V para os ICs DIMM. Isso transfere a integridade da energia para o nível do módulo DDR5 e afasta da placa-mãe.

- Opte por caminhos mais curtos devido à atenuação nos canais DDR5. Um laminado de alta velocidade de baixa perda pode ser benéfico, ou laminados com tecidos de vidro espalhados para minimizar os efeitos da trama de fibra em larguras de banda altas.

No lado da simulação, uma ferramenta de simulação de diafonia pós-layout que utiliza modelos IBIS para seus componentes pode ajudar a avaliar a integridade do sinal nos seus canais de sinal DDR5. A diafonia pode ser usada para determinar se o espaçamento entre linhas é apropriado, dado o empilhamento e a distância até a referência para as linhas de sinal. A mesma ferramenta de simulação pode ser usada para analisar reflexões, o que é importante em uma topologia multi-drop dominada por reflexões encontrada no DDR5, embora isso dependa menos dos modelos IBIS e mais da modelagem do sinal injetado em um canal, o que poderia ser feito numericamente no simulador adequado.

GDDR5 para uma GPU

As poderosas ferramentas de layout e roteamento de PCB em Altium Designer® são projetadas para aplicações como canais SerDes, design de PCB DDR5 e outras áreas avançadas. O Altium Designer inclui um poderoso gerenciador de empilhamento com um solucionador de campo para controlar a impedância na sua placa durante o roteamento, e você terá acesso a ferramentas de simulação pós-layout que ajudarão a identificar problemas de integridade de sinal na sua placa.

Agora você pode baixar uma versão de avaliação gratuita do Altium Designer e saber mais sobre as melhores ferramentas de layout, simulação e planejamento de produção do setor. Fale hoje mesmo com um especialista da Altium para aprender mais sobre as diretrizes de layout e roteamento de PCB DDR5.