Power Plane and Ground Planes: Should You Use Your PCB Power Plane as a Return Path?

Power planes (sometimes called a power layer) and ground planes are important for more than just distribution of supplying power. When defining reference planes, both with impedance controlled routing and in managing return paths, your stackup might force return currents to pass into a PCB power plane before being coupled back to a ground layer. Even though you define a GND reference layer as a the basis for your impedance-controlled trace width, you still have to define a clear return path along the length of the power layer in your design. Let’s take a look at some good practices for controlling return paths in your PCB with a power layer as a return path.

Signal Behavior with a PCB Power Plane as a Return Path

When we say "return path," we're referring to the path that is naturally followed by the return current in a design, where by the current can travel back to the low potential terminal at the input side of the PCB assembly. For a signal traveling on a transmission line, the return path is determined by the capacitance between the line and its reference plane. A higher capacitance, higher frequency, or both means that the return current can easily pass into the ground layer as a displacement current.

This, in turn, means that the distance between a transmission line and its reference plane, whatever that type of reference plane happens to be, determines some important electrical behavior in real designs. Such behavior includes:

- EMI susceptibility from external sources, which can be received inductively through a large current loop, or capacitively via the electric field

- Inconsistent impedance, which will arise when routing between plane regions, over gaps, or with varying trace widths along an interconnect

- Crosstalk from other traces, which can more easily couple inductively into a victim trace if the design has a

- Losses during propagation, which occurs due to field line concentration between the transmission line and the nearby reference plane or other conductors

If you can choose between using a power plane or ground plane as the adjacent layer that provides a return path or signal reference, you should always choose the PCB ground plane. There are two reasons for this, which I’ll explain in more detail below.

Capacitive Coupling

Before discussing how a power plane does (or doesn't) actually function as any kind of return path, we have to ask the question: how would current from a transmission line get into the power plane PCB to begin with. The answer is: capacitive coupling! Remember, as was mentioned above, the return path is induced between a transmission line and any nearby conductor. For a nearby plane layer, this happens whenever there is a changing electric potential between the line and the plane. Therefore, whenever we have a trace being routed next to a plane, and a digital signal travels along that trace, we now have a displacement current being driven in the plane layer.

If the nearby plane were a ground plane at the same potential as our low potential point at the power input, then everything would be great. The problem with this is, when the current needs to then pass from a power plane and into the nearby ground layer, the current will need to bridge through another dielectric layer to reach a PCB ground plane.

Depending on how the stackup is designed and the area in the board where the signal is induced, the capacitance between the two layers could form a very high impedance path between the power plane and the ground plane. Depending on the stackup, such as the simple 4-layer stackup shown below, the plane capacitance between the power layer and PCB ground plane layer could be very small (on the order of femtofarads per sq. mm), creating an extremely high impedance return path except for extremely fast digital signals or very high frequency RF signals. The only other option in this journey between the power plane and the ground plane is through the nearest decoupling capacitor, as shown below. In either case, you could have an EMI problem somewhere in the board.

For typically lower-speed single-ended signals (such as rise time-limited I2C or SPI signals), the EMI generated from this coupling to GND might not be the biggest problem. This doesn't happen at all with purely DC or low frequency analog devices. However, with today's standard CMOS components, even single-ended buses in common digital components can have this problem. So what's the solution?

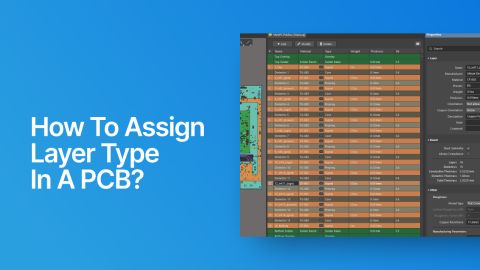

The answer is found in redesigning the PCB stackup. The simplest path forward is to add layers that provide the ground return. Generally, there will be no other design changes needed as long as all the GND planes are stichted together with appropriately spaced stitching vias. Something that is more time-consuming from a design perspective, such as in the above 4-layer stackup, is to place PWR and Signal on the same layer, and then add in the PWR on the same layer as pour.

4-Layer Example

In the example 4-layer board above, the stackup is best used if the buses and lines that must provide continuous bit streams are placed on the top layer directly above GND. Other signals, such as control signals that can be slowed down with RC or series termination, can be placed on the back layer, as well as other supporting components. However, if you need to have a 4-layer PCB with digital buses on both surface layers, then the best practice is to use an alternative stackup.

The stackup below is arguably the best alternative to suppress noise and provide clear return paths everywhere. This is the SIG+PWR/GND/GND/SIG+PWR stackup, where signal and power are routed on the top layers. This provides very strong decoupling for power rails because they will (or should) be placed close to the GND plane on the adjacent layer.

There is one difficulty in this board, which can arise when there are multiple power rails. In the case where your 4-layer board needs to have high-speed signals on both layers, as well as multiple power rails and strong power integrity, the standard SIG/GND/PWR/SIG stackup will not work. This is where adding two layers and building a 6-layer stackup is the best option.

6-Layer Example

Like most routing and layout problems, which then create EMI problems, the source of the problem is usually one of defining ground, or having the wrong layer arrangement in the PCB stackup. Although you can use the power plane as an impedance reference and return path for signals, you’ll need to place a nearby PCB ground plane to prevent coupling between layers in the type of layer stack shown below.

One stackup that is sometimes used in denser designs is the 6-layer stackup shown below. The top and bottom signal layers are coupled directly to ground, yet we still have a power plane (in blue on L3) that might have high plane capacitance to ground on L2, depending on layer thicknesses.

An alternative layer arrangement that is not ideal with high speed routing on an internal layer is to have two adjacent signal layers and power on L2. This could allow internal crosstalk and create problems getting the return current back to ground if the signals are not segmented into different regions in the PCB. A better arrangement would be to use the 6 layer board shown above.

What about coupling directly into traces? Normally, the parasitic capacitance between the neighboring layers can be quite small due to the small dimensions of signal traces, creating a somewhat high impedance return path between any return current in the power plane on L3 and the ground plane on L5. The normal way to provide a low impedance return path between any return current in the power layer and the ground plane is to place a decoupling/bypass capacitor between the power/ground planes. In the above example, the preferable low-impedance path for any return current induced in the power plane is directly into ground on L2, not on L5.

The Takeaway: Engineer Your Return Path

Whether you allow signals to couple back to the power plane followed by capacitive coupling into the nearest PCB ground plane, or back to the ground plane directly, you’ll need to carefully engineer your return path to prevent undesired coupling between any return signal. The important point here is that any circuit in your board is complete when it connects back to the PCB ground plane, regardless of whether this coupling is direct, through decoupling/bypass capacitors, or thanks to interplane capacitance. This is why, in modern PCBs, we always say to route adjacent to a ground plane: this allows the return path to be sent directly to the ground plane without using bypass caps, stitching vias with copper pour, or other measures that don't solve the problems created by a bad stackup.

While you can technically take advantage of a power plane as a shielding layer and a PCB reference plane (assuming the potential difference between the signal track and the power plane is not 0 V), it becomes difficult to control the return path in general. This is particularly true with high-speed/high-frequency boards. In more advanced designs that run at low signal levels, you might be using differential pairs, in which case the return path is provided by differential driving, i.e., it flows parallel to the HIGH signal trace. If you’re interested in learning more about tracing the return path in your board, take a look at this article from Francesco Poderico.

The newest PCB layout and routing tools in Altium Designer® include a ground return path tool that interfaces with the DRC engine. This allows you to define limits on the deviation between a trace and its nearest PCB reference plane as a design rule. This rule is checked automatically by the interactive routing tools as you create your board. You’ll also have a complete set of tools for analyzing signal integrity and preparing manufacturer deliverables.

Now you can download a free trial of Altium Designer and learn more about the industry’s best layout, simulation, and production planning tools. Talk to an Altium expert today to learn more about your power layer and power plane PCBs in general.