Deve-se Remover o Terra Abaixo das Redes de Correspondência de Impedância?

Em uma rede de casamento de impedância, o objetivo é ajustar a resistência, capacitância e indutância do circuito de modo que a transferência de potência ou tensão para uma carga seja maximizada. Controlar esses fatores em torno de um circuito de casamento de impedância em uma PCB é tudo sobre o posicionamento e dimensionamento de trilhas e terra, bem como a correspondência destes com os pads em seus componentes discretos. Para eliminar parasitas adicionais do tamanho do pad e das trilhas conectando a esses componentes, às vezes é necessário modificar onde o terra é colocado ao redor dos componentes do circuito de casamento de impedância.

Por Que o Terra Pode Ser Removido

Em muitos sistemas, é comum construir circuitos de casamento de impedância a partir de componentes discretos, geralmente passivos SMD. Às vezes, quando o terra é removido abaixo de uma rede de casamento de impedância, não estamos eliminando completamente o terra abaixo desses circuitos. Isso ocorre porque as linhas de alimentação que entram e saem do circuito precisam ter uma impedância alvo (geralmente 50 Ohms), então o terra ainda é necessário no dispositivo. Suas opções para modificar o posicionamento do terra incluem:

- Usando terra em uma camada inferior na PCB, e

- Colocando terra coplanar ao redor da rede de casamento de impedância

A razão para fazer isso é bastante simples: queremos reduzir a quantidade de capacitância e indutância parasitas adicionais ao redor dos componentes do circuito de casamento de impedância. É bem conhecido que os parasitas modificam o desempenho de passivos reais em circuitos de alta frequência, criando um limite na perda de retorno esperada em cada porta. Infelizmente, você nunca pode se livrar dessa capacitância de pad/trace em componentes SMD, você só pode tentar minimizar para que o circuito opere o mais próximo possível do desempenho teórico.

Portanto, em alguns casos, pode fazer sentido modificar onde o terra é colocado ao redor desses componentes. Queremos garantir que os tamanhos dos pads e traces nos componentes não criem capacitância parasita adicional excessiva que modifica a impedância dos capacitores e indutores na rede de casamento de impedância.

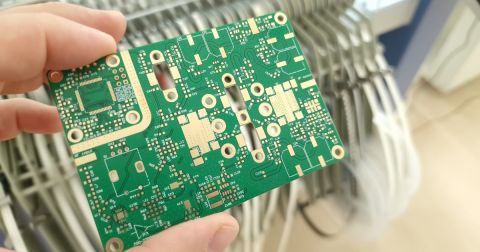

Terra Liberada em um Layout de PCB RF

O exemplo abaixo, de nosso projeto anterior nRF52, mostra como o terra pode ser limpo; o circuito de casamento de filtro pi é mostrado abaixo. Note que isso se alinha bem com as diretrizes da placa de referência nRF52 da Nordic. Aqui, terra coplanar é usado em L1, e há um terra uniforme abaixo da rede de casamento de impedância em L6. O terra é limpo apenas abaixo da região da rede de casamento, e somente em L2-L5.

Se olharmos acima, os pads dos componentes têm alguma capacitância de volta para o terra; isso adiciona capacitância aos capacitores discretos no circuito de casamento de impedância. A mesma ideia se aplica à indutância envolvendo o terra e a indutância de condução dos componentes. Como limpamos o terra sem impactar a impedância da linha?

Primeiro, podemos usar terra coplanar ao redor das trilhas para definir sua impedância característica para a impedância alvo, combinando com a saída do chip. Um recorte poligonal é usado abaixo da linha de alimentação apenas nas camadas internas. A camada inferior tem um preenchimento uniforme de cobre abaixo do circuito de casamento de impedância. A camada superior também tem preenchimento de cobre, mas a regra de distância padrão foi aplicada ao redor das trilhas e pads nessas redes para definir a impedância característica das trilhas para o valor alvo.

Agora, vamos olhar para um exemplo dado o layout RF mostrado acima.

Quão Grande é o Desvio?

Para determinar o desvio, podemos comparar o caso teórico com o caso real. Inicialmente, temos um capacitor 0402 e um indutor 0603. Se tivéssemos o terra diretamente abaixo desses pads e das trilhas de conexão, os parasitas no capacitor seriam de cerca de 3 pF/polegada e 7,5 nH/polegada em laminado Dk = 4. Com a configuração coplanar e o terra apenas em L6 mostrado acima, os parasitas caem para cerca de 2,75 pF/polegada e 6,9 nH/polegada. Podemos realizar cálculos semelhantes para os pads do indutor.

A capacitância parasita total e a indutância dadas os valores de elementos distribuídos acima são resumidos abaixo. Note que isso só leva em conta as trilhas ao redor dos componentes e os pads; isso não leva em conta a autoindutância dos leads do pacote.

|

|

|

|

|

|

|

|

|

|

|

|

Uma simples mudança na localização do terra de L2 para L6 reduz a capacitância parasita em 22,4%. Com esses valores, agora é possível incluir essas parasitas em uma simulação e determinar o efeito delas na impedância de saída da rede.

O cálculo da indutância é um pouco mais complicado porque envolve alguma indutância de laço ao redor dos pads, bem como indutância de condução, ambos podem não ser tão fáceis de determinar. A autoindutância do traçado em série com o indutor também desempenha um papel na determinação da indutância total. Em geral, não é seguro apenas assumir que a indutância modificada compensa a capacitância modificada.

Note acima que incluí uma opção para todos os componentes 0402 em vez do indutor 0603. Podemos ver que há uma redução na capacitância parasita dos pads e traçados simplesmente porque o indutor 0603 tem pads maiores que o indutor 0402. Este exemplo modificado é mostrado abaixo.

Obtemos um pouco menos de capacitância parasita com este arranjo, mas não é muito; é apenas uma redução de 6,8% comparado aos tamanhos de pacote mistos. Em todos esses diferentes casos, é importante agora determinar se isso importará no seu sistema específico.

Essa Divergência Importa?

Para determinar se essa capacitância e indutância parasitas são importantes, temos que comparar os valores com os valores dos componentes colocados no layout da PCB.

No exemplo do nRF52 acima, os valores dos capacitores usados na rede de casamento eram de 1,2 pF. Com uma capacitância adicional de 0,4388 pF, essa rede age como se tivesse uma capacitância total de 2,8388 pF. O resultado é uma redução de cerca de 5 Ohms de impedância da impedância alvo. Suponha por um momento que o circuito sem parasitas estivesse perfeitamente casado com 50 Ohms; se estivéssemos usando essa rede de casamento de impedância real para transformar para uma impedância alvo de 50 Ohms, a perda de retorno resultante seria S11 = -27,5 dB.

E se nossos capacitores fossem de 1,2 nF? Neste caso, a capacitância parasita adicional é praticamente imperceptível e não teria efeito no nosso filtro pi. Em geral, se a capacitância parasita adicional for muito menor do que a capacitância discreta, então ela pode ser ignorada; a mesma ideia se aplica à indutância.

Note-se que este design com o indutor 0603 foi testado em uma placa de cliente e verificou-se que opera dentro das especificações, então eu me sentiria confortável em usar a mesma rede neste projeto. No entanto, os pontos destacados acima devem ser considerados se você quiser usar este design em seus próprios projetos. Os conceitos acima são bastante importantes para componentes práticos operando na faixa de 1-6 GHz, onde redes de casamento de impedância são necessárias.

A razão pela qual o terra pode ser removido mais frequentemente em sistemas operando na faixa de 1-6 GHz é que os capacitores usados nessas redes de casamento de impedância podem ser bastante pequenos (~1 pF). O ~1 pF de capacitância discreta na rede é semelhante à capacitância parasita esperada ao redor de uma linha de 50 Ohms em laminado Dk ~ 4. Essa capacitância parasita essencialmente existe em paralelo com a capacitância discreta, e juntos isso poderia modificar a condição de casamento.

Onde está a Rede de Casamento em Frequências Mais Altas?

Em frequências superiores às do WiFi, você pode não ver nenhuma rede de casamento de impedância em suas interconexões RF que se destinam a operar a 50 Ohms. Existem duas razões importantes para isso:

- A maioria dos ICs de RF incorporará sua rede de correspondência de impedância no próprio chip

- . Circuitos de RF ou antenas tendem a ser construídos especificamente para operar na impedância alvo.

Tomemos como exemplo os transceptores de radar. Existem milhões de automóveis e sensores especializados que usam esses transceptores, e em todas essas placas, você não verá nenhuma rede de correspondência de impedância na PCB. Nestes sistemas, nos preocupamos com a capacitância parasita ao redor da PCB, e em particular nos amplificadores de RF de alta potência, mas não estamos colocando redes de correspondência de impedância com pequenos componentes discretos na PCB, e certamente não estamos limpando o terra abaixo dos pinos de transmissão e recepção.

Agora considere a antena patch alimentada em série operando em ~77-78 GHz mostrada abaixo. Esta antena é intencionalmente projetada para operar a 50 Ohms. Normalmente, uma antena patch individual (ou simples antena microstrip impressa) poderia ter uma impedância de entrada de 200-300 Ohms. A razão pela qual a antena abaixo tem uma impedância de entrada de 50 Ohms deve-se ao seu pequeno tamanho e ao uso de linhas de correspondência de comprimento de onda fracionário para conectar os patches. Isso também confere a larga largura de banda de emissão, como mostrado no gráfico de perda de retorno abaixo.

Apresento esses exemplos para ilustrar o seguinte ponto importante: não se surpreenda se você não encontrar uma rede de casamento de impedância construída a partir de componentes discretos quando seu sistema RF opera em frequências muito altas. Esses componentes geralmente incluirão terra abaixo de seus pinos TX e RX, bem como um lançamento de sinal mais complexo localizado ao redor do pino de montagem na PCB.

Sempre que precisar projetar um layout de PCB RF com uma rede de casamento de impedância, certifique-se de usar o conjunto completo de ferramentas de design e produção de PCBs no Altium Designer®. Uma vez que você tenha terminado o layout da sua PCB e estiver pronto para compartilhar seus entregáveis de fabricação, você pode facilmente compartilhar dados e liberar arquivos para sua equipe com a plataforma Altium 365™.

Apenas arranhamos a superfície do que é possível com o Altium Designer no Altium 365. Inicie seu teste gratuito do Altium Designer + Altium 365 hoje.