インピーダンス整合ネットワークの下のグラウンドを取り除くべきですか?

インピーダンス整合ネットワークでは、回路の抵抗、容量、およびインダクタンスを調整して、負荷への電力または電圧の伝達を最大化することが目標です。PCB内のインピーダンス整合回路周辺でこれらの要因を制御することは、トレースとグラウンドの配置とサイズ、およびこれらをディスクリートコンポーネントのパッドに合わせることに関係しています。パッドサイズとこれらのコンポーネントに接続するトレースから追加の寄生を排除するために、時にはインピーダンス整合回路コンポーネントの周りでグラウンドの配置を変更する必要があります。

グラウンドが取り除かれる理由

多くのシステムでは、通常SMDパッシブからインピーダンス整合回路を構築することが一般的です。時には、インピーダンス整合ネットワークの下のグラウンドをクリアするとき、これらの回路の下のグラウンドを完全に排除しているわけではありません。これは、回路に入出力されるフィードラインが目標インピーダンス(通常は50オーム)である必要があるため、デバイス内には依然としてグラウンドが必要だからです。グラウンドの配置を変更するオプションには次のようなものがあります:

- PCBの下層にグラウンドを使用し、

- インピーダンス整合ネットワークの周りに共面グラウンドを配置する

これを行う理由は非常にシンプルです。インピーダンス整合回路のコンポーネント周りの追加の寄生容量とインダクタンスの量を減らしたいからです。高周波回路において、寄生要素が実際の受動部品の性能を変化させ、各ポートで期待されるリターンロスの限界を作り出すことはよく知られています。残念ながら、SMDコンポーネントのパッド/トレース容量を完全に取り除くことはできませんが、回路が理論的な性能にできるだけ近く動作するように、最小限に抑えることしかできません。

したがって、場合によっては、これらのコンポーネントの周りにグラウンドを配置する場所を変更することが理にかなっています。コンポーネントのパッドとトレースのサイズが、インピーダンス整合ネットワーク内のキャパシタとインダクタのインピーダンスを変更する過剰な追加の寄生容量を生み出さないようにしたいのです。

RF PCBレイアウトにおけるクリアードグラウンド

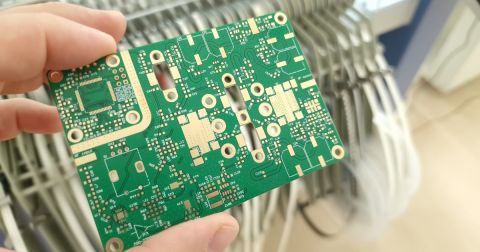

以下の例は、以前のnRF52プロジェクトからのもので、グラウンドがどのようにクリアされるかを示しています。下に示すのは、πフィルターマッチング回路です。これは、NordicのnRF52リファレンスボードのガイドラインとよく一致しています。ここでは、L1に共面グラウンドが使用されており、インピーダンスマッチングネットワークの下にはL6に均一なグラウンドがあります。グラウンドはマッチングネットワーク領域の下でのみクリアされ、L2-L5にのみ適用されます。

上を見ると、コンポーネントのパッドにはグラウンドに戻るいくらかの容量があり、これがインピーダンスマッチング回路の離散キャパシタに容量を追加します。同じ考え方が、グラウンドとコンポーネントのリードインダクタンスに関わるインダクタンスにも適用されます。線のインピーダンスに影響を与えずにグラウンドをどのようにクリアしますか?

まず、トレースの周りに共面グラウンドを使用して、チップの出力にマッチする目標インピーダンスに特性インピーダンスを設定できます。内部層にのみフィードラインの下にポリゴンカットアウトが使用されます。ボトムレイヤーには、インピーダンスマッチング回路の下に均一な銅の注ぎ込みがあります。トップレイヤーにも銅の注ぎ込みがありますが、これらのネット上のトレースとパッドの周りに標準のクリアランスルールが適用されており、トレースの特性インピーダンスを目標値に設定するためです。

それでは、上に示されたRFレイアウトの例を見てみましょう。

逸脱の大きさはどれくらいですか?

逸脱を決定するために、理論的なケースと実際のケースを比較することができます。初めに、0402キャパシタと0603インダクタを持っています。これらのパッドと接続トレースの直下にグラウンドがあれば、キャパシタの寄生容量は約3 pF/インチ、Dk = 4のラミネート上のインダクタは約7.5 nH/インチになります。上に示されたL6のみにグラウンドがある共面構成では、寄生容量は約2.75 pF/インチ、寄生インダクタンスは約6.9 nH/インチに減少します。インダクタパッドに対しても同様の計算を行うことができます。

上記の分布要素値を考慮した総寄生容量とインダクタンスは以下の通りです。これはコンポーネント周辺のトレースとパッドのみを考慮したもので、パッケージリードの自己インダクタンスは考慮していません。

|

|

|

|

|

|

|

|

|

|

|

|

グラウンドの位置をL2からL6に変更するだけで、寄生容量が22.4%減少します。これらの値を使用して、これらの寄生要素をシミュレーションに含め、ネットワークの出力インピーダンスに対する影響を判断することができるようになります。

インダクタンスの計算はもう少し複雑です。これは、パッド周りのループインダクタンスやリードインダクタンスなど、簡単に判断できない要素が関与するためです。インダクタと直列のトレース自体のインダクタンスも、全体のインダクタンスを決定する上で役割を果たします。一般に、修正されたインダクタンスが修正された容量を補償すると単純に仮定するのは安全ではありません。

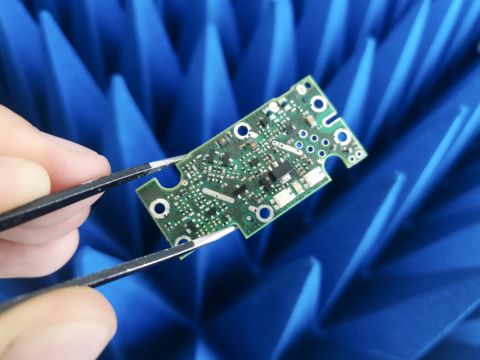

上記で、0603インダクタの代わりにすべての0402コンポーネントを含むオプションを追加したことに注意してください。0402インダクタは0603インダクタよりもパッドが小さいため、パッドとトレースからの寄生容量が減少することがわかります。この修正例を以下に示します。

この配置では寄生容量がわずかに減少しますが、それほど多くはありません。混合パッケージサイズと比較して6.8%の減少に過ぎません。これらの異なるケースすべてにおいて、特定のシステムでこれが重要かどうかを今判断することが重要です。

この逸脱は重要ですか?

この寄生容量と寄生インダクタンスが重要かどうかを判断するためには、PCBレイアウトに配置されたコンポーネントの値と比較する必要があります。

nRF52の上記の例では、マッチングネットワークに使用されたキャパシタの値は1.2 pFでした。追加の容量が0.4388 pFの場合、このネットワークは合計容量が2.8388 pFのように動作します。結果として、目標インピーダンスから約5オームのインピーダンス低下があります。寄生がない回路が完全に50オームにマッチしていたと仮定すると、この実際のインピーダンスマッチングネットワークを使用して50オームの目標インピーダンスに変換する場合、結果として得られるリターンロスはS11 = -27.5 dBになります。

もし私たちのキャパシタが1.2 nFだったらどうでしょうか?この場合、追加の寄生容量はほとんど気にならず、πフィルターには影響しません。一般に、追加の寄生容量が離散容量よりもはるかに小さい場合、それは無視できます。同じ考え方がインダクタンスにも適用されます。

この設計は0603インダクターを使用しており、クライアントのボードでテストされ、仕様内で動作することが確認されましたので、このプロジェクトでも同じネットワークを使用することに問題はないと思います。しかし、あなたのプロジェクトでこの設計を使用したい場合は、上記の点を考慮する必要があります。上記の概念は、インピーダンスマッチングネットワークが必要とされる1-6 GHz範囲で動作する実用的なコンポーネントにとって非常に重要です。

1-6 GHz範囲で動作するシステムでグラウンドがより頻繁に取り除かれる理由は、これらのインピーダンスマッチングネットワークで使用されるキャパシタが非常に小さい(〜1 pF)ためです。ネットワーク内の約1 pFの離散キャパシタンスは、Dk ~ 4のラミネート上の50オーム線周辺の予想される寄生キャパシタンスと似ています。この寄生キャパシタンスは、離散キャパシタンスと並列に存在し、これによってマッチング条件が変更される可能性があります。

高周波でのマッチングネットワークはどこにあるのか?

WiFiよりも高い周波数では、50オームで動作することを意図したRFインターコネクト上にインピーダンスマッチングネットワークが見られないことがあります。これには2つの重要な理由があります:

- ほとんどのRF ICは、ダイ

- 上にインピーダンス整合ネットワークを組み込むでしょう。RF回路やアンテナは、目標とするインピーダンスで動作するように特別に構築される傾向があります。

レーダートランシーバーを例にとってみましょう。これらのトランシーバーを使用する自動車や特殊センサーが数百万台ありますが、これらのボードのどれにもPCB上にインピーダンス整合ネットワークは見られません。これらのシステムでは、PCB周辺の寄生容量、特に高電力RFアンプ上の寄生容量について懸念していますが、PCB上に小さな離散コンポーネントでインピーダンス整合ネットワークを配置したり、駆動ピンや受信ピンの下のグラウンドをクリアすることはありません。

次に、以下に示される約77-78 GHzで動作する直列給電パッチアンテナを考えてみましょう。このアンテナは意図的に50オームで動作するように設計されています。通常、個々のパッチアンテナ(または単純なプリントマイクロストリップアンテナ)は、入力インピーダンスが200-300オームになることがあります。以下のアンテナが50オームの入力インピーダンスを持つ理由は、その小さなサイズと分数波長整合線を使用してパッチをリンクすることによります。これにより、以下に示されるリターンロスプロットで示されるような広い放射帯域幅も得られます。

これらの例を挙げる理由は、次の重要な点を説明するためです:RFシステムが非常に高い周波数で動作する場合、離散コンポーネントから構成されるインピーダンスマッチングネットワークを見かけないことに驚かないでください。これらのコンポーネントは一般的に、TXおよびRXピンの下にグラウンドを含み、PCB上の取り付けピン周辺により複雑な信号の発射を配置します。

インピーダンスマッチングネットワークを備えたRF PCBレイアウトを設計する必要がある場合は、Altium Designer®の完全なPCB設計および製造ツールセットを使用してください。PCBレイアウトを完成させ、製造デリバラブルを共有する準備ができたら、Altium 365™プラットフォームを使用して、データを共有し、リリースファイルをチームと簡単に共有できます。

Altium DesignerとAltium 365で可能なことの表面をかすめただけです。今日からAltium Designer + Altium 365の無料トライアルを開始してください.