Bạn Có Nên Loại Bỏ Mặt Đất Dưới Mạng Lưới Điều Chỉnh Trở Kháng Không?

Trong mạng lưới khớp trở kháng, mục tiêu là điều chỉnh trở kháng, dung kháng, và cảm kháng của mạch sao cho việc truyền công suất hoặc điện áp tới tải được tối đa hóa. Việc kiểm soát những yếu tố này xung quanh một mạch khớp trở kháng trên PCB đều liên quan đến việc đặt và kích thước của các đường dẫn và mặt đất, cũng như việc khớp chúng với các pad trên các linh kiện rời. Để loại bỏ thêm các yếu tố nhiễu từ kích thước pad và các đường dẫn kết nối với những linh kiện này, đôi khi bạn cần phải chỉnh sửa vị trí đặt mặt đất xung quanh các linh kiện của mạch khớp trở kháng.

Tại Sao Lại Cần Loại Bỏ Mặt Đất

Trong nhiều hệ thống, việc xây dựng các mạch khớp trở kháng từ các linh kiện rời, thường là các linh kiện SMD bị động, là phổ biến. Đôi khi, khi mặt đất được loại bỏ phía dưới mạng lưới khớp trở kháng, chúng ta không hoàn toàn loại bỏ mặt đất phía dưới những mạch này. Điều này là bởi vì các đường dẫn vào và ra khỏi mạch cần phải có trở kháng mục tiêu (thường là 50 Ohm), vì vậy mặt đất vẫn cần thiết trong thiết bị. Các lựa chọn của bạn để chỉnh sửa vị trí của mặt đất bao gồm:

- Sử dụng mặt đất ở lớp dưới của PCB, và

- Đặt mặt đất đồng mức xung quanh mạng lưới khớp trở kháng

Lý do cho việc này khá đơn giản: chúng ta muốn giảm lượng dung kháng và cảm kháng phụ trợ xung quanh các thành phần mạch khớp trở kháng. Điều này được biết đến rằng các thành phần phụ trợ thay đổi hiệu suất của các linh kiện thụ động thực tế trong mạch tần số cao, tạo ra giới hạn về tổn thất trở lại mong đợi tại mỗi cổng. Thật không may, bạn không bao giờ loại bỏ được dung kháng pad/trace trên các thành phần SMD, bạn chỉ có thể cố gắng giảm thiểu để mạch hoạt động càng gần với hiệu suất lý thuyết càng tốt.

Vì vậy, trong một số trường hợp, có thể có ý nghĩa khi thay đổi vị trí đặt mặt đất xung quanh các thành phần này. Chúng ta muốn đảm bảo rằng kích thước của các pad và trace trên các thành phần không tạo ra dung kháng phụ trợ bổ sung quá mức làm thay đổi trở kháng của các tụ điện và cuộn cảm trong mạng lưới khớp trở kháng.

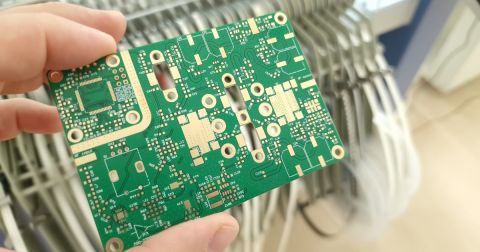

Mặt đất được làm sạch trong Bố cục PCB RF

Ví dụ dưới đây từ dự án nRF52 trước đây của chúng tôi cho thấy làm thế nào để làm sạch mặt đất; mạch phù hợp bộ lọc pi được hiển thị bên dưới. Lưu ý rằng điều này phù hợp với hướng dẫn từ bảng tham khảo nRF52 của Nordic. Tại đây, mặt đất đồng mặt phẳng được sử dụng trên L1, và có mặt đất đồng nhất phía dưới mạng lưới khớp trở kháng trên L6. Mặt đất chỉ được làm sạch phía dưới khu vực mạng lưới khớp và chỉ trên L2-L5.

Nếu chúng ta nhìn lên trên, các pad của linh kiện có một số điện dung trở lại với mặt đất; điều này thêm điện dung vào các tụ điện rời trong mạch khớp trở kháng. Ý tưởng tương tự áp dụng cho độ tự cảm liên quan đến mặt đất và độ tự cảm dẫn của các linh kiện. Làm thế nào chúng ta có thể làm sạch mặt đất mà không ảnh hưởng đến trở kháng dòng?

Đầu tiên, chúng ta có thể sử dụng mặt đất đồng mặt phẳng xung quanh các đường dẫn để thiết lập trở kháng đặc trưng của chúng phù hợp với trở kháng khớp mục tiêu của đầu ra chip. Một lỗ cắt đa giác được sử dụng phía dưới đường cấp chỉ trên các lớp nội bộ. Lớp dưới cùng có đổ đồng đồng nhất phía dưới mạch khớp trở kháng. Lớp trên cũng có đổ đồng, nhưng quy tắc khoảng cách tiêu chuẩn đã được thực thi xung quanh các đường dẫn và pad trên các mạng này để thiết lập trở kháng đặc trưng của các đường dẫn phù hợp với giá trị mục tiêu.

Bây giờ, hãy xem xét một ví dụ dựa trên sơ đồ bố trí RF được hiển thị ở trên.

Sự lệch lạc lớn như thế nào?

Để xác định sự lệch lạc, chúng ta có thể so sánh trường hợp lý thuyết với trường hợp thực tế. Ban đầu, chúng ta có một tụ điện 0402 và cuộn cảm 0603. Nếu chúng ta có mặt đất ngay dưới các pad này và các đường dẫn kết nối, sự nhiễu xạ trên tụ điện sẽ khoảng 3 pF/inch và 7.5 nH/inch trên lớp cách điện Dk = 4. Với cấu hình đồng mặt phẳng và mặt đất chỉ ở L6 được hiển thị ở trên, sự nhiễu xạ giảm xuống còn khoảng 2.75 pF/inch và 6.9 nH/inch. Chúng ta có thể thực hiện các tính toán tương tự cho các pad của cuộn cảm.

Tổng dung kháng và cảm kháng nhiễu xạ dựa trên các giá trị phần tử phân phối được tóm tắt ở dưới. Lưu ý rằng điều này chỉ tính đến các đường dẫn xung quanh các linh kiện và các pad; nó không tính đến cảm kháng tự của các chân gói.

|

|

|

|

|

|

|

|

|

|

|

|

Việc thay đổi vị trí mặt đất từ L2 sang L6 giảm dung kháng nhiễu xuống 22.4%. Với những giá trị này, giờ đây có thể bao gồm các dung kháng nhiễu này trong một mô phỏng và xác định ảnh hưởng của chúng đối với trở kháng đầu ra của mạng lưới.

Việc tính toán độ tự cảm hơi phức tạp hơn vì nó liên quan đến một số độ tự cảm vòng quanh các pad cũng như độ tự cảm của chân dẫn, cả hai có thể không dễ xác định. Độ tự cảm tự thân của dấu vết nối tiếp với cuộn cảm cũng đóng vai trò trong việc xác định tổng độ tự cảm. Nói chung, không an toàn khi chỉ giả định rằng độ tự cảm đã chỉnh sửa bù đắp cho dung kháng đã chỉnh sửa.

Lưu ý ở trên rằng tôi đã bao gồm một lựa chọn cho tất cả các linh kiện 0402 thay vì cuộn cảm 0603. Chúng ta có thể thấy rằng có sự giảm dung kháng từ các pad và dấu vết đơn giản vì cuộn cảm 0603 có pad lớn hơn so với cuộn cảm 0402. Ví dụ đã chỉnh sửa này được hiển thị bên dưới.

Chúng ta nhận được dung kháng nhiễu ít hơn một chút với sắp xếp này, nhưng không nhiều; chỉ giảm 6.8% so với kích thước gói hỗn hợp. Trong tất cả các trường hợp khác nhau này, quan trọng là phải xác định liệu điều này có ảnh hưởng trong hệ thống cụ thể của bạn hay không.

Liệu Sự Sai Lệch Này Có Quan Trọng?

Để xác định liệu dung kháng và cảm kháng nhiễu này có quan trọng hay không, chúng ta cần so sánh các giá trị này với giá trị của các linh kiện được đặt trên bố cục PCB.

Trong ví dụ nRF52 ở trên, giá trị tụ điện được sử dụng trong mạng ghép nối là 1.2 pF. Với dung kháng nhiễu thêm vào là 0.4388 pF, mạng lưới này hoạt động như thể nó có tổng dung kháng là 2.8388 pF. Kết quả là giảm khoảng 5 Ohms trở kháng so với trở kháng mục tiêu. Giả sử trong một khoảnh khắc mạch không có nhiễu hoàn hảo được ghép nối với 50 Ohms; nếu chúng ta sử dụng mạng ghép nối trở kháng thực này để biến đổi sang trở kháng mục tiêu 50 Ohms, lỗ hồi tỷ lệ thu được sẽ là S11 = -27.5 dB.

Vậy nếu tụ điện của chúng ta là 1.2 nF? Trong trường hợp này, dung kháng nhiễu thêm vào hầu như không đáng kể và sẽ không có ảnh hưởng gì trong bộ lọc pi của chúng ta. Nói chung, nếu dung kháng nhiễu thêm vào nhỏ hơn nhiều so với dung kháng rời, thì nó có thể được bỏ qua; ý tưởng tương tự cũng áp dụng cho cảm kháng.

Lưu ý rằng thiết kế này với cuộn cảm 0603 đã được thử nghiệm trên một bảng mạch của khách hàng và nó được phát hiện là hoạt động trong phạm vi thông số kỹ thuật, vì vậy tôi sẽ cảm thấy thoải mái khi sử dụng cùng một mạng lưới trong dự án này. Tuy nhiên, các điểm được nêu trên nên được xem xét nếu bạn muốn sử dụng thiết kế này trong các dự án của riêng bạn. Các khái niệm trên là khá quan trọng đối với các thành phần thực tế hoạt động trong phạm vi 1-6 GHz nơi mà mạng lưới khớp trở kháng là cần thiết.

Lý do mặt đất có thể được loại bỏ thường xuyên hơn trong các hệ thống hoạt động trong phạm vi 1-6 GHz là vì các tụ điện được sử dụng trong các mạng lưới khớp trở kháng này có thể khá nhỏ (~1 pF). ~1 pF của dung lượng tụ điện rời rạc trong mạng lưới tương tự như dung lượng tụ điện nhiễu dự kiến xung quanh một đường 50 Ohm trên laminate Dk ~ 4. Dung lượng tụ điện nhiễu này cơ bản tồn tại song song với dung lượng tụ điện rời rạc, và cùng nhau điều này có thể thay đổi điều kiện khớp nối.

Mạng lưới Khớp Nối ở Các Tần Số Cao Hơn như thế nào?

Ở các tần số cao hơn WiFi, bạn có thể không thấy bất kỳ mạng lưới khớp trở kháng nào trên các kết nối RF của mình được dự định hoạt động ở 50 Ohms. Có hai lý do quan trọng cho điều này:

- Hầu hết các IC RF sẽ tích hợp mạng lưới khớp trở kháng của chúng vào chíp

- . Các mạch RF hoặc ăng-ten thường được xây dựng cụ thể để hoạt động tại trở kháng mục tiêu.

Xem xét các bộ thu phát radar là một ví dụ. Có hàng triệu ô tô và cảm biến chuyên dụng sử dụng các bộ thu phát này, và trong tất cả các bảng mạch đó, bạn sẽ không thấy bất kỳ mạng lưới khớp trở kháng nào trên PCB. Trong các hệ thống này, chúng tôi quan tâm đến dung kháng nhiễu xung quanh PCB, và đặc biệt là trên các bộ khuếch đại RF công suất cao, nhưng chúng tôi không đặt mạng lưới khớp trở kháng với các linh kiện rời nhỏ trên PCB, và chắc chắn chúng tôi không loại bỏ lớp đất dưới các chân truyền và nhận.

Bây giờ xem xét ăng-ten vá dạng dãy hoạt động ở khoảng ~77-78 GHz được hiển thị bên dưới. Ăng-ten này được thiết kế cố ý để hoạt động ở 50 Ohm. Bình thường, một ăng-ten vá riêng lẻ (hoặc ăng-ten microstrip in đơn giản) có thể có trở kháng đầu vào là 200-300 Ohm. Lý do ăng-ten dưới đây có trở kháng đầu vào 50 Ohm là do kích thước nhỏ của nó và thông qua việc sử dụng đường dẫn khớp sóng phân số để kết nối các vá. Điều này cũng mang lại băng thông phát sóng rộng như được hiển thị trong biểu đồ tổn hao trở lại bên dưới.

Tôi đưa ra những ví dụ này để minh họa điểm quan trọng sau: đừng ngạc nhiên nếu bạn không thấy mạng ghép nối trở kháng được xây dựng từ các linh kiện rời khi hệ thống RF của bạn hoạt động ở tần số rất cao. Những linh kiện này thường bao gồm mặt đất phía dưới các chân TX và RX của chúng, cũng như một phương pháp phát tín hiệu phức tạp hơn được đặt xung quanh chân gắn trên PCB.

Bất cứ khi nào bạn cần thiết kế bố cục PCB RF với mạng ghép nối trở kháng, hãy chắc chắn bạn sử dụng bộ công cụ thiết kế và sản xuất PCB đầy đủ trong Altium Designer®. Khi bạn đã hoàn thành bố cục PCB và bạn sẵn sàng chia sẻ các tài liệu sản xuất, bạn có thể dễ dàng chia sẻ dữ liệu và phát hành tệp cho đội ngũ của mình với nền tảng Altium 365™.

Chúng tôi chỉ mới khám phá bề mặt của những gì có thể thực hiện với Altium Designer trên Altium 365. Bắt đầu dùng thử miễn phí Altium Designer + Altium 365 ngay hôm nay.