Die große Debatte über die richtigen PCB-Layout-Regeln geht weiter

Bis heute sehe ich immer noch viele PCB-Layout-Regeln, die fast 20 Jahre alt sind. Gelten diese Regeln auch weiterhin? Die Antwort ist ein klares „Vielleicht“. In vielen Forendiskussionen über PCB-Design-Regeln wird zunehmend mit „Immer/Nie“ argumentiert. Dadurch verwenden oder unterlassen manche Designer gängige Designregeln, wo dies nicht angebracht ist. Das mag nicht immer ein Versagen der Leiterplatte nach sich ziehen. Erfahrene Leiterplattenexperten sagen jedoch hierzu: manchmal funktioniert eine Leiterplatte auch einfach nur durch Zufall.

Bei der Diskussion um Faustregeln für das Leiterplattenlayout geht es nicht darum, ob diese Regeln richtig oder falsch sind. Das Problem besteht darin, dass bei der Diskussion über diese Regeln oftmals der Kontext überhaupt nicht berücksichtigt wird, was zu der bereits beschriebenen „Immer/Nie“-Diskussion in einigen beliebten Foren führt. Mein Ziel in diesem Artikel ist es, den Kontext hinter den allgemeinen Leiterplatten-Design-Regeln zu vermitteln. Ich hoffe, dass ich damit veranschaulichen kann, wann diese verschiedenen Regeln gelten und wann man sie vermeiden sollte.

Die gängigen PCB-Layout-Regeln

Lassen Sie uns nun direkt einsteigen, einen Blick auf einige gängige Regeln für das Leiterplattenlayout werfen und schauen, ob wir hilfreiche Kontextinformationen zu diesen Design-Regeln bieten können.

Orthogonales Routing

Diese Faustregel habe ich in einem kürzlich erschienenen Artikel detailliert besprochen. Hier möchte ich also nur die wichtigsten Punkte wiederholen. Beim orthogonalen Routing sollen Leiterbahnen auf benachbarten Signallagen in zueinander senkrecht stehenden Richtungen verlegt werden. So soll induktiver Crosstalk zwischen den Leiterbahnen auf diesen benachbarten Lagen vermieden werden. Bei hohen Frequenzen dominiert dann der kapazitive Crosstalk und erzeugt Stromspitzen zwischen orthogonalen Leiterbahnen.

Bei geringer Anstiegszeit und niedrigen Frequenzen (weniger als ein paar GHz) ist zwischen orthogonalen Leiterbahnen auf benachbarten Lagen kein signifikanter kapazitiver Crosstalk zu erwarten. Bei hohen Frequenzen in HF-Platinen (mehrere Dutzend GHz) erzeugen Hohlraumresonanzen im Fasergewebe und zwischen nicht geerdeten leitenden Strukturen starke elektromagnetische Resonanzen bei bestimmten Frequenzen. Diese können dann zu starkem Crosstalk zwischen den Signallagen führen, selbst wenn die Leiterbahnen in jeder Lage orthogonal verlegt sind.

Die bessere Option für alle Frequenzen besteht jedoch darin, die Signallagen einfach durch Kupferlagen zu trennen. Dies gilt insbesondere für moderne Leiterplatten, die allein aufgrund der in modernen ICs verwendeten Logikfamilien mit hohen Flankenraten/Frequenzen arbeiten. Wenn Sie vermuten, dass Sie ohne Probleme orthogonales Routing verwenden könnten, sollten Sie dennoch eine einfache Crosstalk-Simulation mit orthogonalen Leiterbahnen durchführen und prüfen, ob der Crosstalk über Ihrem Rauschgrenzwert liegt. Planen Sie auch den Rückpfad mit Sorgfalt, da dieser eines der Hauptprobleme bei beim orthogonalen Routing ist.

Thermische Vias

Hierbei handelt es sich um eine klassische „Immer/Nie“-Debatte. Manche Designer sagen, dass sie nie thermische Vias verwenden und noch nie Probleme beim Löten oder bei der Bestückung hatten. Gleichzeitig sagen andere Designer, dass thermische Vias immer und für jede Lagenverbindung verwendet werden sollten. Wer hat Recht?

Beide, jeweils in unterschiedlichen Situationen. Wenn man von Hand lötet, kann man einfach die Temperatur seines Lötkolbens erhöhen, um die Wärmeabgabe an die Kupferlage zu kompensieren. Ansonsten, wenn der Bestücker Wellenlöten verwendet, benötigt man thermische Vias, um zu verhindern, dass sich Komponenten verschieben oder dass kalte Lötstellen entstehen und Grabsteineffekte auftreten. Meiner Meinung nach ist es besser, in den sauren Apfel zu beißen und einfach in jeder Situation thermische Vias zu verwenden.

Rechtwinkliges Routing

Diese Faustregel wird wahrscheinlich von allen gehasst. Ich beobachte auch heute noch, dass manche Designer behaupten, rechtwinklige Leiterbahnen sollten unter keinen Umständen verwendet werden. Als Begründung werden unsinnige Behauptungen angeführt – beispielsweise, dass Elektronen an einer Leiterbahnecke nicht um 90 Grad „abbiegen“ können (90-Grad-Kurven an Vias werden hier dann einfach ignoriert). Die Gründe sind auch praktischer Natur. Zum Beispiel kann mit zwei 45-Grad-Kurven eine kürzere Leiterbahn geroutet werden als mit zwei 90-Grad-Kurven. Andere Erklärungen für diese Faustregel besagen, dass die Außenseite aller 90-Grad-Kurven abgeschrägt werden muss. Es gibt auch das Problem von Säurefallen – mit modernen alkalischen Ätzmittel ist das jedoch kein Thema mehr.

Sofern Sie nicht mit 50 GHz und mehr arbeiten (das geschieht im Moment nur im Millimeterwellen-/Radar-/5G-Bereich), müssen Sie sich keine Gedanken über rechtwinklige Leiterbahnen machen. Tatsächlich können Sie in jedem beliebigen Winkel routen und dabei die Widerstandskontrolle über die gesamte Verbindung hinweg aufrechterhalten. Dieser Prozess ist extrem einfach, wenn man seine Leiterplatten-Routingtools mit einem Solver für elektromagnetische Felder integriert.

Die „3W“-Regel(n)

Hiermit werden eigentlich drei verschiedene Regeln bezeichnet. Die erste Version der 3W-Regel besagt, dass der Abstand zwischen benachbarten Leiterbahnen mindestens das Dreifache der Breite (=„3 x Width“) der Leiterbahnen betragen sollte. Ziel ist die Minimierung des magnetischen Flusses zwischen den Leiterbahnen. Laut dieser Logik wird durch die Minimierung des magnetischen Flusses zwischen den Leiterbahnen auch der induktive Crosstalk minimiert.

Die verschiedenen Varianten dieser Regel, die ich gelesen habe, scheinen die Tatsache zu ignorieren, dass die Stärke des induktiven Crosstalks proportional zur Schleifeninduktivität zwischen „Aggressor“- und „Opfer“-Leiterbahn ist. Diese ist wiederum proportional zur Fläche, die von beiden Leiterbahnen umschlossen wird. Wenn die Schleifeninduktivität und die Fläche, die von jeder Leiterbahn umschlossen ist, kleiner werden, können die Leiterbahnen auch weniger als 3W voneinander entfernt liegen. Genau wie beim orthogonalen Routing sollten Sie eine grundlegende Crosstalk-Simulation durchführen und dabei die Abstände zwischen den Leiterbahnen variieren.

Die andere Variante der 3W-Regel kommt beim Sawtooth-Routing zur Längenanpassung zum Einsatz. Bei dieser Regel handelt es sich um eine Obergrenze für die Größe des Sawtooth-Querschnitts. Diese dient dazu, Widerstandsdiskontinuitäten in solchen Längenanpassungsstrukturen zu minimieren. Mehr über diese Version der 3W-Regel erfahren Sie in diesem aktuellen Artikel.

Die dritte Variante dieser Regel bezieht sich schließlich auf den Abstand zwischen Mikrostreifen und den angrenzenden Kupferflächen bzw. zwischen Streifenleitungen und den angrenzenden Kupferflächen. Diese Abstandsregel besagt, dass der Abstand zwischen der Leiterbahn und der Kupferfläche mindestens das Dreifache der Breite der Leiterbahn betragen sollte, um zu verhindern, dass die angrenzende Kupferfläche den Widerstand des Kupfers verändert.

Wie ich in einem kürzlich erschienenen Artikel erörtert und mit einigen einfachen Simulationen gezeigt habe, ist diese Regel übermäßig konservativ. Auch wenn die Einhaltung dieser Regel nicht notwendigerweise Ihrem Design schadet oder zu Signalintegritätsproblemen führt, können Sie in gewissem Maße gegen diese Regel verstoßen. Wie sehr gegen diese Regel verstoßen werden kann hängt von dem Verhältnis zwischen Leiterbahnbreite und Beabstandung der Lagendicke ab, sowie von der dielektrischen Konstante des Substrats. Schauen Sie sich den verlinkten Artikel an, um zu sehen, wie sich das berechnen lässt. Wenn Sie gerade nicht den Mindestabstand berechnen möchten, den Sie für Ihre Streifenleitungen oder Mikrostreifen verwenden können, können Sie auf Nummer sicher gehen und die 3W-Regel verwenden.

Die „20H“-Regel

Diese Regel legt den Abstand fest, den eine Massefläche unter einer Versorgungsfläche auf einer Leiterplatte haben sollte. Zunächst sollte in modernen Leiterplatten eine Versorgungsfläche neben der Massefläche platziert werden, um eine ausreichende Kapazität zwischen den Flächen zu gewährleisten und die Welligkeit des Strombus in Hochgeschwindigkeitsplatten zu reduzieren.

Einige experimentelle Studien zu diesem Thema haben zu durchwachsenen Ergebnissen geführt. Laut einer Studie können HF-Emissionen aus Streufeldern mit weniger als 300 MHz um ca. 5 dBμV/m reduziert werden, indem die 20H-Regel befolgt wird. Bei höheren Frequenzen, die den erzwungenen Resonanzen in der Wellenleiterstruktur für die Masse-/Versorgungsfläche entsprechen, sehen die Ergebnisse ganz anders aus. HF-Emissionen werden bei bestimmten Frequenzen unterdrückt und bei anderen erhöht, unabhängig davon, ob die 20H-Regel befolgt wird. Die Einhaltung der 20H-Regel bewirkt lediglich eine Änderung der Resonanzfrequenzen, die allesamt im GHz-Bereich liegen.

Hier das Fazit: Wenn Ihre Signalbandbreiten unter dem GHz-Bereich liegen, können Sie auch die 20H-Regel anwenden. Ansonsten scheint sie keine allgemeinen Vorteile zu bieten. Ob die 20H-Regel die HF-Emissionen von Streufeldern unterdrückt oder nicht, hängt von der Signalbandbreite ab.

Weiterführende Materialien zu PCB-Layoutregeln

Lesen Sie diese weiterführenden Artikel, um mehr über Leiterplatten-Designregeln zu erfahren:

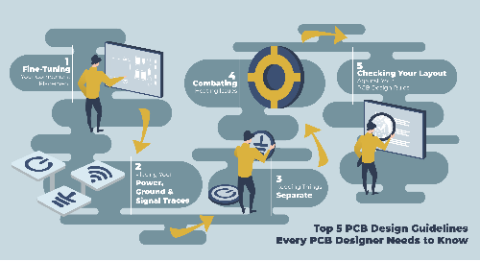

- Die wichtigsten Leiterplatten-Designrichtlinien, die jeder Designer kennen muss

- 7 häufige Missverständnisse im Leiterplattendesign

- Der schlechteste Rat zum Leiterplattendesign, den wir je gehört haben

Ganz gleich, welche Faustregeln oder Industriestandards für das Leiterplattenlayout im Rahmen Ihres Designs wichtig sind – Sie können sie als Designregeln in Altium Designer® definieren. Die vereinheitlichte Designumgebung in Altium Designer integriert Ihre Designdaten in die Routing- und Layout-Tools. Während Sie Ihr Layout erstellen, überprüfen Ihre Designtools die Leiterplatte anhand Ihrer Designregeln. Außerdem steht Ihnen ein komplettes Toolset für Signalintegritätssimulationen und für die Fertigungsvorbereitung Ihres neuen Produkts zur Verfügung.

Jetzt können Sie eine kostenlose Testversion von Altium Designer herunterladen und mehr über die branchenweit besten Werkzeuge für das Layout, die Simulation und die Produktionsplanung erfahren. Sprechen Sie noch heute mit einem Altium-Experten, um weitere Informationen zu erhalten.