How to Design a Bias Tee for a Power Amplifier

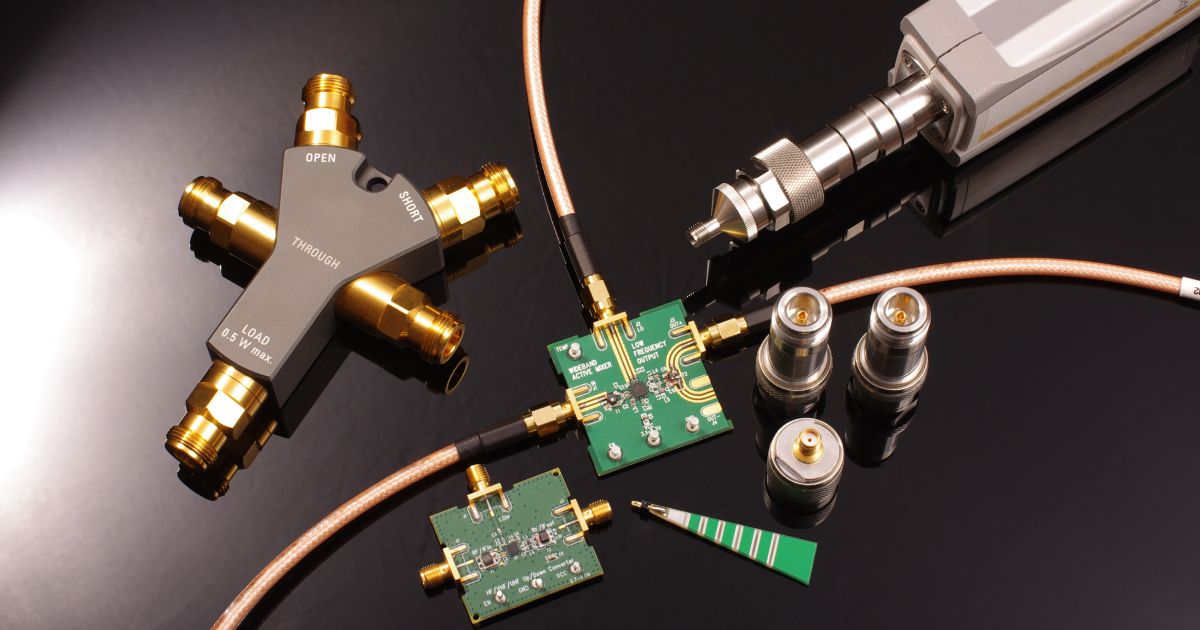

RF bias tees are used to separate DC and AC power along an interconnect. It is a 2-input, 1-output device that uses reactive elements to provide a power flow along different directions. In a previous project with an RF power amplifier layout, there is a bias tee in the design that is used to provide DC power to the amplifier while also allowing RF power to propagate towards the output SMA connector.

In this article, I’ll outline how to design this circuit and what the important parameters are for ensuring high-power propagation into your load component. These devices are available both as high-power modules for long-range broadcasting, but they can be built as small circuits on a PCB for lower-power RF systems.

What is a Bias Tee?

A bias tee is a simple circuit that uses an inductor and a capacitor to direct the flow of AC and DC power. The simplest type of bias tee is a 2-input device; an inductor is used to pass DC power from one input port, and a capacitor is used to pass AC power to the output. In the earlier example with our RF power amplifier, a bias tee was used to provide power to the amplifier, while also passing RF output power from the same pin. The circuit that was used previously is shown below.

The concept is simple; the inductive impedance of the inductor blocks the AC signal, while the capacitor blocks the DC signal from passing to the load in this system. The DC signal is simply the power being provided to the VDD pin, which will power the amplifier, and the internal circuitry of the amplifier will route the input power in the required manner.

Impedance Ratio in a Simple Bias Tee

Bias tees are designed such that we attempt to hit a particular impedance ratio. The impedance ratio in a bias tee refers to the ratio between the impedance along the DC path and the impedance seen by the signal as it travels along the output path. This impedance ratio needs to be included in the design of the bias tee under the following design targets:

The impedance looking into the DC port should be much larger than the impedance looking into the RF output

The equivalent impedance drop across the bias tee (measured from RFOUT to the output side of the capacitor) needs to match the transmission line LO_OUT

Therefore, we have two important definitions we can use to calculate the impedance ratio:

The values in the above two equations are reactances of the inductor (L) and capacitor (C) at the circuit’s operating frequency. A typical value for the impedance ratio could range anywhere from n = 1 to n = 1000. The bias tee’s impedance Z(tee) will be matched to the transmission line impedance, normally 50 Ohms on a PCB. We have two equations and two unknowns, so we can easily solve for these reactances.

The above values are minimum values required to converge to an impedance match. If we use the definition of capacitive and inductive reactance in the above equation, we have the following relationship between the target operating frequency and the capacitance:

This relationship tells us that we can shift the passband for the bias tee by adjusting C for a target impedance ratio while holding the inductor value L constant. We can also use the same relation but with L on the RHS of the equation instead of C.

For example, if we were to take the above values and increase the capacitance by a factor N, the operating frequency where we would expect to see maximum power delivery into the load would have to decrease by a factor √N in order to maintain the same impedance ratio. This could modify the impedance match at the output; even though we might have some reflection and impedance mismatch, the bias tee is shifting its passband such that the load power can be increased.

LC Bias Tee Calculator

You can use the calculator application below to determine the L and C values for use in a bias tee. This requires that the designer input a desired impedance ratio and a target impedance. The frequency given here is the expected frequency where we see the maximum in the bias tee’s passband.

Higher Order Filtering

What would happen if we placed a more complex filter section on the DC side? This is also possible with placement of a filter circuit. The DC stage shown above could have a more complex filter stage between the input power port and the branch point on the RF output net. For example, we could place a higher-order bidirectional low-pass filter between the input DC port and the branch point.

This would look something like the circuit below. Here I’ve placed parallel RL circuits as filtering elements that essentially limit current at higher frequencies coming from the power supply. If you look around the internet, you will see other examples of RLC circuits used as low-pass filters along the DC connection.

In this circuit, the impedance of the inductor + RF filter stage is sized to hit a particular impedance ratio with respect to the 50 Ohm line and the impedance ratio target. It’s also common to see a capacitor coming off of the VDD terminal. Why would we want to take this approach for the filter stage? There are three possible reasons:

- Because it is a higher-order filter, there will be steeper roll-off at high frequencies

- Based on the previous point, the filter section could filter noise from the DC source

- The tee could have a consistently high impedance ratio over a wider passband

In the above example, a higher-order filter is being used on the DC input port. The main challenge with this is that the topology of the blocking filter could have some passband ripple as a function of frequency, and as a result the tee impedance might also have some passband ripple. Therefore, it is important to simulate the filter section’s operation, which can be done in a SPICE simulation.

Example: SPICE Simulation With LC Bias Tee

In this section, I’ll show some simulation results for the simpler LC bias tee shown in the above schematics for our power amplifier module project. As it was originally designed, the bias tee shown above will operate as intended with wideband operation, and the impedance matching will be almost exactly 50 Ohms. However, it is not optimized for power delivery to a 50 Ohm load because of the filtering action of the bias tee due to the high impedance ratio.

The schematic below shows the initial circuit that will be used to simulate the bias tee.

For this simulation, we’ll look at an AC simulation for the tee, where we are interested in the output voltage, current into the RF side, and the power delivered to RLOAD. We also want to know what is the impedance looking across the RF input. Ideally, this should be as close to 50 Ohms as possible. The initial AC results are shown below.

This initial simulation reveals some pretty good results. The passband is very wide for this bias tee, and the impedance matching appears extremely precise right up to the circuit’s operating frequency of 6.3 GHz. Although the target impedance appears to have been reached, we do not see maximum power delivery to the load at the desired frequency. This is because 6.3 GHz is in the rolloff for the passband.

Suppose now we set the impedance ratio to 1:1 for this circuit. This would require a 1.2 nH inductor and 0.5 pF capacitor. The results with this updated simulation configuration are shown below.

From here we see that the passband has moved to higher frequencies, but we do not necessarily get more power out of the tee being delivered to RLOAD. We also see that the impedance does not converge to the target until a much higher frequency (about 10 GHz). So we still have not converged on a perfect design.

Finally, let’s see what happens if we increase the parameters to L = 6 nH and C = 1 pF (equal to 3.14 impedance ratio at about 6.45 GHz). In this case, we get much better matching to the target impedance, although the power delivered to the load is somewhat lower. Although the passband has moved much higher, the impedance this circuit is targeting at 6.45 GHz is about 77.4 Ohms, could explain the lower power delivery in this circuit.

A parameter sweep could help determine the best balance between L and C within some range. The other simulation we could perform is a transient analysis simulation. This will tell us what happens to the tee as the circuit is initially brought up to its operating power. Try doing this yourself as it is quite simple, and it should illustrate the potential pitfalls of using higher order filtering on the DC side of the circuit.

Is there anything wrong with this picture? As it turns out, there is! In particular, there are two points that are not considered in this simulation:

- At the GHz frequencies where this system will operate, the capacitor and inductor could have some parasitics (ESR/ESL on the capacitor and EPC on the inductor)

- The bias tee is supporting wave propagation, so the connections between components are actually transmission lines.

Based on point #2, and the idea that the output from an amplifier could be internally terminated to 50 Ohms, the bias tee’s impedance is sometimes set very low. This might be okay as long as the tee is placed very close to the output pin on the power amplifier. However, it is much more preferable to use impedance matching throughout the interconnect to try and maximize power transfer into the load.

SPICE simulations are not very good at simulating propagation on transmission lines between components and out of the bias tee. Therefore, the SPICE simulation shown above uses a 50 Ohm load to represent the input impedance looking into the load in our example power amplifier module. If we had a situation where the load is placed close to the output of the bias tee, then we can certainly take the circuit approach that is being idealized in the SPICE simulation example shown here.

Once you select components for your bias tee, make sure you use the complete set of PCB design tools in Altium to design your circuit board. Altium is the industry’s leading CAD platform that also includes an easy-to-use SPICE simulator inside the schematic editor. When you’ve finished your design, and you want to release files to your manufacturer, Altium makes it easy to collaborate and share your projects.