Overview of Electrical Stress Test Methods for PCBAs

Quality control in volume production and prototyping have one important set of tasks in common: the need for PCB testing. The specific set of tests you’ll need to perform in your PCBA depends on its application area, idealized service conditions, and of course the relevant industry standards on your product. Some basic tests and inspection tasks can be requested for your PCB/PCBA during fabrication and assembly, and it is a good idea to perform these tests at least to ensure continuity, accurate assembly, and simply to spot any obvious defects that might require rework.

High-reliability applications may require more than simple electrical testing and inspection, either during fabrication/assembly, once prototypes get into the hands of a design team, and/or by an external testing lab. An electrical stress analysis is just one of the possible tests that should be performed in high-reliability assemblies to ensure the PCBA can withstand demanding electrical conditions.

Electrical Stress Test Basics

To start, whenever something like electrical stress analysis gets brought up, new designers might think they’ve forgotten something or have to plan to do some extreme testing before they accept a board as provided by their manufacturer. You’ll be doing plenty of functional testing, but you won’t need to worry about specifically quantifying stress limits in your board unless you’re under some scrutiny from a standards organization (such as UL), regulatory requirements arise for your product, or you’re making the transition to high volume.

If you’re prototyping, or you’re only producing a small quantity of throwaway boards, then don’t overthink this. Hobby projects, simple prototypes, demo board projects, or one-offs are not normally candidates for electrical stress analysis. There are some QTY 1 exceptions, such as highly specialized aerospace products (satellites, drones, etc.). If your board won’t be deployed in an area or conditions where there is a risk of extreme electrical stress, then you probably don’t need electrical stress analysis.

With that out of the way, what is the current state of the art in electrical stress analysis, and what exactly is being “stressed”? Some of the main stress testing methods might fall into these areas:

- Electrical overstress tests

- Electrostatic discharge (ESD) tests

- Environmental stress screening

- Accelerated life tests

The idea is to identify problems that would create an unintended failure in the board or to simply quantify when the board specifically does fail (or both). While there are other quality control tests that might be performed during manufacturing, we’ll focus on the above list for the moment.

Electrical Overstress (EOS) Tests

This is sometimes lumped in with ESD as they are both forms of overstress on components. An EOS test is probably the simplest electrical stress test that can be performed: components are basically overpowered, and the DUT is monitored until the device fails. This is normally performed at the wafer level or individual device level simply to quantify when the device will fail, as well as its failure mechanism.

If you’re looking at the absolute maximum ratings in a datasheet, you’re seeing recommendations based on results from EOS tests for individual components. These ratings are defined with some margin of safety, so you might be able to exceed these values. What you’re not looking at is electrical overstress at the system level. This is where you’ll need to manually apply overstress to your system at each interface and power, and you’ll want to monitor performance or outputs to ensure the device can withstand any expected overstress.

Electrostatic Discharge (ESD) Tests

This test is exactly as it sounds: it tests the extent to which the PCBA can withstand ESD events. When an ESD event occurs, your PCBA will interact with a very strong electrical pulse, possibly reaching over 10,000 V and exceeding several amperes of current. Such an event can destroy components if it is not diverted back to a safety ground in your system. ESD circuits are designed to absorb and/or divert ESD pulses away from components and into the safety ground region in your system. Some digital interfaces, such as IEEE 802.3 standards on Ethernet PHYs, have their own ESD requirements that must be met at the component level.

JEDEC differentiates between ESD at the component level and at the system level. PCB designers need to consider what happens at the system level because this is the area that they can control.

A system-level ESD event occurs within the PCBA and may affect multiple components, leading to one of the following outcomes:

- The system continues to work without a problem

- The system experiences upset/lockup (soft failure), but no physical failure.

- The system experiences physical damage (hard failure)

Various industry standards beyond the IPC standards place requirements on the ability of a device to withstand electrostatic discharge. The specific test method depends on which standards will govern your product (such as IEC 62368-1/IEC 61000, ISO 10605 for automotive, DO-160 for avionics, etc.). Refer to the relevant safety standards for your product and industry to determine the level of ESD protection your product will require.

Environmental Stress Screening (ESS) Tests

These tests are meant to closely simulate the idealized deployment environment for a device. ESS testing could involve applying thermal cycling, drop tests, vibration tests, thermal/mechanical shock tests, and any other environmental or mechanical exposure a device will be expected to receive during operation. More specialized testing methods might involve crash tests, pressure and humidity tests, and even altitude tests. Highly reliable systems will need to stand up to all of these environmental factors during electrical operation, so a combination of tests is generally needed to ensure reliability.

Functional testing is also performed before, during, and after these tests to fully qualify whether the design will fail and whether functionality is compromised. These tests don’t just look at the electrical stresses, they also qualify functionality in a variety of stressful situations that might be inclusive of electrical overstress or even ESD. Since this is typically a combination of specialized tests that need to be performed, rigorous evaluation is performed by the design team, and not a manufacturer.

Accelerated Life Tests

This refers to a set of possible tests that are meant to determine the approximate useful lifetime of a new device. Accelerated life tests are often lumped together as “burn-in testing”, although there are several variations of these tests. Accelerated life tests can be divided into the following areas:

- Burn-in testing: A method for identifying which components and/or assemblies will fail early using statistical techniques.

- Highly accelerated life testing (HALT): Here the goal is to stress a device until it fails in gross overoperation. This mimics overoperation in the actual environmental conditions where the device will be deployed.

- Highly accelerated stress testing (HAST): Similar to HALT in that the design is stressed until total failure.

- Highly accelerated stress screening (HASS): Uses the same environmental stresses as in HASS, but at lower levels, and typically after a complete HALT test is completed.

Any of these lifetime/stress tests could be performed along the other test methods mentioned above as long as the right testing chambers and equipment are available. Such combinations of tests can be highly specialized, but they are essential to determining lifetime and identifying failure mechanisms in electronics.

Failure Analysis

The above electrical stress tests are intended to both identify the limits of a device, while also evaluating whether it can withstand environmental conditions during operation. If you find that the design can’t stand up to the expected level of stress and fails, some failure analysis is required to determine the root cause of the failure in your device. Failure could occur at the component level, board level, or both, and some forensic investigation is needed to determine the failure mechanism with certainty. We’ll look at these points in some upcoming articles.

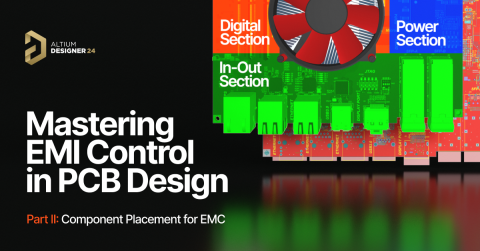

When you need to specify your electrical stress test requirements, inspection requirements, and even mechanical performance requirements, use the complete set of design and documentation features in Altium Designer®. The integrated manufacturing tools and the Draftsman utility can help you specify your performance requirements for your product. When you’ve finished your design, and you want to release files to your manufacturer, the Altium 365™ platform makes it easy to collaborate and share your projects.

We have only scratched the surface of what’s possible with Altium Designer on Altium 365. Start your free trial of Altium Designer + Altium 365 today.