Análise, Redução e Técnicas de Eliminação de Crosstalk em Design de PCB

Seja projetando uma placa digital com muitos traços, ou uma placa RF operando em frequências muito altas, qualquer dispositivo eletrônico com sinais se propagando experimentará crosstalk. É simplesmente uma questão de se o crosstalk é tão extremo que o sistema falha em funcionar, ou se o crosstalk está dentro de algum limite aceitável. Não existe um nível universal de crosstalk "aceitável", mas se você descobrir por meio de simulação e medição que tem um problema, existem métodos muito simples que podem ser usados para reduzir o crosstalk.

Neste artigo, queremos olhar para algumas maneiras certeiras de você reduzir o crosstalk em seus designs de alta velocidade. Vou delinear três métodos que são simples e que sempre produzem resultados favoráveis. Há um outro método que pode proporcionar melhorias, mas requer alguma análise ou simulação adicional para garantir que você não crie um novo problema de integridade de sinal.

O Que É Crosstalk em Design de PCB?

Definido de forma muito simples, crosstalk é um fenômeno onde um interconector transportando um sinal (o agressor) irá acoplar indutiva ou capacitivamente esse sinal em um interconector vizinho (a vítima). Isso é bidirecional: a vítima e o agressor podem ser trocados, e, com tudo o mais sendo igual, esperaria-se que o crosstalk ocorresse em ambas as direções. Crosstalk só ocorre enquanto um sinal está mudando, ou seja, durante a taxa de borda de um sinal digital; para sinais analógicos/RF, uma réplica deslocada de fase pode ocorrer em interconectores vizinhos porque o sinal no agressor está sempre mudando. Sinais puramente DC não causam crosstalk, mas podem ser vítimas de crosstalk.

Um gráfico simples ilustrando o crosstalk e as equações que determinam a força de um sinal de crosstalk em um interconector vítima são mostrados abaixo. Crosstalk, como mostrado aqui, é subdividido em dois tipos:

-

Crosstalk de extremidade próxima (NEXT, curva vermelha), às vezes chamado de crosstalk de fundo

-

Crosstalk de extremidade distante (FEXT, curva verde), às vezes chamado de crosstalk direto

Ambos os tipos de diafonia são mediados pela indutância mútua (Lm) e capacitância mútua (Cm) entre os dois traços. Juntos, esses dois efeitos determinam a diafonia observada no lado do transmissor e no lado do receptor de uma linha vítima.

Se você se interessa pela matemática que rege a diafonia, notará que o FEXT poderia ser eliminado em casos ideais, o que é indicado pelo sinal negativo na equação do FEXT. Uma stripline ideal, perfeitamente simétrica, teria FEXT zero, embora na realidade a diafonia nunca seja zero.

Agora que cobrimos essa introdução básica, vamos olhar para as técnicas mais simples de redução de diafonia.

Técnicas de Redução de Diafonia que Você Pode Usar no Altium Designer

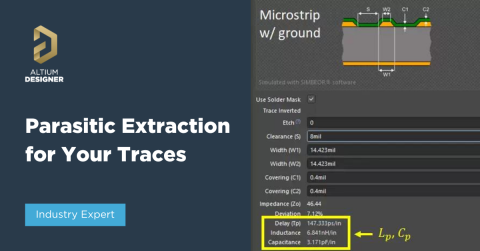

Se você está projetando uma PCB que usa sinais digitais, e esses sinais têm uma taxa de transição rápida o suficiente para criar diafonia perceptível, então você deve sempre rotear esses sinais sobre um plano de terra. Isso significa, no mínimo, você deve usar uma configuração SIG+PWR/GND/GND/SIG+PWR para designs digitais, particularmente quando o tempo de subida do sinal reduz para a faixa de ns ou menor.

O roteamento sobre um plano de terra neste tipo de empilhamento fornece uma impedância definida que pode ser ajustada para 50 Ohms conforme necessário, de modo a suportar interfaces simples e diferenciais padronizadas com requisitos de impedância especificados. Isso definirá a largura do traço para um valor específico, que pode então ser usado para definir um valor de espaçamento entre os traços.

Aumento do Espaçamento Entre Traços para Redução de Diafonia

A maneira mais simples e eficaz de reduzir a intensidade da diafonia recebida em um traço vítima é aumentar o espaçamento entre os traços. Quando os traços estão mais próximos, os campos elétricos e magnéticos ao redor do traço agressor serão mais fortes, assim, qualquer diafonia no traço vítima será mais intensa. Portanto, aumentar o espaçamento certamente criará uma redução da diafonia entre as linhas.

Existe uma regra básica de design de PCB conhecida como a regra "3W", que afirma que:

-

O espaçamento entre dois traços deve ser pelo menos 3x a largura dos traços.

A intenção por trás desta regra é fornecer um valor muito conservador que geralmente proporciona a redução de diafonia dentro dos limites de margem de ruído que se aplicam à maioria das famílias lógicas. Esta regra é apropriada para trilhas de alta velocidade acima de um plano de terra, mas com uma camada dielétrica mais espessa que era anteriormente usada em construções tradicionais antes do advento do HDI. Vou explicar mais sobre por que isso é importante abaixo.

Para implementar isso no Altium Designer, você pode fazer o seguinte:

-

Criar uma Classe de Rede contendo as redes de alta velocidade que poderiam ser agressores de diafonia.

-

Aplicar uma regra de largura às trilhas na sua Classe de Rede que define a largura desejada. Se essas trilhas forem controladas por impedância, aplique o perfil de impedância do gerenciador de pilhas de camadas.

-

Definir uma regra de espaçamento entre trilhas na seção de Liberação do Editor de Regras e Restrições de PCB. Aplique o espaçamento maior apenas à sua Classe de Rede.

Isso garantirá que suas regras de espaçamento sejam definidas especificamente para as trilhas de alta velocidade que você deseja separar sem impor a mesma regra a todas as outras trilhas.

E quanto ao espaçamento entre pares diferenciais? Esta é uma área onde usar acoplamento apertado é benéfico, pois garante que o crosstalk em um par diferencial seja maximamente recebido como ruído de modo comum. No entanto, como discuto abaixo, há mais benefícios no acoplamento frouxo em comparação com o acoplamento apertado, e pode haver estratégias melhores quando pares diferenciais estão envolvidos.

Minimize Comprimentos de Traços Paralelos Para Reduzir Crosstalk

O crosstalk entre dois traços é ponderado pelo produto escalar de vetores ortogonais entre os dois traços acoplados. Em termos não matemáticos, isso significa que o crosstalk entre dois traços é maximizado quando os dois traços estão correndo paralelamente um ao outro. Portanto, uma estratégia simples para reduzir o crosstalk é minimizar o comprimento sobre o qual dois traços são paralelos um ao outro.

Se você esculpiu canais de roteamento em direções únicas, então isso é mais fácil de dizer do que fazer. No entanto, esta é a base para o roteamento ortogonal sem um plano de terra, onde traços em duas camadas diferentes correm perpendicularmente um ao outro. Isso funciona até você chegar a taxas de borda muito rápidas; leia mais sobre roteamento ortogonal neste artigo.

Se você deseja impor essa prática em suas ferramentas de roteamento, pode usar a regra ParallelSegment no Editor de Regras e Restrições do PCB, conforme mostrado abaixo. Note que a regra ParallelSegment também aplica uma distância mínima de separação, assim como você faria com a regra de Clearance mostrada acima.

Use uma Distância Menor até o Terra para Redução de Crosstalk

A regra de 3W mencionada acima é um ponto de referência apropriado para trilhas roteadas em camadas dielétricas mais espessas. No entanto, existe um método alternativo que pode ser usado para redução de crosstalk: aproximar o terra das trilhas. Se você está roteando em camadas mais finas, também é possível ir além da regra de 3W, e ainda assim observar a mesma magnitude de crosstalk que você veria em camadas mais espessas ao rotear com a regra de 3W.

Como exemplo, veja os resultados da simulação abaixo. Estas curvas mostram resultados de diafonia usando parâmetros S de 4 portas para linhas de transmissão em um empilhamento construído com laminados Megtron 7. O gráfico superior mostra o que acontece em uma situação típica de linhas finas em uma camada de 4 mil, onde o espaçamento e a largura de linha entre nossas linhas de transmissão são iguais. Se simplesmente aproximarmos os planos de terra ao diminuir a espessura do dielétrico em 50%, e então redimensionarmos as trilhas para atingir o mesmo alvo de impedância, vemos que conseguimos uma redução significativa na diafonia nominal sem ter que fazer nenhum rerroteamento.

Neste exemplo, o redimensionamento das trilhas pode ser completado regenerando o perfil de impedância no Gerenciador de Empilhamento de Camadas no Altium Designer, seguido pela regeneração das regras de design para estas redes. O processo leva alguns minutos e não requer rerroteamento. Também poderíamos trocar por um constante dielétrica diferente para obter mais melhorias.

Se o seu projeto já estiver completo e você estiver se preparando para a fabricação, trocar uma camada dielétrica é uma mudança simples de materiais que pode ser implementada pelo seu fabricante. Se você ainda estiver no meio do seu projeto, pode alterar o empilhamento no arquivo de layout da sua PCB e, em seguida, mudar as larguras das trilhas para trilhas com controle de impedância; não seria necessário refazer o roteamento. Ambas as opções oferecem benefícios consideráveis para o crosstalk.

Deve-se Usar Preenchimento de Cobre e Trilhas de Guarda para Redução de Crosstalk?

Finalmente, um método que os projetistas podem tentar empregar com frequência é o uso de preenchimento de cobre entre duas trilhas, ou o roteamento de uma trilha de guarda entre suas duas trilhas de sinal. Eu não aconselho a depender disso como um método para reduzir o crosstalk, e muitos outros especialistas também não. Há várias razões para isso:

-

Para encaixar uma trilha de guarda ou preenchimento de cobre entre duas trilhas acopladas, você precisa espaçá-las, tipicamente por pelo menos 3W

-

Aproximar o terra das trilhas pode produzir a mesma redução de crosstalk que você poderia estar tentando alcançar ao rotear uma trilha de guarda

-

Não há uma maneira automatizada de rotear rapidamente uma trilha de guarda, você tem que roteá-la e posicionar seu terra manualmente com vias

-

O preenchimento com cobre é basicamente como um traço de proteção e pode ser colocado de forma automatizada, mas a costura de vias pode realmente aumentar o acoplamento indesejado criando uma cavidade ressonante aberta entre os dois traços acoplados; esta é a mesma razão pela qual você obtém uma perda de potência extrema em certas guias de onda coplanares como mostrado aqui.

-

Usar preenchimento com cobre com vias de costura requer algum cálculo ou simulação antes da implementação para acertar

O ponto #1 é o mais importante: para até mesmo fazer espaço para um preenchimento com cobre apreciável ou traços de proteção, você já precisa fornecer espaço suficiente para atingir pelo menos um espaçamento de 3W. Isso proporcionará proteção significativa contra o acoplamento indesejado, desde que haja um plano de terra presente na próxima camada.

Portanto, antes de usar o método de preenchimento com cobre e traços de proteção, considere os outros pontos acima primeiro, pois eles podem fornecer melhorias significativas que trazem suas interconexões para a conformidade. Para aprender mais sobre isso, assista ao seguinte vídeo.

No vídeo, eu mostro um conjunto de resultados de simulação de Eric Bogatin e Bert Simonovich, que revelam a eficácia das trilhas de guarda na redução de diafonia para trilhas de extremidade única. Como o uso de trilhas de guarda continua surgindo em situações com designs de alta velocidade, é útil examinar como as trilhas de guarda afetam a diafonia com trilhas de extremidade única de 50 Ohms, já que estas normalmente seriam implementadas como o padrão em barramentos de alta velocidade e interconexões RF (por exemplo, em SDRAM/DDR). Em outras instâncias com SPI ou PPI, não há especificação de impedância, mas trilhas muito longas poderiam ser projetadas para 50 Ohms e ter terminação aplicada.

O resultado importante que foi encontrado por Bogatin e Simonovich é que o nível de diafonia encontrado nas simulações dependia de se as trilhas eram roteadas como 50 Ohm striplines ou microstrip, bem como se as trilhas estão curtas, abertas ou conectadas à terminação de 50 Ohms em cada extremidade. Para conveniência, estou mostrando seus resultados no domínio do tempo abaixo, que mostram a eficácia relativa ou ineficácia das trilhas de guarda em ambas as configurações.

Bogatin, E., Simonovich, B., Guard Traces: Love Them or Leave Them? Signal Integrity Journal, 5 September 2019.

Os resultados são muito claros: a única configuração eficaz de trilha de guarda é em stripline com ambas as extremidades aterradas, especificamente para NEXT. Para FEXT, parece haver uma redução de diafonia para uma trilha de guarda aterrada em stripline, mas a diafonia já era muito baixa de qualquer forma.

Os resultados mostrados aqui são válidos para trilhas de 50 Ohm de extremidade única, mas os mesmos resultados podem ser observados para um par diferencial separado por trilhas de guarda. A diferença é que estaríamos olhando para a diafonia diferencial, onde um sinal diferencial pode criar tanto ruído diferencial quanto de modo comum no interconector vítima.

Para ler o estudo completo e aprender mais sobre este problema com trilhas de extremidade única, leia o seguinte artigo no Signal Integrity Journal:

Quando você está procurando pelo melhor pacote de software para design de PCB de alta velocidade, use o conjunto completo de ferramentas de design em Altium Designer. O motor integrado de regras de design e o Layer Stack Manager oferecem tudo o que você precisa para criar uma placa de circuito com baixo diafonia e impedância controlada. Quando você terminar seu design e quiser liberar os arquivos para seu fabricante, a plataforma Altium 365™ facilita a colaboração e o compartilhamento de seus projetos.

Apenas começamos a explorar o que é possível com Altium Designer no Altium 365. Comece seu teste gratuito do Altium Designer + Altium 365 hoje.