Projet Pi.MX8 - Agencement du circuit imprimé Partie 3

Chapitres

Board Layout Part 3

| Created: June 24, 2024PCB Assembly

| Coming soonBienvenue dans un nouvel épisode du projet de module informatique open-source Pi.MX8 ! Dans cette série, nous explorons la conception et les tests d'un système sur module basé sur un processeur i.MX8M plus de NXP.

Dans la mise à jour précédente, nous avons terminé les préparatifs de la mise en page. Cela incluait la création des profils d'impédance, l'ajout des règles de conception selon les spécifications du fabricant de la carte et la définition des zones où des règles de conception spéciales devraient s'appliquer. Nous avons également terminé le routage de l'interface LPDDR4 mais sans ajustement de longueur (pour l'instant).

Avant de commencer l'ajustement de longueur de l'interface DRAM, nous examinerons le routage des autres interfaces sur le module Pi.MX8. Il y a pas mal de bus à haute et basse vitesse sur la carte, certains étant des bus parallèles larges qui occupent beaucoup d'espace de routage. Afin d'allouer suffisamment d'espace à chaque interface, nous allons d'abord créer un plan d'implantation sommaire pour chaque couche de routage du module.

Planification du routage

Le plan de routage nous aidera à déterminer comment distribuer toutes les interfaces à haute et basse vitesse à travers les couches de signaux disponibles. En établissant un guide approximatif à l'avance, nous pouvons nous assurer que nous disposons de suffisamment d'espace de routage disponible sur la couche sur laquelle nous travaillons actuellement. Cela nous aide également à minimiser les transitions entre les couches et à réduire la quantité de retravail à effectuer pendant le processus de routage.

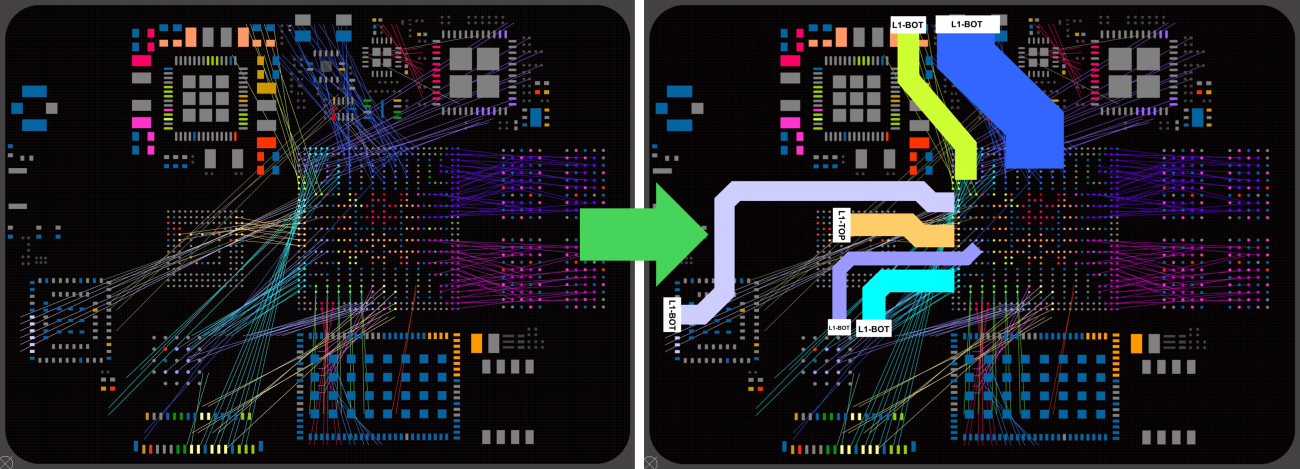

Il existe plusieurs façons de mettre en place la planification de l'agencement, principalement en fonction des outils disponibles. Nous avons juste besoin d'un outil de dessin basique qui nous permet de faire des esquisses par-dessus une image existante. Dans cet exemple, nous utiliserons Inkscape.

Dans Inkscape, nous pouvons ajouter une image de fond qui montre le placement des composants et les interfaces non routées sous forme de fils aériens colorés. Notez que les réseaux d'alimentation sont cachés dans cette capture d'écran car nous nous concentrerons uniquement sur les réseaux qui seront routés sur les couches de signal. Dans le schéma, nous avons placé une directive de classe de réseau sur chaque réseau d'alimentation, ce qui facilite l'identification des réseaux routés sur les couches de plan en activant ou en masquant simplement la classe de réseau associée dans l'éditeur de layout.

Pour le routage proprement dit, nous ajoutons simplement des lignes dans Inkscape pour représenter les interfaces que nous souhaitons router sur la couche correspondante. Nous pouvons ajuster la largeur de ces lignes pour représenter le nombre de signaux qui seront routés dans l'interface. La couleur de la ligne peut être choisie parmi l'image de fond pour faciliter l'identification de l'interface représentée.

Comme les transitions entre les couches nécessitent également de l'espace alloué sur toutes les couches, nous pouvons ajouter un bloc à la fin de chaque ligne détaillant la transition de couche.

Planification de l'agencement dans Inkscape avec une capture d'écran d'Altium Designer comme image de fond

Une fois que nous avons répété le processus ci-dessus pour chaque couche de routage, nous pouvons aller de l'avant et commencer le processus de routage proprement dit.

Routage de la couche supérieure

Avec une stratégie de routage en place, commençons par router les interfaces sur la couche supérieure. Puisque nous avons déjà réalisé le routage de fanout pour les composants sur la couche supérieure, nous pouvons utiliser tout l'espace restant pour le routage des signaux. Il ne reste pas beaucoup d'espace, mais ce que nous avons peut encore être utilisé pour faciliter le routage sur les couches de signaux internes en plaçant stratégiquement des VIAs dans des régions qui n'interféreront pas avec le routage sur les couches internes plus tard. C'est un autre avantage de planifier une mise en page à l'avance, sinon ces régions ne seraient pas définies à ce stade.

Routage de la couche supérieure du module PiMX8

Lors du placement des pistes sur la couche supérieure, nous devrions également considérer que nous avons besoin d'un peu d'espace pour ajouter des fonctionnalités telles que des fiduciaux ou des étiquettes sur la couche supérieure. Les codes à matrice de données gravés au laser peuvent également nécessiter soit une zone de cuivre solide, soit une zone sans pistes pour fournir un contraste homogène, ce qui signifie que ces zones ne peuvent pas être utilisées pour le routage.

Routage de la couche de signaux internes

La plupart des connexions seront placées sur les deux couches de signal internes que nous avons définies dans le gestionnaire de pile de couches. Commençons par router toutes les interfaces synchrones à haute vitesse. Dans notre cas, il pourrait s'agir des interfaces MIPI-CSI, MIPI-DSI et LVDS. Ces interfaces utilisent toutes une signalisation différentielle basse tension et comportent une ligne d'horloge dédiée et au moins deux lignes de données. Elles nécessitent beaucoup d'espace de routage car la longueur de chaque ligne de données doit être ajustée à celle de la ligne d'horloge dans une certaine marge de temps. L'ajustement de la longueur de plusieurs paires différentielles peut nécessiter beaucoup d'espace, car il est très probable qu'une ou plusieurs paires au sein de l'interface introduiront un retard significatif qui doit être pris en compte. En routant ces interfaces en premier, nous pouvons nous assurer qu'assez d'espace sera disponible pour l'ajustement de longueur plus tard.

Placer des VIAS de chemin de retour près des transitions de couche de ces paires différentielles à haute vitesse est également important pour assurer l'intégrité du signal. Les VIAS de chemin de retour peuvent occuper de l'espace sur plusieurs couches, donc ces VIAS devraient être placés dès qu'une transition de signal est réalisée.

Ensuite, nous pouvons router les autres interfaces à haute vitesse telles que PCIe, USB, HDMI et Ethernet. Ces interfaces ont des exigences moins strictes en matière d'appariement de longueur entre les paires, donc nous n'avons pas besoin de consacrer autant d'espace à l'appariement de longueur. Une gestion solide du chemin de retour et des approches de base en conception haute vitesse sur ces signaux sont néanmoins très importantes, bien que les plaçant en second sur la liste des priorités de routage.

En dernier lieu, mais non des moindres, nous pouvons router les interfaces de vitesse inférieure restantes telles que SDIO, GPIO, RGMII et d'autres bus divers tels que UART ou I2C et SPI. Ces interfaces fonctionnent toujours à des vitesses de transition élevées, ce qui signifie que nous devons toujours les traiter comme des signaux à haute vitesse.

Routing de la couche de signal interne 1

Routing de la couche de signal interne 2

Routing de la couche inférieure

Dans le cas de la carte PiMX8, nous pouvons traiter la couche inférieure comme une couche de routage interne en termes d'espace disponible. La plupart des composants actifs sont placés sur la couche supérieure du module, ne laissant qu'un petit nombre de régulateurs de tension et de composants passifs tels que les condensateurs de découplage et les résistances de configuration sur la couche inférieure.

La priorité de routage sur la couche inférieure est la même que pour les couches internes, donc nous commencerons par les interfaces MIPI-CSI, MIPI-DSI et LVDS. Sur le module PiMX8, un multiplexeur haute vitesse peut sélectionner entre les ports DSI et LVDS. Ce composant est placé sur la couche inférieure près du connecteur carte-à-carte. En raison du brochage du multiplexeur, il y a un retard significatif sur l'une des lignes de signal connectées au mux. Nous devrons examiner cela de plus près lors du processus d'appariement des longueurs, mais nous devons réserver de l'espace sur la couche inférieure pour permettre un retard plus important.

Brochage du multiplexeur avec une ligne longue dans l'interface

Routage de la couche inférieure module PiMX8

Il y a quelques scénarios sur le module PiMX8 qui nécessitent une attention particulière lors de l'ajustement des retards. Nous ferons un usage intensif des X-signaux pour surmonter certains de ces défis. Ce que sont exactement ces défis, et comment nous pouvons implémenter les X-signaux pour fournir un ajustement précis des retards sur un composant partagé par plusieurs interfaces, feront partie de la prochaine mise à jour. Restez à l'écoute !