Projeto Pi.MX8 - Layout da Placa Parte 3

Capítulos

Board Layout Part 3

| Created: June 24, 2024PCB Assembly

| Coming soonBem-vindo a uma nova edição do projeto do módulo de computador de código aberto Pi.MX8! Nesta série, exploramos o design e os testes de um sistema em módulo baseado no processador i.MX8M Plus da NXP.

Na atualização anterior, completamos os preparativos do layout. Isso incluiu a criação dos perfis de impedância, a adição das regras de design de acordo com as especificações do fabricante da placa e a definição de áreas onde regras de design especiais deveriam ser aplicadas. Também terminamos o roteamento da interface LPDDR4, mas sem ajuste de comprimento (por enquanto).

Antes de começarmos com o ajuste de comprimento da interface DRAM, vamos dar uma olhada no roteamento das demais interfaces no módulo Pi.MX8. Há várias barras de alta e baixa velocidade na placa, algumas das quais são barras paralelas largas que ocupam muito espaço de roteamento. Para alocar espaço suficiente para cada interface, primeiro criaremos um plano básico para cada camada de roteamento no módulo.

Planejamento de roteamento

O plano de roteamento nos ajudará a determinar como distribuir todas as interfaces de alta e baixa velocidade pelas camadas de sinal disponíveis. Ao configurar um guia preliminar com antecedência, podemos garantir que temos espaço suficiente de roteamento disponível na camada em que estamos trabalhando atualmente. Isso também nos ajuda a minimizar as transições entre camadas e reduzir a quantidade de retrabalho a ser feito durante o processo de roteamento.

Existem várias maneiras de configurar o planejamento de layout, principalmente dependendo das ferramentas disponíveis. Precisamos apenas de uma ferramenta de desenho básica que nos permita esboçar sobre uma imagem existente. Neste exemplo, usaremos o Inkscape.

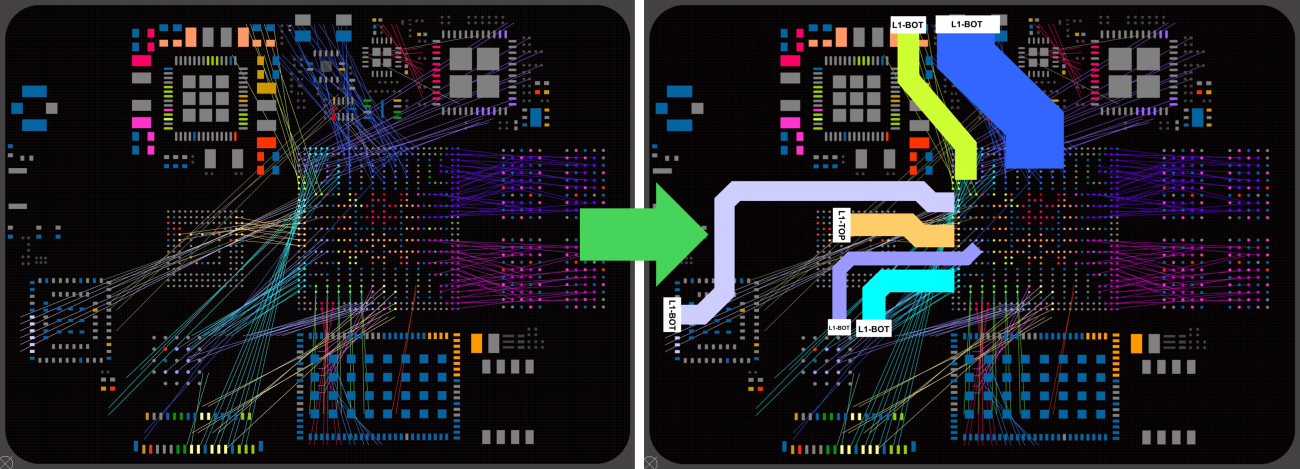

No Inkscape, podemos adicionar uma imagem de fundo que mostra a colocação dos componentes e as interfaces não roteadas na forma de airwires coloridos. Note que as redes de alimentação estão ocultas nesta captura de tela, pois nos concentraremos apenas nas redes que serão roteadas nas camadas de sinal. No esquemático, colocamos uma diretiva de classe de rede em cada rede de alimentação, facilitando a identificação de quais redes são roteadas nas camadas de plano simplesmente ativando ou ocultando a classe de rede associada no editor de layout.

Para o roteamento propriamente dito, simplesmente adicionamos linhas no Inkscape para representar as interfaces que queremos rotear na camada correspondente. Podemos ajustar a largura dessas linhas para representar quantos sinais serão roteados na interface. A cor da linha pode ser escolhida a partir da imagem de fundo para facilitar a identificação de qual interface está sendo representada.

Uma vez que as transições de camada também precisam de espaço alocado em todas as camadas, podemos adicionar um bloco no final de cada linha detalhando a transição de camada.

Planejamento de layout no Inkscape com uma captura de tela do Altium Designer como imagem de fundo

Uma vez que tenhamos repetido o processo acima para cada camada de roteamento, podemos prosseguir e começar com o processo de roteamento propriamente dito.

Roteamento da camada superior

Com uma estratégia de roteamento em vigor, vamos começar roteando as interfaces na camada superior. Uma vez que já realizamos o roteamento de fanout para os componentes na camada superior, podemos usar todo o espaço restante para o roteamento de sinal. Não há muito espaço sobrando, mas o que temos ainda pode ser utilizado para facilitar o roteamento nas camadas internas de sinal, colocando VIAs estrategicamente em regiões que não interferirão com o roteamento nas camadas internas mais tarde. Esse é outro benefício de planejar um layout com antecedência, caso contrário, essas regiões não estariam definidas nesta fase.

Roteamento da camada superior do módulo PiMX8

Ao colocar trilhas na camada superior, também devemos considerar que precisamos de algum espaço para adicionar recursos como fiduciais ou etiquetas na camada superior. Códigos de matriz de dados gravados a laser também podem exigir ou uma área de cobre sólido ou uma área sem trilhas para fornecer um contraste homogêneo, o que significa que essas áreas não podem ser utilizadas para roteamento.

Roteamento da Camada Interna de Sinal

A maioria das conexões será colocada nas duas camadas internas de sinal que definimos no gerenciador de pilhas de camadas. Vamos começar roteando todas as interfaces síncronas de alta velocidade. No nosso caso, estas poderiam ser as interfaces MIPI-CSI, MIPI-DSI e LVDS. Todas essas interfaces utilizam sinalização diferencial de baixa tensão e possuem uma linha de clock dedicada e pelo menos duas linhas de dados. Elas requerem muito espaço de roteamento porque o comprimento de cada linha de dados deve ser compatibilizado com a linha de clock dentro de uma certa margem de tempo. Compatibilizar o comprimento de múltiplos pares diferenciais pode exigir muito espaço, pois é muito provável que um ou mais pares dentro da interface introduzam um atraso significativo que deve ser levado em conta. Ao rotear essas interfaces primeiro, podemos garantir que haverá espaço suficiente para a sintonia de comprimento mais tarde.

Colocar VIAs de caminho de retorno perto das transições de camada desses pares diferenciais de alta velocidade também é importante para garantir a integridade do sinal. As VIAs de caminho de retorno podem ocupar espaço em múltiplas camadas, então essas VIAS devem ser colocadas assim que uma transição de sinal for realizada.

Em seguida, podemos rotear as outras interfaces de alta velocidade, como PCIe, USB, HDMI e Ethernet. Essas interfaces têm requisitos menos rigorosos para o emparelhamento de comprimento entre pares, então não precisamos dedicar tanto espaço para o emparelhamento de comprimento. No entanto, uma gestão sólida do caminho de retorno e abordagens básicas de design de alta velocidade nessas sinalizações ainda são muito importantes, embora colocando-as em segundo na lista de prioridades de roteamento.

Por último, mas não menos importante, podemos rotear as interfaces de menor velocidade restantes, como SDIO, GPIO, RGMII e outros barramentos diversos, como UART ou I2C e SPI. Essas interfaces ainda operam em taxas de borda alta, o que significa que ainda precisamos tratá-las como sinais de alta velocidade.

Roteamento da camada interna de sinal 1

Roteamento da camada interna de sinal 2

Roteamento da Camada Inferior

No caso da placa PiMX8, podemos tratar a camada inferior como uma camada de roteamento interna em termos de espaço disponível. A maioria dos componentes ativos é colocada na camada superior do módulo, deixando apenas um punhado de reguladores de tensão e componentes passivos, como capacitores de desacoplamento e resistores de configuração, na camada inferior.

A prioridade de roteamento na camada inferior é a mesma que para as camadas internas, então começaremos pelas interfaces MIPI-CSI, MIPI-DSI e LVDS. No módulo PiMX8, um multiplexador de alta velocidade pode selecionar entre as portas DSI e LVDS. Esse componente é colocado na camada inferior, próximo ao conector de placa para placa. Devido ao pinout do multiplexador, há um atraso significativo em uma das linhas de sinal conectadas ao mux. Teremos que analisar isso mais de perto durante o processo de correspondência de comprimento, mas precisamos reservar algum espaço na camada inferior para permitir um atraso maior.

Pinout do multiplexador com uma linha longa na interface

Roteamento na camada inferior do módulo PiMX8

Existem alguns cenários no módulo PiMX8 que requerem atenção especial durante o ajuste de atraso. Faremos uso extensivo de sinais X para superar alguns desses desafios. O que exatamente são esses desafios, e como podemos implementar sinais X para fornecer um ajuste preciso de atraso sobre um componente compartilhado por várias interfaces, será parte da próxima atualização. Fique atento!