Pi.MX8 プロジェクト - ボードレイアウト パート3

チャプター

Board Layout Part 3

| Created: June 24, 2024PCB Assembly

| Coming soonPi.MX8オープンソースコンピュータモジュールプロジェクトの新しいインストールメントへようこそ!このシリーズでは、NXPのi.MX8Mプラスプロセッサを基にしたシステムオンモジュールの設計とテストについて詳しく説明します。

前回のアップデートでは、レイアウト準備を完了しました。これには、インピーダンスプロファイルの作成、ボード製造業者の仕様に従った設計ルールの追加、特別な設計ルールを適用すべきエリアの定義が含まれます。また、LPDDR4インターフェースのルーティングも完了しましたが、長さ調整は(今のところ)行っていません。

DRAMインターフェースの長さ調整を始める前に、Pi.MX8モジュール上の残りのインターフェースのルーティングを見ていきます。ボード上には、多くの高速および低速バスがあり、その中には多くのルーティングスペースを必要とする広い並列バスもあります。各インターフェースに十分なスペースを割り当てるために、まずモジュールの各ルーティング層について大まかなフロアプランを作成します。

ルーティング計画

ルーティングプランは、利用可能な信号層全体に高速および低速インターフェースをどのように分配するかを決定するのに役立ちます。あらかじめ大まかなガイドを設定することで、現在作業している層に十分なルーティング用の不動産が利用可能であることを確認できます。これにより、層の移行を最小限に抑え、ルーティングプロセス中に行う再作業の量を減らすことができます。

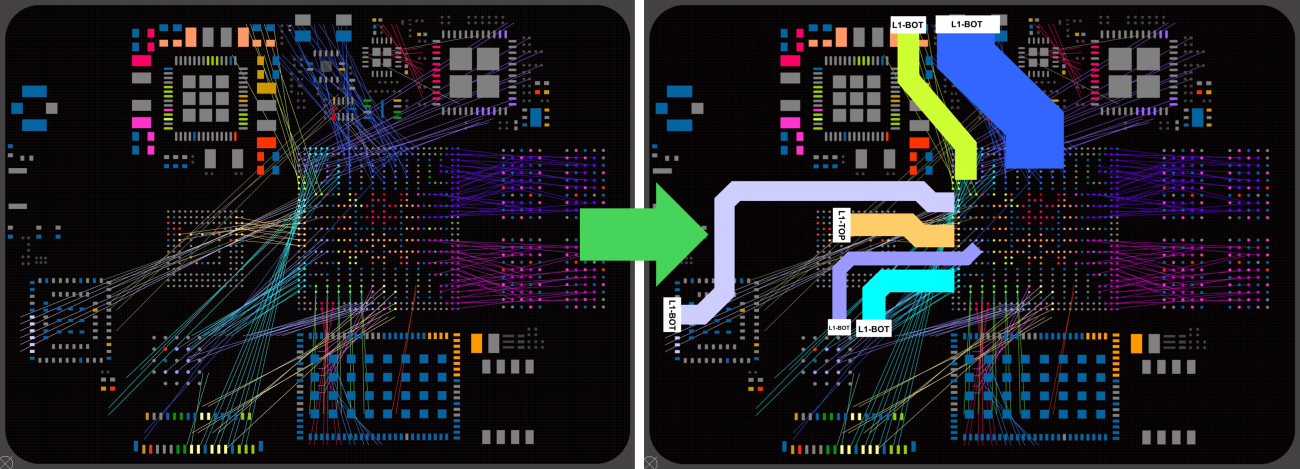

レイアウト計画を設定する方法はいくつかあり、主に利用可能なツールに依存します。私たちに必要なのは、既存の画像の上にスケッチを描くことができる基本的な描画ツールです。この例では、Inkscapeを使用します。

Inkscapeでは、背景画像を追加して、配置されたコンポーネントと未ルーティングのインターフェースをカラーのエアワイヤとして表示できます。このスクリーンショットでは、信号層でルーティングされるネットにのみ焦点を当てるため、電源ネットは非表示になっています。回路図では、各電源ネットにネットクラス指令を配置しており、レイアウトエディターで関連するネットクラスを有効にするか非表示にすることで、どのネットがプレーン層でルーティングされるかを簡単に識別できます。

実際のルーティングには、Inkscapeで線を追加して、対応するレイヤー上でルートしたいインターフェースを表します。これらの線の幅を調整して、インターフェースでルーティングされる信号の数を表現できます。線の色は、背景画像から選択して、どのインターフェースが表されているかを識別しやすくすることができます。

レイヤー間の移行にもすべてのレイヤーにスペースが割り当てられる必要があるため、各線の末端にブロックを追加してレイヤー移行を詳細にします。

Inkscapeでのレイアウト計画、背景画像としてAltium Designerのスクリーンショットを使用

上記のプロセスを各ルーティングレイヤーで繰り返した後、実際のルーティングプロセスを開始できます。

トップレイヤーのルーティング

ルーティング戦略を確立したので、まずはトップレイヤーのインターフェースのルーティングから始めましょう。トップレイヤーのコンポーネントのファンアウトルーティングは既に完了しているため、残りのスペースをすべてシグナルルーティングに使用できます。残されたスペースは多くありませんが、内部シグナルレイヤーのルーティングを後で容易にするために、内部レイヤーのルーティングに干渉しない領域に戦略的にVIAを配置することで、まだ利用可能です。これは、あらかじめレイアウトを計画することのもう一つの利点であり、そうでなければこれらの領域はこの段階で定義されていません。

トップレイヤーのPiMX8モジュールのルーティング

トップレイヤーにトレースを配置する際には、フィデューシャルやラベルなどの機能をトップレイヤーに追加するためのスペースが必要であることも考慮する必要があります。レーザーエッチングされたデータマトリックスコードは、均一なコントラストを提供するために、固体の銅領域またはトレースのない領域を必要とする場合があり、これらの領域はルーティングに使用できません。

内部シグナルレイヤーのルーティング

ほとんどの接続は、レイヤースタックマネージャーで定義した2つの内部信号層に配置されます。まず、すべての高速同期インターフェースのルーティングから始めましょう。この場合、MIPI-CSI、MIPI-DSI、LVDSインターフェースなどが該当します。これらのインターフェースはすべて低電圧差動信号を使用し、専用のクロックラインと少なくとも2つのデータラインを持っています。各データラインの長さは、一定のタイミングマージン内でクロックラインに合わせる必要があるため、多くのルーティングスペースが必要です。複数の差動ペアの長さを合わせるには、かなりのスペースが必要になることがあります。なぜなら、インターフェース内の1つ以上のペアが、考慮しなければならない大きな遅延を引き起こす可能性が非常に高いからです。これらのインターフェースを最初にルーティングすることで、後で長さ調整のために十分なスペースが確保できるようになります。

これらの高速差動ペアの層間遷移の近くにリターンパスVIAを配置することも、信号の整合性を確保するために重要です。リターンパスVIAは複数の層にわたってスペースを取ることができるので、信号の遷移が配置されたらすぐにこれらのVIAを配置するべきです。

次に、PCIe、USB、HDMI、Ethernetなどの他の高速インターフェースをルーティングできます。これらのインターフェースは、ペア間の長さの一致に関してはそれほど厳格な要件を持っていないため、長さの一致に多くのスペースを割く必要はありません。ただし、これらの信号に対しては、しっかりとしたリターンパス管理と基本的な高速設計アプローチが非常に重要ですが、ルーティング優先リストでこれらを二番目に配置します。

最後に、SDIO、GPIO、RGMII、その他の雑多なバス(UARTやI2C、SPIなど)などの残りの低速インターフェースをルーティングできます。これらのインターフェースは依然として高いエッジレートで動作するため、高速信号として扱う必要があります。

内部信号層1のルーティング

内部信号層2のルーティング

ボトムレイヤーのルーティング

PiMX8ボードの場合、利用可能なスペースの観点からボトムレイヤーを内部ルーティング層として扱うことができます。モジュールのトップレイヤーにはほとんどのアクティブコンポーネントが配置されており、ボトムレイヤーには電圧レギュレータやデカップリングキャパシタ、設定用抵抗などの受動部品のみがわずかに残っています。

ボトムレイヤーのルーティング優先順位は内部レイヤーと同じであるため、MIPI-CSI、MIPI-DSI、LVDSインターフェースから始めます。PiMX8モジュールでは、高速マルチプレクサーがDSIポートとLVDSポートの間で選択できます。このコンポーネントは、ボード間コネクタに近いボトムレイヤーに配置されます。マルチプレクサーのピン配置のため、muxに接続された信号線の1つには大きな遅延があります。長さのマッチングプロセス中にこれをより詳しく見ていく必要がありますが、より大きな遅延を許容するためにボトムレイヤーにいくらかのスペースを確保する必要があります。

インターフェース内の1つの長いラインを持つマルチプレクサーのピン配置

ボトムレイヤールーティング PiMX8モジュール

PiMX8モジュールには、遅延調整中に特別な注意が必要なシナリオがいくつかあります。これらの課題を克服するために、X-シグナルを広範囲に使用します。これらの課題が具体的に何であり、複数のインターフェースで共有されるコンポーネントに対して正確な遅延調整を提供するためにX-シグナルをどのように実装できるかは、次のアップデートの一部となります。お楽しみに!