Addressing Skew Sources in High Speed PCBs

Sometimes, when we talk about skew, we aren't as specific as we should be. Most discussions of skew and jitter deal with the type of skew incurred during routing, namely due to length mismatches in differential pairs and fiber weave-induced skew. In fact, there are many different sources of skew that contribute to total jitter on an interconnect, and it's important to quantify these in serial and parallel buses that require precise timing control.

If you compile a list of skew sources, you'll see that fiber weave-induced skew is only one entry on a long list of skew sources. We'll look at this list of possible skew sources below, and we'll see how they affect the operation of your PCB. From the list below, we'll see that some of these issues with skew are not simply solved by paying attention to the fiber weave construction in a PCB substrate.

Jitter = Total Skew

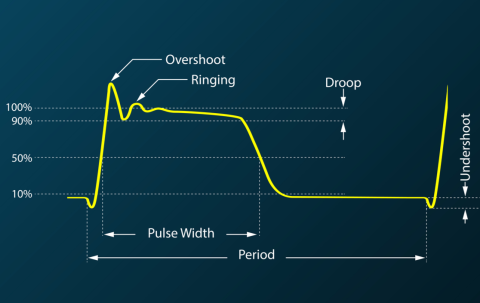

The first point to note here is the difference between jitter and skew, as well as the difference between random and deterministic jitter/skew. Probably the best definition of skew I have seen comes from an old Texas Instruments application note written by Steve Corrigan. In this application note, Steve describes jitter as "the sum total of all skews". This should illustrate why some authors will sometimes use "jitter" and "skew" interchangeably (I've mistakenly done this myself). JEDEC has its own definitions for jitter and skew.

Random or Deterministic?

No matter which term you use, there is sometimes an association between "jitter" and random skew, while the term "skew" would be used to reference pseudorandom or deterministic skew. In reality, there is only one source of random skew: thermal noise. Random motion of the atoms and molecules that make up all matter does contribute to noise in electronic circuits, but it only matters in highly precise low-level measurements. In the majority of applications, the skew sources you need to worry about are deterministic and can be linked back to a root cause.

Sources of Skew

The table below shows a list of skew sources that can arise in a PCB, as well as a brief description where each arises.

|

|

|

|

|

|

|

|

|

|

|

|

|

Reflections |

|

|

|

|

There is a lot going on in this table; we have multiple sources of skew have little to do with fiber weave effects and cannot be perfectly solved by applying length matching! However, if you look below the first row, we see that most of these sources of skew appear at the system level due to some interplay between different functional blocks in a system, or between chips and the board.

Can You Eliminate All Skew?

Unfortunately the answer is "no", you can't ever totally eliminate skew. Even if you suppressed all the deterministic sources of skew listed above, there will still be some amount of random skew due to thermal noise. Although you can never completely eliminate skew, you can work towards minimizing it with a few basic layout guidelines.

- Glass weave: Use a tighter weave material like spread glass; this directly confronts fiber weave-induced skew.

- Crosstalk and parasitics: Learn what cause parasitic coupling between two interconnects and plan the layout to reduce this coupling. The easiest way to deal with parasitic coupling is proper stackup design that enables appropriate ground placement.

- Termination: Ensure channels are terminated with flat target impedance up to the required bandwidth limit for your channels. In other words, ensure channels are terminated at least up to the channel's Nyquist frequency.

- Power integrity: Ensure components that require precise timing for high-speed signals or precision timing in edge rates are receiving stable power.

After dealing with these issues, standard differential or parallel bus delay tuning structures can be applied to compensate the remaining skew in your PCB to deal with any length mismatch. At this point, even if there was some residual skew in your interconnects, the majority of skew would be addressed and signals would still be aligned at receiver I/Os.

The routing featuers in Altium Designer® can help you apply accurate impedance calculation results as design rules, as well as design your layer stack in your high speed PCB to minimize noise coupling that contributes to the skew sources listed above. When you’re ready to share your designs with collaborators or your manufacturer, you can share your completed designs through the Altium 365™ platform. Everything you need to design and produce advanced electronics can be found in one software package.

We have only scratched the surface of what is possible to do with Altium Designer on Altium 365. Start your free trial of Altium Designer + Altium 365 today.