Switching Regulator Layout: One or Two Layers?

Take a look at the typical switching regulator layout on a PCB; usually, everything is placed on a single layer for multiple reasons. Sometimes, such as in low-power scenarios, the circuit is just physically small, so there is not really a need to use two layers to save space. For larger switching regulators, the physically large size of components means that placement on two layers might save some space in theory, but this makes placement inside an enclosure more difficult due to mounting constraints.

When you have a switching regulator of mid-range size, which might have a few discretes and some MOSFETs, you have some flexibility to place everything on two layers as you typically don’t have large mechanical pieces (heatsink or fans) or tall caps/inductors. Should you place everything on a single layer or two layers, and what will be the impact on performance?

As it turns out, the major impact of placement on two layers is in terms of parasitics and noise coupling. You could likely make the design smaller and possibly have lower radiated/received EMI, but you might create strong coupling to nearby interconnects if not laid out properly. Let’s look at this deeper to see where noise begins to create problems and what are some solutions to prevent noise coupling.

Noise in One-Layer and Two-Layer Switching Regulators

All switching regulators generate noise at their dV/dt node and dI/dt loop. For more complex topologies, like half-bridge/full-bridge topologies, the switching node can move between different locations in the design depending on the phase difference between switching FETs. If there is a PFC circuit in the board and it is running in critical conduction mode, then it will modulate deeply at its high and low side switching nodes to give high dV/dt spikes. In any case, the dV/dt node will determine the location of the dI/dt loop. Together, these will determine how noise might be coupled around the design.

The example buck converter circuit diagram below shows where these nodes exist. Similar diagrams could be drawn for a boost converter, or for an isolated topology. The switching node and the pulsating current loop are indicated in the diagram; these are the points where the circuit will radiate the most noise.

This type of circuit could be laid out using a gate driver to generate the PWM pulse and modulate Q1. More advanced bridge or resonant topologies will basically do the same thing, but the current loop and the dV/dt node may swap between different points depending on the topology.

In determining where to put the components (single vs. double sided PCB layout), you will be balancing the area taken up by the regulator vs. the switching noise the regulator can couple into other circuits. To see some advantages of each style, let’s look at some examples.

Single-Layer PCB Layout Example

For this example, I’ll look at a buck regulator IC (TPS562201 from Texas Instruments) that could supply up to 2 A of current. The circuit uses a feedback loop with a resistor divider to sense the output voltage and adjust a one-shot timer to trigger internal MOSFETs that will generate switching. Therefore, the output dI/dt loop will span the ground plane on the IC’s die and will need to have uniform ground beneath it.

We have two goals when transferring this circuit to the layout:

- Prevent dV/dt noise from SW_OUT and magnetically-coupled noise from reaching the feedback loop through parasitic capacitance and parasitic inductance.

- Ensure the dI/dt loop is as small as possible so that it does not radiate strongly and so that the inductance of conductors in this loop do not contribute to excessive transient overshoot during switching.

An example of a typical approach to laying out this small switching regulator on a PCB is shown below. I’ve roughly traced out the path of the switching current on the board so that we can see where the design is susceptible to radiate. The stackup uses 4 layers. In this design, we have a feedback line going from R1 back to U1 (the trace on Layer 2), as well as the big copper switching node (SW_OUT).

The feedback trace might be susceptible to some noise coupling, which is rather important in this application. This line is being used to determine when an internal one-shot timer needs to be reset so that the internal MOSFET can be triggered for the next switching cycle. Therefore, you would like to avoid strong noise and ensure an accurate feedback measurement. In this example, placing it on Layer 2 and surrounding it by ground is a good strategy to ensure low inductance. Keeping this trace safe from switching noise from L1 could be done in three ways:

- Keep it on the bottom layer and move it farther away from L1 and SW_OUT

- Place it on the top layer, surround it with some copper pour, and shield it with carefully sized switching vias

- Put the trace on the back layer so that it is totally shielded by GND

If we want to go with #3, we might as well just put the output caps on the back layer as well! Let’s see what this looks like.

Caution With Two-Layer Regulator Circuits

Two-layer circuits with a current loop on the output side are attractive for layout in two layers. This arrangement is sometimes called a clamshell design due to the arrangement of the LC section in the regulator. The main reason you might opt for this type of routing is to control the parasitics, which then gives you control over coupling of switching noise onto other circuits. This is highly desirable if you’re laying out a small form factor power regulator that might be close to other circuits.

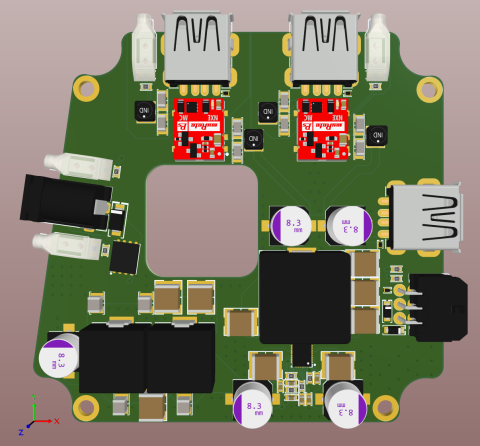

Our modified two-layer circuit is shown below (Layer 1 in focus). I’ve left U1, C5, and L1 on the top layer; all the smaller passives are on the bottom layer. If this board were going to be put into an enclosure with small standoffs, it wouldn’t have any problems with bulky components on two layers. We’re also able to make the board much smaller compared to the previous layout.

The bottom layer is shown below. By moving the passives to the bottom layer, we’ve tightened up the feedback loop so that it has lower inductance and it is totally shielded from L1 by ground on Layer 2 and 3. Another benefit is SW_OUT; it is also totally shielded from the feedback loop.

How Can We Improve the Layout?

I'm a believer that no layout is perfect, and there is always some improvements to be made. The above layout will technically work, but a few changes in the layout will do some good and help make the layout a bit more compact. The downside of the layout is the magnetic field is being generated along the surface of the board, so we cannot route any data signals along the top and bottom edges of the PCB. This is something to keep in mind when placing this design into another layout that will include some data signals.

The other way to improve the layout is to put those feedback resistors and the feedback trace. Ideally, we would like to have those resistors (R1 and R2) closer to the feedback pin. If these were current sense resistors, then we would also want to implement a Kelvin connection to ensure lowest possible modification of the feedback network resistance. While placing this on the back layer and adding some GND helps add some shielding, it's better to place those resistors close to the feedback pin for the most accurate tracking of the output voltage.

If we just apply a 90 degree rotation on U1, and shift the components around, we can get the layout a bit more compact and reduce the board size.

I like this better because most of the SW_OUT node is above GND, rather than above the feedback trace. The dI/dt loop through C3 and C4 is also much tighter. Moving those feedback resistors also helps reduce the total size of the PCB layout.

If this were just a simple regulator module and the total layer count was 2 copper layers, then we wouldn't have any other levers to pull to shield any of the sensitive traces from the switching node other than to just move the traces farther from SW_OUT and increase the total route distances. If this layout were to be used in a real product with some other components, then you would likely have some GND pour or an entire GND plane on an internal layer (e.g., at least a 4-layer board). This gives you a way to further reduce both the loop inductance for the feedack trace/SW_OUT and to block these control traces from the SW node, thereby giving you some protection from noise coupling.

Scaling Up

If you understand these principles with a single power MOSFET, then you can scale this up to a synchronous converter with two MOSFETs, or to a more advanced bridge converter, resonant converter, or multiphase converter. Those layouts are more complex because there are more locations where noise can couple to other circuits in your PCB layout. However, following the noise coupling principles above will help ensure you’re successful if you’re designing more advanced power topologies.

When you need to place and route your switching regulator layout, use the CAD features in Altium Designer®. You’ll have the freedom to quickly place components on either layer and set your stackup to help control noise. When you’re ready to share your designs with collaborators or your manufacturer, you can share your completed designs through the Altium 365™ platform. Everything you need to design and produce advanced electronics can be found in one software package.

We have only scratched the surface of what is possible to do with Altium Designer on Altium 365. Start your free trial of Altium Designer + Altium 365 today.