Co to są chiplety i jak są wykorzystywane w pakowaniu?

Chiplety to małe kości IC o specjalistycznej funkcjonalności. Są one zaprojektowane do łączenia w celu utworzenia większego układu scalonego, co jest zgodne z trendem w przemyśle półprzewodnikowym dotyczącym heterogenicznej integracji. Możliwość wyboru z zestawu małych, wysoko wyspecjalizowanych układów, a następnie łączenie ich w celu uzyskania pożądanej ogólnej funkcjonalności, stanowi znaczący krok naprzód w porównaniu z tradycyjnym podejściem systemu na chipie (SoC) do pakowania półprzewodników. Główni producenci wyprodukowali procesory komputerowe, które łączą wybraną liczbę chipletów, zamiast podążać tradycyjną ścieżką monolitycznej produkcji półprzewodników, gdzie urządzenie jest fabrykowane na jednym kawałku krzemu.

Chociaż pomysł chipletów istnieje od dziesięcioleci, opakowania oparte na chipletach napędzają nowe typy komponentów, produktów i systemów dla specjalistycznych zastosowań. Te komponenty są dostosowane do konkretnych aplikacji, a coraz więcej firm wchodzi do gry projektowania układów z chipletami jako ich głównym procesorem. Na podstawie liczby prac badawczych, zgłoszeń patentowych i artykułów technicznych, które znajdziesz online, jasne jest, że komponenty oparte na chipletach są tutaj, aby zostać.

Jeśli jesteś projektantem systemów i rozważasz opcje procesorów, możesz nie zdawać sobie sprawy, że chiplety stanowią fundament Twojego systemu. Jednak chiplety są kręgosłupem umożliwiającym różnorodną funkcjonalność znajdowaną w nowoczesnych układach, a koncepcja pakowania nadal napędza integrację nowych funkcji w projektach układów. Przykłady obejmują integrację bloków FPGA i bloków akceleratorów AI do tego samego pakietu co pamięci, CPU, a nawet komponenty RF.

Dlaczego chiplety?

Koszt i wydajność to dwa najważniejsze problemy w projektowaniu i produkcji układów scalonych. Ostatnie lata przyniosły spowolnienie skalowania Dennarda i prawa Moore'a, co skutkuje dłuższymi odstępami czasu między węzłami technologii procesowej. Ponadto, integracja tranzystorów na monolitycznym chipie staje się coraz bardziej wyzwaniem, ponieważ jest niewiele dostępnych opcji dla skalowania urządzeń. Te wyzwania zmniejszyły ROI dla monolitycznych półprzewodników z powodu droższych procesów produkcyjnych.

Jedynym sposobem na zwiększenie liczby zintegrowanych jednostek funkcjonalnych przy tej samej wielkości tranzystora jest rozszerzenie obszaru chipa, zarówno w płaszczyźnie urządzenia, jak i pionowo. Problem zwiększania obszaru chipa polega na tym, że większe chipy są bardziej podatne na defekty produkcyjne, co ogranicza wydajność płytek i zwiększa cenę produktów dostarczanych klientom. W konsekwencji monolityczne chipy stają się coraz mniej zdolne do zapewnienia pożądanej wydajności w świetle rosnących wymagań obliczeniowych.

W związku z tym, aby wspierać aplikacje o wysokiej mocy obliczeniowej takie jak AI/ML na urządzeniu, ultrabłyskawiczne sieci, fuzję sensorów i urządzenia mobilne nowej generacji, zaobserwowaliśmy pojawienie się systemów opartych na chipletach umożliwiających kosztowo-efektywny rozwój elektroniki wysokiej wydajności. Obejmuje to zaawansowane SoC, procesory do komputerów/stacji roboczych oraz GPU.

Przełamywanie "murów powierzchniowych"

Problem "murów powierzchniowych" wynika z niezgodności między potrzebą dużych chipów w systemach o wysokiej wydajności obliczeniowej a niską wydajnością produkcji półprzewodników. Mur powierzchniowy odnosi się do tego wyzwania w monolitycznej produkcji półprzewodników, gdzie większe chipy są używane do zwiększenia gęstości funkcji, ale również zwiększa się liczba defektów. W miarę przechodzenia możliwości produkcyjnych do bardziej zaawansowanych węzłów, wydajność procesu maleje, a tym samym koszt dla końcowego klienta wzrasta. Dlatego zawsze istnieje motywacja do zmniejszenia ryzyka produkcji tych produktów poprzez eliminację szans na defekty.

Rozwiązanie problemu murów powierzchniowych mogłoby zmniejszyć ogólny koszt produktu końcowego poprzez redukcję odpadów podczas produkcji. Chiplety w zasadzie dywersyfikują profil ryzyka produktu, rozpraszając go na wiele półprzewodnikowych kostek. Końcowym rezultatem jest zmniejszenie kosztów oraz możliwość znacznie większej dywersyfikacji funkcjonalności niż w komponencie monolitycznym.

Zmniejszenie kosztów

Kilka chipletów jest łączonych za pomocą specjalnych technik pakowania, tworząc większy układ scalony jako alternatywę dla struktury monolitycznej. Ponieważ chiplety są produkowane na mniejszej powierzchni, zazwyczaj na okrągłych krążkach, wpływ defektów produkcyjnych jest zmniejszony, a wykorzystanie powierzchni wzrasta. W rezultacie koszt jest zmniejszony, ponieważ wydajność krążka jest znacznie wyższa, gdy używa się chipletów do stworzenia komponentu.

Integracja heterogeniczna to kolejna znacząca zaleta chipletów, szczególnie pod względem zmniejszenia kosztów projektowania i produkcji układów scalonych. Każdy chiplet może być produkowany przy użyciu różnych węzłów procesowych, co AMD ujawniło, że zostało zrobione z ich produktem Ryzen 7. Innym przykładem od AMD jest niedawny patent na GPU oparte na chipletach; architektura tego systemu jest pokazana na oryginalnej ilustracji poniżej:

Różne materiały (np. chiplety GaN i Si) mogą być również łączone w tym samym opakowaniu przy użyciu tego podejścia. Użycie różnych węzłów technologicznych procesu zmniejsza ogólne ryzyko wbudowane w produkt; największe ryzyko jest ograniczone tylko do chipletu, który jest produkowany w najbardziej zaawansowanym węźle procesowym, a nie na całym chipie.

Ponowne wykorzystanie projektu

Gdy chiplet zostanie opracowany, może być ponownie użyty, co redukuje koszty testowania i weryfikacji. Efektywność kosztowa procesu projektowania układów scalonych jest znacznie wyższa dzięki wykorzystaniu modułów chiplet, ponieważ mogą być one ponownie używane. Jednym ze scenariuszy ponownego wykorzystania chipletów jest zaprojektowanie i wyprodukowanie tylko głównego chipletu dla układu scalonego (IC), podczas gdy pozostałe chiplety w pakiecie są pozyskiwane od innego dostawcy. Korzystanie z tego podejścia z gotowymi chipletami od wielu dostawców, lub przez ponowne wykorzystanie IP w nowym projekcie, znacznie redukuje całkowite koszty projektowania i weryfikacji produktu.

W przypadku gdy wymagana jest aktualizacja systemu, jeden chiplet może być zamieniony na inny chiplet wewnątrz opakowania. Należy zauważyć, że samo opakowanie może wymagać aktualizacji, ale jest to znacznie mniej trudne zadanie projektowe niż przeprojektowanie całego monolitycznego komponentu. Mała część systemu może być również przeprojektowana bez ponoszenia nowych kosztów weryfikacji, które pojawiłyby się w monolitycznych pakietach półprzewodnikowych. Ta metoda ponownego wykorzystania chipletów jest określana jako „heterogeniczne ponowne wykorzystanie”.

Inny scenariusz ponownego wykorzystania chipletów polega na integracji wielu identycznych chipletów w ten sam system. Metoda ta jest idealna dla skalowalnych systemów i znacznie poprawia ich efektywność przy jednoczesnym redukowaniu kosztów. Metoda ta jest określana jako homogeniczne ponowne wykorzystanie, a główną zaletą jest to, że zwiększenie liczby chipletów w architekturze wystarczy, aby sprostać różnym wymaganiom dotyczącym wydajności i mocy.

Technologie pakowania chipletów

Aby tworzyć produkty oparte na chipletach, potrzebne są umiejętności projektowe, matryce, połączenia między matrycami oraz strategia produkcji. Wydajność, cena i dojrzałość technologii pakowania chipletów mają znaczący wpływ na zastosowanie chipletów. Zgodnie z różnicami w medium i metodach połączeń, technologie pakowania używane do łączenia chipletów można sklasyfikować na trzy grupy:

-

Pakowanie na podłożu

-

Pakowanie na interposerze krzemowym

-

Pakowanie warstwy redystrybucyjnej (RDL)

-

Wbudowany mostek wieloukładowy do połączeń (EMIB)

Pakowanie na podłożu

W pakowaniu na podłożu popularnym wyborem podłoża jest materiał organiczny, ponieważ są one łatwo dostępne. Podobnie jak w przypadku konwencjonalnych PCB, połączenia przewodzące są tworzone przez proces trawienia, który jest niezależny od innych procesów używanych w produkcji półprzewodników. Jest to najlepiej znana wczesna inkarnacja 2D heterogenicznej integracji.

Przez projekt flip-chip lub stosowanie, kilka matryc może być łatwo połączonych z podłożem o wysokiej gęstości. Ponadto, koszty materiałów i produkcji związane z tym są minimalne, ponieważ ta technologia nie zależy od procesu produkcji chipów. Główną wadą korzystania z tej technologii jest niska gęstość pinów I/O i wynikające z tego ograniczenie w przepustowości połączeń w tych pakietach.

Pakowanie na interposerze krzemowym

Ta technologia obejmuje technologie pakowania 2.5D i 3D, gdzie układy scalone są budowane poziomo na interposerze (2.5D) lub układane pionowo (3D). Aby zaimplementować połączenia i komunikację między kośćmi, warstwa interposera krzemowego jest umieszczana między podłożem a kośćmi. Interposer jest jak miniaturowa płyta drukowana, zapewniając podstawę dla połączeń elektrycznych między chipletami. Tkanina łącząca jest zbudowana z metalicznych kontaktów (zwanych mikro wypustkami) i przez-krzemowych przelotek (TSV) biegnących wewnętrznie w opakowaniu. Są one używane do połączenia kości z interposerem, a złącza interposera z podłożem opakowania z wzorem lądowania BGA.

Te produkty mają wyższą gęstość I/O przy zmniejszonym zużyciu energii i niższym opóźnieniu transmisji. Jest to umożliwione przez mniejszą długość ścieżki i rozstaw między mikro wypustkami a TSV. Jedyną znaczącą wadą tej technologii są zwiększone koszty produkcji.

Opakowania RDL

Technologia pakowania warstwy redystrybucyjnej (RDL) nie używa podłoża, zamiast tego polega na bezpośrednim osadzaniu dielektryka i metalu bezpośrednio na górnej powierzchni krzemienia. Technologia ta jest również określana jako technologia ‘fanout’. Aby przenieść projekt przewodu, warstwa redystrybucyjna jest konstruowana tak, aby porty I/O na każdym chiplecie były ukształtowane wokół urządzenia. Skracając długość obwodu, RDL zapewnia lepszą integralność sygnału (mniejsze straty i zniekształcenia).

Wbudowany wielokostkowy mostek łączący

EMIB to technologia, która używa cienkich sekcji krzemowych wafli osadzonych w materiałach organicznych jako podłoża dla połączeń kość-do-kości. Problem wyższych kosztów w zaawansowanych produktach można rozwiązać, stosując pakowanie mostkowe z różnorodnymi chipletami. Ta hybrydowa technologia pakowania jest kombinacją pakowania na podłożu i na interposerze. Cienkie warstwy krzemowe, zazwyczaj mniejsze niż 75 mikronów, są nanoszone na podłoże i używane do tworzenia połączeń międzykościowych, a te warstwy są osadzone w organicznej warstwie podłoża.

Koncepcja ta opiera się na tych samych pomysłach, co ELIC używane w HDI PCB, gdzie tkanina łącząca każdą warstwę łączy wiele kości z wewnętrznymi warstwami w izolującym (organicznym) podłożu. Część EMIB opakowania to krzemowy mostek zapewniający połączenia o wysokiej przepustowości między chipletami.

Podsumowanie

Oczekuje się, że chiplety będą kontynuować rewolucjonizowanie aplikacji wymagających komponentów o wysokiej mocy obliczeniowej, jak również różnorodnej funkcjonalności w jednym opakowaniu. Te produkty obecnie kierują się na zaawansowane technologie takie jak 5G, IoT, motoryzacja, edge computing, obrazowanie medyczne, edge computing, AI, urządzenia mobilne i wiele innych.

Dzisiaj główni producenci półprzewodników tacy jak Intel, Marvell i AMD zainteresowali się technologią chipletów, i możemy oczekiwać, że więcej firm będzie badać tę opcję. W miarę jak rynek dla IP chipletów się rozwija, podobnie jak rynek dla wielu innych komponentów, więcej firm półprzewodnikowych bez własnych fabryk może przyjąć podejście do półprzewodników na zamówienie, zamiast budować systemy z dyskretnymi komponentami.

Teraz, gdy Intel, AMD i TSMC uzgodniły wspólny standard dla połączeń chipletów, czy zobaczymy większe rozpowszechnienie tych projektów przez inne firmy? Można mieć nadzieję, że rynek dla tych komponentów się rozwinie, ponieważ będzie to zachęcać do większej innowacji na poziomie pakowania poza dużymi producentami półprzewodników.

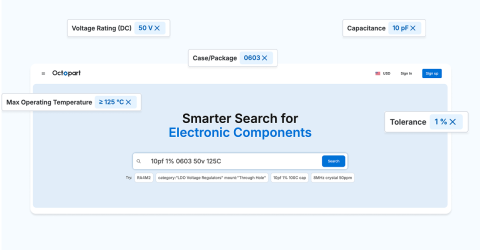

Gdy na rynku pojawią się komponenty oparte na chipletach z zaawansowanym pakowaniem, projektanci systemów mogą używać zaawansowanych funkcji wyszukiwania i filtracji w Octopart, aby znaleźć wszystkie zaawansowane komponenty potrzebne do zaawansowanych projektów. Korzystając z wyszukiwarki elektroniki Octopart, uzyskasz dostęp do aktualnych danych cenowych dystrybutorów, zapasów części i specyfikacji części, i wszystko to jest swobodnie dostępne w przyjaznym dla użytkownika interfejsie. Zobacz naszą stronę z układami scalonymi, aby znaleźć potrzebne komponenty.

Bądź na bieżąco z naszymi najnowszymi artykułami, zapisując się do naszego newslettera.