チップレットとは何か、そしてパッケージングでどのように使用されるのか?

チップレットは、特化した機能を持つ小さなICダイです。これらは、半導体業界の異種統合のトレンドに従って、より大きな集積回路を構成するために組み合わされるように設計されています。小さく、高度に特化したチップの選択肢から選び、これらを組み合わせて所望の全体的な機能を生み出す能力は、半導体パッケージングにおける従来のシステムオンチップ(SoC)アプローチからの大きな進歩です。主要なベンダーは、従来の単一のシリコン片上にデバイスを製造する方法ではなく、選択した数のチップレットを組み合わせたコンピュータプロセッサを製造しています。

チップレットのアイデアは数十年前から存在していましたが、チップレットベースのパッケージングは、特殊なアプリケーション向けの新しいタイプのコンポーネント、製品、およびシステムを推進しています。これらのコンポーネントは特定のアプリケーション向けにカスタマイズされており、より多くの企業がチップレットをコアプロセッサとして重視するチップ設計に参入しています。オンラインで見つかる研究論文、特許出願、技術記事の数からも、チップレットベースのコンポーネントがここにとどまることは明らかです。

システムデザイナーであり、プロセッサのオプションを検討している場合、チップレットがシステムの基盤を形成していることに気づかないかもしれません。しかし、チップレットは現代のチップに見られる多様な機能を可能にする背骨であり、パッケージングコンセプトは新しい機能のチップデザインへの統合を続けて推進しています。例としては、メモリ、CPU、さらにはRFコンポーネントと同じパッケージにFPGAブロックやAIアクセラレータブロックを統合することが挙げられます。

なぜチップレットなのか?

コストと性能は、チップ設計と製造における最も切迫した問題の2つです。近年、デナードのスケーリングとムーアの法則が鈍化し、プロセス技術ノード間の時間が長くなっています。さらに、単一のシリコン片上でのトランジスタの統合は、デバイスのスケーリングに利用可能なオプションが少なくなるにつれて、ますます困難になっています。これらの課題は、より高コストの製造プロセスにより、単一の半導体のROIを低下させています。

同じトランジスタサイズで統合される機能ユニットの数を増やす唯一の方法は、デバイス平面または垂直方向にチップエリアを拡大することです。チップエリアを増やす問題は、より大きなチップが製造欠陥に対してより敏感になり、ウェハーの収率を制限し、顧客に提供される製品の価格を上昇させることです。その結果、単一のチップは、高まるコンピューティング要求を考慮すると、望まれる性能を提供することがますます困難になっています。

したがって、オンデバイスAI/ML、超高速ネットワーキング、センサーフュージョン、次世代モバイルデバイスなどの高計算アプリケーションをサポートするために、高性能電子機器のコスト効率の良い開発のためのチップレットベースのシステムの出現を目の当たりにしています。これは、高度なSoCからデスクトップ/サーバープロセッサやGPUにまで及んでいます。

「エリアウォール」の克服

「エリアウォール」とは、高性能コンピューティングシステムが大面積チップを必要とする一方で、半導体製造の歩留まりが低いというミスマッチから生じる問題です。エリアウォールは、大きなチップを使用して機能密度を増やすものの、欠陥数も増加するという、モノリシック半導体製造におけるこの課題を指します。製造プロセス能力がより先進的なノードに移行するにつれて、プロセス歩留まりは減少し、結果としてエンドカスタマーのコストは増加します。したがって、欠陥の可能性を排除することによって、これらの製品の製造リスクを軽減する動機が常にあります。

エリアウォールへの解決策は、製造中の廃棄を減らすことによって、エンド製品の全体的なコストを削減します。チップレットは、複数の半導体ダイにリスクプロファイルを分散させることによって、製品のリスクを本質的に多様化します。その結果、コストが削減され、モノリシックコンポーネントよりもはるかに大きな範囲で機能を大幅に多様化する能力が得られます。

コスト削減

複数のチップレットは特殊なパッケージング技術と組み合わせて、モノリシック構造の代わりとなる大きなICを構成します。チップレットは通常、円形のウェハー上でより小さな面積で製造されるため、製造欠陥の影響が減少し、面積利用率が向上します。その結果、チップレットを使用してコンポーネントを作成する場合、ウェハーの歩留まりが大幅に高くなるため、コストが削減されます。

異種統合は、特にICの設計および生産コストを削減する点で、チップレットのもう一つの重要な利点です。各チップレットは、AMDがRyzen 7製品で行ったように、異なるプロセスノードを使用して製造することができます。AMDからのもう一つの例は、このシステムのアーキテクチャを以下のオリジナルアートワークで示したチップレットベースのGPUの最近の特許です:

このアプローチでは、異なる材料(例えば、GaNおよびSiチップレット)も同じパッケージに組み合わせることができます。異なるプロセス技術ノードの使用により、製品に組み込まれた全体的なリスクが削減されます。最も高度なプロセスノードで生産されているチップレットにのみ、最高のリスクが限定され、チップ全体にわたってではありません。

設計の再利用

チップレットが開発されると、テストと検証のコストを削減しながら再利用することができます。チップレットモジュールの使用により、チップ設計プロセスのコスト効率は大幅に向上します。チップレットの再利用のシナリオの一つとして、ICのコアチップレットのみを設計・製造し、パッケージ内の残りのチップレットを別のベンダーから取得する方法があります。複数のベンダーから既製のチップレットを使用するこのアプローチ、または新しい設計でIPを再利用することにより、製品の総設計および検証コストを大幅に削減できます。

システムに更新が必要な場合、パッケージ内の一つのチップレットを別のチップレットに交換することができます。ただし、パッケージ自体を更新する必要があるかもしれませんが、これは全体のモノリシックコンポーネントを再設計するよりもはるかに簡単な設計タスクです。モノリシック半導体パッケージで発生する新しい検証コストを発生させることなく、システムの一部を再設計することも可能です。このチップレット再利用方法は「異種再利用」と呼ばれます。

チップレット再利用の別のシナリオは、複数の同一のチップレットを同じシステムに統合することです。この方法はスケーラブルなシステムに理想的であり、効率を大幅に向上させると同時にコストを削減します。これは均質再利用方法と呼ばれ、主な利点は、さまざまな性能および電力要件を満たすためにアーキテクチャ内のチップレットの数を増やすだけで済むことです。

チップレットパッケージング技術

チップレットベースの製品を作るには、設計スキル、ダイ、ダイ間の接続、および生産戦略が必要です。チップレットの適用において、チップレットパッケージング技術の性能、価格、成熟度が大きな影響を与えます。接続媒体と方法の違いにより、チップレットの相互接続に使用されるパッケージング技術は次の3つのグループに分類することができます:

-

基板パッケージング

-

シリコンインターポーザパッケージング

-

再配布層(RDL)パッケージング

-

組み込みマルチダイインターコネクトブリッジ(EMIB)

基板ベースのパッケージング

基板ベースのパッケージングでは、一般的な基板の選択肢として有機材料が使用されます。これらは容易に入手可能です。従来のPCBと同様に、配線接続は半導体製造で使用される他のプロセスとは独立してエッチングプロセスを通じて行われます。これは2D異種統合の最も初期の形態として最もよく知られています。

フリップチップ設計または積層を通じて、複数のダイを高密度で基板に簡単に接合することができます。さらに、この技術はチップ製造プロセスに依存しないため、関連する材料および製造コストは最小限です。この技術を使用する主な欠点は、I/Oピンの密度が低く、これらのパッケージの相互接続の帯域幅に制限があることです。

シリコンインターポーザパッケージング

この技術は2.5Dおよび3Dパッケージング技術にまたがり、チップはインターポーザー上で横方向に(2.5D)または垂直方向に(3D)積み重ねられて構築されます。ダイ間の相互接続と通信を実装するために、シリコンインターポーザー層が基板とダイの間に配置されます。インターポーザーは、チップレット間の電気接続のための基板を提供する、基本的にはミニチュアプリント回路基板のようなものです。相互接続ファブリックは、金属接点(マイクロバンプと呼ばれる)とパッケージ内部を走るスルーシリコンビア(TSV)から構築されます。これらは、ダイをインターポーザーに接続し、インターポーザーコネクタをBGAランドパターンを持つパッケージ基板に接続するために使用されます。

これらの製品は、マイクロバンプとTSV間のトレース長とピッチが小さいことにより、高いI/O密度、低い消費電力、および低い伝送遅延を実現しています。この技術の唯一の顕著な欠点は、製造コストの増加です。

RDLパッケージング

再配布層(RDL)パッケージング技術は基板を使用せず、代わりにウェハーの上面に直接誘電体と金属を堆積させることを含みます。この技術は「ファンアウト」技術とも呼ばれます。ワイヤーデザインを運ぶために、各チップレット上のI/Oポートがデバイスの周りに形成されるように再配布層が構築されます。RDLは回路の長さを短縮することで、より大きな信号整合性(低損失および歪み)を提供します。

組み込みマルチダイ相互接続ブリッジ

EMIBは、ダイ間の相互接続のための基板として有機材料に埋め込まれた薄いシリコンウェハーセクションを使用する技術です。高度な製品の高コストの問題は、異なるチップレットを持つブリッジパッケージングを使用することで対処できます。このハイブリッドパッケージング技術は、基板ベースおよびインターポーザーベースのパッケージングの組み合わせです。通常75マイクロン未満の薄いシリコン層が基板にコーティングされ、ダイ間の接続を形成するために使用され、これらの層は有機基板層に埋め込まれます。

このコンセプトは、HDI PCBで使用されるELICでのアイデアと同じで、各層相互接続ファブリックが複数のダイを絶縁(有機)基板の内部層に接続します。パッケージのEMIB部分は、チップレット間の高帯域幅接続を提供するシリコンブリッジです。

結論

チップレットは、単一のパッケージ内で高い計算コンポーネントと多様な機能性が必要なアプリケーションを革命的に変え続けると期待されています。これらの製品は現在、5G、IoT、自動車、エッジコンピューティング、医療画像、エッジコンピューティング、AI、モバイルデバイスなどの先進技術をターゲットにしています。

今日、Intel、Marvell、AMDなどの主要半導体メーカーはチップレット技術に進出しており、より多くの企業がこのオプションを探求することが期待されます。チップレットIPの市場が他の多くのコンポーネントのように発展するにつれて、より多くのファブレス半導体企業が、個別のコンポーネントでシステムを構築するのではなく、カスタム半導体のアプローチを取るかもしれません。

Intel、AMD、TSMCがチップレットの相互接続に関する共通の標準に合意した今、他の企業によるこれらの設計のさらなる普及を見ることになるでしょうか?このようなコンポーネントの市場が発展することを期待できます。これは、大手半導体メーカーを超えてパッケージングレベルでのさらなるイノベーションを促進するでしょう。

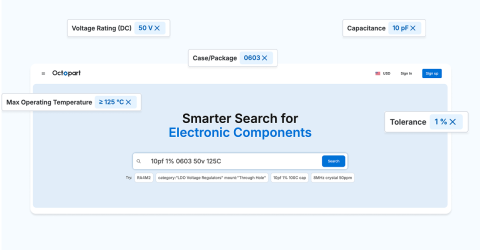

高度なパッケージングを備えたチップレットベースのコンポーネントが市場に出るにつれて、システム設計者はOctopartの高度な検索およびフィルタリング機能を使用して、高度な設計に必要なすべての高度なコンポーネントを見つけることができます。Octopartの電子部品検索エンジンを使用すると、最新のディストリビューター価格データ、部品在庫、部品仕様にアクセスでき、それらはすべてユーザーフレンドリーなインターフェースで自由にアクセス可能です。統合回路のページをご覧ください必要なコンポーネントを見つけてください。

最新の記事を読むために、私たちのニュースレターにサインアップしてください。