Was ist HDI-Design und wie werden HDI-Leiterplatten hergestellt?

Während sich die Welt der Technologie ständig weiterentwickelt, steigt gleichzeitig auch die Notwendigkeit, mehr Funktionen in kleinere Pakete zu packen. Leiterplatten, die mit Techniken für hohe Packungsdichte (High-Density Interconnect, kurz HDI) entwickelt wurden, sind in der Regel kleiner, da mehr Komponenten auf kleinerem Raum untergebracht sind. Auf einer HDI-Leiterplatte werden Blind-, Buried- und Microvias sowie Vias in Pads und sehr dünne Leiterbahnen verwendet, um mehr Komponenten auf einer kleineren Fläche befestigen zu können.

Wir zeigen Ihnen hier in unserem HDI-Design-Guide die wichtigsten Grundlagen für HDI-Design. Außerdem zeigen wir, wie Altium Designer® Ihnen bei der Erstellung eines leistungsstarken HDI-Leiterplattendesigns helfen kann.

Die Entwicklung und Herstellung von gedruckten Schaltungen mit hoher Packungsdichte (HDI) nahm ihren Anfang im Jahr 1980, als Forscher nach Möglichkeiten zur Verringerung der Via-Größe in Leiterplatten suchten. Die ersten Aufbau- oder sequenziell gedruckten Leiterplatten erschienen im Jahr 1984. Seitdem suchen Designer und Komponentenhersteller nach immer besseren Möglichkeiten, mehr Funktionen auf einen einzigen Chip und auf eine einzige Leiterplatte zu packen. Heutzutage sind HDI-Platinendesign und -herstellung in den Normen IPC-2315, IPC-2226, IPC-4104 und IPC-6016 festgelegt.

Bei der Planung eines HDI-Leiterplattendesigns gibt es einige Herausforderungen in Bezug auf Design und Herstellung. Hier folgt eine kurze Liste der Herausforderungen, auf die Sie beim Entwurf einer HDI-Leiterplatte stoßen könnten:

- Begrenzter Arbeitsbereich auf der Leiterplatte

- Kleinere Komponenten und geringere Abstände

- Größere Anzahl von Komponenten auf beiden Seiten des PCB-Lagenaufbaus

- Längere Leiterbahnrouten und dadurch längere Signallaufzeiten

- Mehr Leiterbahnrouten erforderlich, um die Leiterplatte abzuschließen.

Mit den richtigen Layout- und Routing-Tools, die auf einem regelbasierten Design-Engine aufbauen, können Sie die normalen Regeln des Leiterplattendesigns brechen und leistungsstarke PCBs mit sehr hoher Packungsdichte anfertigen. Die Arbeit mit hochdichtem PCB-Routing und Komponenten mit dünnen Leiterbahnbreiten ist einfach, wenn Sie eine fortschrittliche PCB-Designsoftware verwenden, die speziell für HDI-Leiterplatten entwickelt wurde. Erstellen Sie Ihr neues HDI-Leiterplattendesign und planen Sie den HDI-Herstellungsprozess mit den erstklassigen Designfunktionen von Altium Designer.

Was ist beim Design und der Herstellung von HDI-Leiterplatten anders?

Der HDI-Herstellungsprozess unterscheidet sich von der traditionellen Leiterplattenherstellung in einigen einfachen, aber wichtigen Punkten. Ein wichtiger Aspekt ist, dass Beschränkungen des Herstellers die Designmöglichkeiten und die Art und Weise, wie die Leiterplatte geroutet werden kann, begrenzen. Die Verwendung dünnerer Leiterbahnen, kleinerer Vias, mehr Lagen und kleinerer Komponenten kann in Ihrer Designsoftware zwar noch berücksichtigt werden, aber um die Anforderungen an das Design for Manufacturing (DFM, zu Dt. „Design für die Herstellung“) zu erfüllen, müssen Sie die Vorteile der Automatisierung in Ihrer Designsoftware nutzen. Die genauen DFM-Anforderungen hängen vom Herstellungsprozess und von den Materialien ab, die zur Herstellung der Leiterplatte verwendet werden. DFM-Anforderungen werden ebenfalls wichtig, wenn die Anforderungen an die Zuverlässigkeit berücksichtigt werden müssen.

Materialauswahl für das HDI-Design

Die Materialauswahl muss die folgenden Fragen beantworten:

- Ist die Chemie des Dielektrikums mit der Chemie des Kernsubstrats kompatibel?

- Weist das Dielektrikum eine akzeptable Haftung für die Verkupferung auf? (Viele Erstausrüster [OEMs] wollen > 1,08 kgm/cm [6 lb./in.] pro 35,6 µm [1 oz.] Kupfer).

- Bietet das Dielektrikum ausreichende und zuverlässige dielektrische Abstände zwischen den Metallschichten?

- Erfüllt es die thermischen Anforderungen?

- Bietet das Dielektrikum eine wünschenswerte „hohe“ Glasübergangstemperatur für das Drahtbonding und die Nacharbeit?

- Übersteht es thermischen Schock mit mehreren SBU-Schichten (z. B. Lötschwimmer, beschleunigte Thermalzyklen, mehrere Rückflüsse)?

- Hat es beschichtete und zuverlässige Microvias?

Dielektrische Materialien für HDI-Substrate

Es gibt neun verschiedene allgemeine dielektrische Materialien, die in HDI-Substraten verwendet werden. IPC-Slash-Sheets wie IPC-4101B und IPC-4104A umfassen viele davon, aber viele andere sind noch nicht durch IPC-Normen spezifiziert. Die Materialien sind:

- Lichtempfindliche flüssige Dielektrika

- Lichtempfindliche Trockenfoliendielektrika

- Flexibler Polyimidfilm

- Thermisch gehärtete Trockenfilme

- Thermisch gehärtetes flüssiges Dielektrikum

- Harzbeschichtete Kupferfolie (RCC), doppellagig und verstärkt

- Konventionelle FR-4-Kerne und Prepregs

- Neue laserbohrbare (LD) „Spreizglas“-Prepregs

- Thermoplastische Kunststoffe

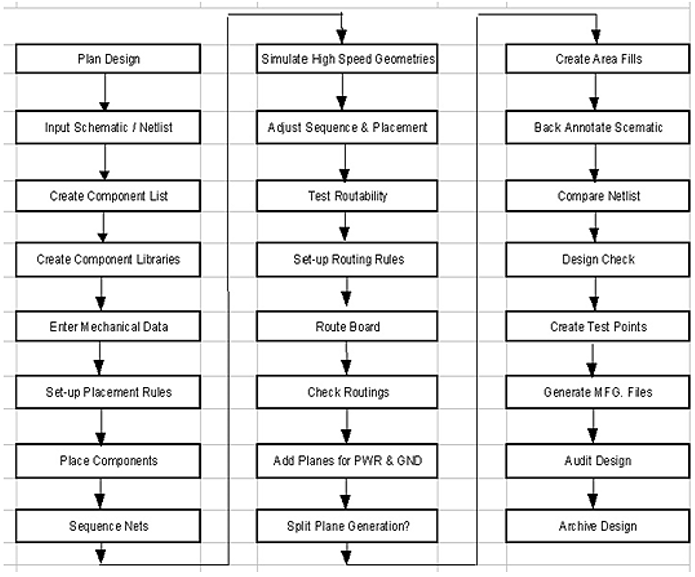

HDI-Design-Prozess

Der Prozess des HDI-Leiterplattendesigns wird im Folgenden dargestellt. Die Effizienz des HDI-Routings hängt dabei von verschiedenen Dingen ab, u.a. vom Lagenaufbau, der Via-Architektur, der Platzierung der Bauteile, dem BGA-Fanout und den Designregeln. Die wichtigsten Aspekte bei der Planung eines HDI-Layouts sind die Leiterbahnbreite, die Via-Größe und die Platzierung/das Escape-Routing von BGA-Komponenten.

Allgemeine Übersicht über das HDI-Leiterplattendesign und den Layout-Prozess.

Erkundigen Sie sich immer bei Ihrem Leiterplattenhersteller nach dessen Methoden für die Herstellung von HDI-Leiterplatten. Es ist wichtig, dass Sie die Grenzen der Herstellungsmethoden kennen, da diese die Komponentengröße beeinflussen, die Sie in Ihrem Layout unterbringen können. Der Abstand bei BGA-Komponenten bestimmt die Via-Größe, die wiederum den für die Herstellung der Leiterplatte erforderlichen HDI-Herstellungsprozess festlegt. Ein zentrales Merkmal Ihrer HDI-Leiterplatte sind die Microvias, die für das Routing zwischen den Lagen präzise gestaltet sein müssen.

Best Practices für das Design von HDI-Leiterplatten

Der typische Herstellungsprozess für Leiterplatten umfasst an sich schon eine Reihe von verschiedenen Schritten. Bei der Herstellung von HDI-Leiterplatten sind jedoch einige weitere besondere Schritte notwendig, die möglicherweise bei anderen Leiterplatten so nicht relevant sind oder vorkommen. Der HDI-Platinendesignprozess beginnt wie viele andere Prozesse:

- Bestimmen Sie die Lagenanzahl, die zum Routing aller Signale erforderlich ist, entweder durch die Verwendung des größten BGA-Bauteils auf der Leiterplatte oder mithilfe der Anzahl an Schnittstellen + Richtungen vom größten IC auf der Platte.

- Wenden Sie sich an Ihr Fertigungsunternehmen, um Materialien auszuwählen und dielektrische Daten für die Erstellung Ihres Leiterplattenaufbaus zu erhalten.

- Bestimmen Sie auf der Grundlage der Lagenzahl und -dicke die Art der Vias, mit der die Signale durch die inneren Lagen geleitet werden sollen.

- Führen Sie bei Bedarf eine Zuverlässigkeitsbewertung durch, um sicherzustellen, dass die Werkstoffe die Verbindungen während der Montage und des Betriebs nicht durch Überbelastung brechen lassen.

- Legen Sie basierend auf den Fähigkeiten des Herstellers und den Zuverlässigkeitsanforderungen (für Teardrops, Leiterbahnbreiten, Abstände usw.) Designregeln fest, um eine zuverlässige Herstellung und Bestückung zu gewährleisten.

Die Erstellung von Lagenaufbauten und die Festlegung von Designregeln sind kritische Punkte, da sie bestimmen, ob sich die Leiterplatte planmäßig routen lässt und ob das Endprodukt auch wirklich zuverlässig sein wird. Nach Abschluss dieser Schritte kann der Designer seine DFM-Anforderungen und Zuverlässigkeitsanforderungen als Designregeln in der ECAD-Software implementieren. Es ist wichtig, diese Arbeiten bereits am Anfang zu erledigen, denn sie tragen dazu bei, dass das Design zuverlässig und herstellbar ist und planmäßig geroutet werden kann.

Gestalten Sie Ihre Funktionsgröße so, dass sie die HDI-DFM-Anforderungen erfüllt.

In Bezug auf die Abstände in einer HDI-Leiterplatte sind die DFM-Anforderungen relativ streng. Sie können aber die Designregeln in Ihrer Leiterplattendesignsoftware nutzen, um sie zu berücksichtigen. Zu den wichtigsten DFM-Anforderungen, die vor dem Layout und Routing erfasst werden müssen, gehören:

- Grenzwerte für Leiterbahnbreite und -abstände

- Grenzwerte für Restringgröße und Aspect Ratio, insbesondere für Designs mit hoher Zuverlässigkeit

- Materialsystem, das in der Leiterplatte verwendet wird, um eine kontrollierte Impedanz im erforderlichen Aufbau zu gewährleisten

- Impedanzprofile für den gewünschten Aufbau oder die Lagenpaare (falls verfügbar)

Ihre Designtools sind enorm wichtig, um Ihre HDI-Leiterplatte gemäß diesen DFM-Anforderungen zu entwerfen. Das Routing von impedanzkontrollierten Leiterbahnen auf Ihrer HDI-Leiterplatte ist mit den richtigen Designtools relativ einfach. Erstellen Sie einfach ein Impedanzprofil und definieren Sie Ihre gewünschte Leiterbahnbreite unter Berücksichtigung der DFM-Richtlinien Ihres Herstellers. Die Online-DRC-Engine in Ihrer Routing-Software überprüft Ihr Routing, während Sie Ihr HDI-Layout erstellen. Vergewissern Sie sich, dass Sie vollständige Spezifikationsangaben für den Prozess Ihres Herstellers erhalten, damit Sie alle relevanten HDI-DFM-Regeln berücksichtigen können.

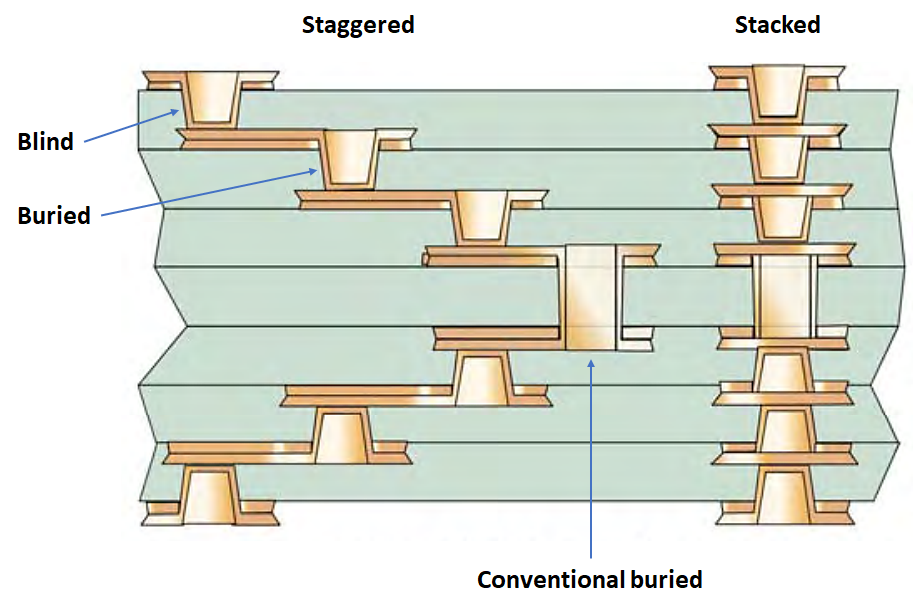

Arten von Vias beim HDI-PCB-Routing

Die folgende Abbildung zeigt die typischen Vias, die beim Layout und Routing von HDI-Leiterplatten verwendet werden. Diese Vias weisen eine niedrige Aspect Ratio von (idealerweise) weniger als 1 auf, obwohl einige Hersteller Aspect Ratios von bis zu 2 als zuverlässig bezeichnen, auch für gestapelte Microvias. In der Mitte des Leiterplattenaufbaus befindet sich ein konventionelles Buried Via, um eine Verbindung durch die dickere Kernschicht herzustellen; dieses Buried Via in der inneren Schicht kann eine höhere Aspect Ratio aufweisen, da es mechanisch gebohrt wird. Sobald die Anzahl der Lagen und die dielektrischen Dicken bestimmt sind, kann der Designer die Vias unter Einhaltung der oben genannten Grenzwerte für die Aspect Ratio entwerfen. Die Einhaltung dieser Grenzwerte für die Aspect Ratio von Microvias ist ein wichtiger Faktor für die Zuverlässigkeit, insbesondere wenn diese Leiterplatten einen Reflow-Prozess durchlaufen oder in einer Umgebung mit wiederholten thermischen/mechanischen Stößen und Zyklen eingesetzt werden.

Sequenzieller Aufbau

Das sequenzielle Laminierverfahren wird überwiegend für die schichtweise Konstruktion eines HDI-Lagenaufbaus verwendet. Im Allgemeinen kann diese Technik für jede mehrlagige Leiterplatte eingesetzt werden, ist aber insbesondere für HDI-Leiterplatten wichtig. Das liegt daran, dass die hochdichten und sehr dünnen Dielektrika in einzelnen Schichten um einen dicken Kern herum gebildet werden, so dass die Laminierung in mehreren Schritten erfolgt, um den Aufbau zu konstruieren. Der sequenzielle Laminierungsprozess umfasst die folgenden Schritte:

- Auftragen und Belichtung von Fotolack: Damit werden die zu ätzenden Bereiche definiert, die auf dem Laminat ein Leiterbahnmuster hinterlassen werden.

- Ätzen und Reinigen: Der derzeitige Industriestandard für Ätzmittel ist eine Eisenchloridlösung. Nach dem Ätzen können die Reste des Fotolacks zurückgewonnen werden, und das entstandene Leitermuster wird gereinigt.

- Ausbilden und Bohren von Vias: Vias müssen mit mechanischen oder Laserbohrverfahren ausgebildet werden. Für eine hohe Via-Dichte können die Via-Öffnungen chemisch entfernt werden.

- Via-Metallisierung: Sobald die Vias definiert sind, werden sie metallisiert, um eine durchgehende leitende Verbindung zu bilden.

- Aufbau: Die Schichten werden in mehreren Laminierungszyklen aufgebaut, um den Aufbau vor der Bearbeitung der Außenschicht abzuschließen.

Ein Ablaufdiagramm für den Aufbauprozess finden Sie im Abschnitt „Metallisierung“ weiter unten.

Ausbilden von Vias in HDI-Leiterplatten

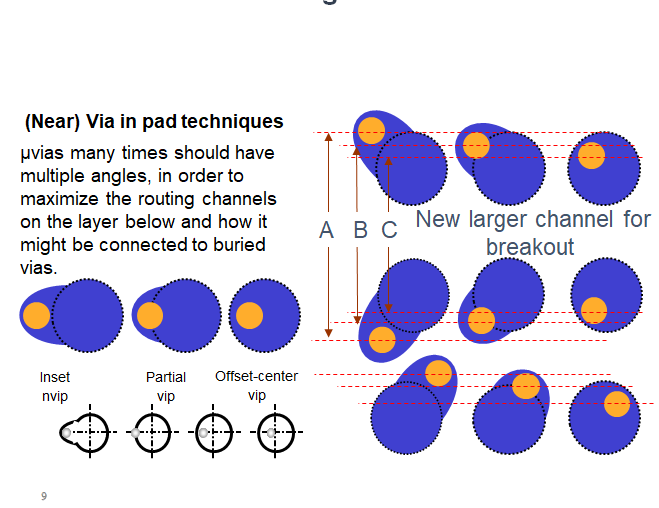

HDI-Leiterplatten erfordern Verbindungen, die in der Regel den unteren Grenzwert der Via-Größe erreichen, die in einer Leiterplatte mit mechanischen Bohrungen platziert werden kann. Sobald die Via-Löcher kleiner als 6 mils sind, ist ein alternatives Ausbildungsverfahren erforderlich, um Microvias zwischen den Schichten zu platzieren. Da gefüllte und verkupferte Microvias ein Standardmerkmal von HDI-Leiterplatten sind, können sie in einem Via-in-Pad-Designansatz verwendet werden, um die Dichte zu erhöhen. Via-in-Pads sind eine einfache Möglichkeit, um mehr Komponenten in ein Design zu integrieren, da sie eine direkte Verbindung von einem Bauteilanschluss zu einer internen Schicht herstellen.

Wenn Bedenken hinsichtlich der Zuverlässigkeit von Microvias bestehen, kann auch eine Near-Pad-Technik angewandt werden, bei der ein sehr kleiner Leiterbahnabschnitt von einem Pad geführt wird und das Microvia berührt. So wird die Verbindung zu einer internen Schicht abgeschlossen und bietet einen größeren Breakout-Kanal, falls die Bohrung aufgrund von Bohrerwandern von der gewünschten Position abweicht.

Via-in-Pad-Designs für HDI-Leiterplatten

Metallisierung

Während des sequenziellen Laminierungsprozesses durchläuft jede Schicht einer HDI-Leiterplatte einen Prozess zur Metallisierung, Füllung und Beschichtung von Vias. Die entstehenden Vias müssen im Innenkörper hohlraumfrei sein und eine ausreichende Ummantelung des Halses aufweisen, um eine Rissbildung während der Reflow-Zyklen und im Betrieb zu vermeiden. Es gibt vier Metallisierungsverfahren, die bei der HDI-Herstellung verwendet werden:

- Herkömmliches stromloses und galvanisch beschichtetes Kupfer

- Konventioneller leitfähiger Graphit oder andere Polymere

- Voll- und halbadditives stromloses Kupfer

- Leitfähige Pasten oder Tinten

Größere Vias können auch gebohrt werden, aber die Kosten übersteigen letztendlich die Kosten für das Laserbohren und resultieren in einem geringeren Durchsatz, da eine langsamere Bohrgeschwindigkeit erforderlich ist. Die Laserbohrung ist bei weitem der beliebteste Bohrungsprozess für Microvias, jedoch nicht der schnellste. Das chemische Ätzen kleiner Vias ist mit einer geschätzten Rate von 8.000 bis 12.000 Vias pro Sekunde am schnellsten. Dies gilt auch für die Plasma- und Photovia-Bildung.

Beim Laserbohren wird ein hochenergetischer Strahl verwendet, um ein Loch in das PCB-Laminat zu bohren. Die Laser können das dielektrische Material abtragen und anhalten, sobald sie auf den Kupferschaltkreis treffen. Daher sind sie ideal für die Herstellung von Blind-Vias mit Tiefenkontrolle. Die Wellenlängen für Laserenergie bewegen sich im Infrarot- und Ultraviolettbereich. Der Laserpunkt ist etwa 20 Mikrometer groß.

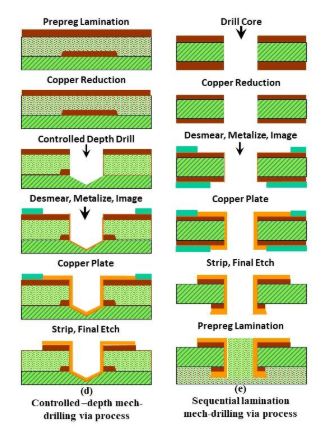

Wenn die Vias in der Leiterplatte breit genug für die Bohrung sind, kann ein kontrollierter Bohrschritt verwendet werden, um die Vias zu platzieren. Dies erfordert einen sequenziellen Laminierungsschritt, um zwei Schichten der Leiterplatte miteinander zu verbinden, gefolgt von Bohren und Beschichten, um die Via-Öffnung zu definieren. Anschließend folgt die Verbindung zur inneren Schicht und die Anschlussfläche auf der oberen Schicht. Diese Vias können auch vor dem nächsten sequenziellen Laminierungsschritt gefüllt werden (wenn sie sich in den inneren Schichten befinden). Wenn sie sich auf den äußeren Schichten befinden, können sie auch ungefüllt bleiben. Das Bohren und der sequenzielle Prozess insgesamt werden nachfolgend gezeigt.

Microvia-Bohr- und Metallisierungsprozesse in einem HDI-Herstellungsprozess

Die Einbindung Ihrer Leiterplatte in den HDI-Fertigungsprozess

HDI-Leiterplattenprozesse sind fortschrittlicher als herkömmliche Verarbeitungsschritte für starre Leiterplatten. Dennoch verwenden sie dieselben Herstellungsdaten, die man für eine typische starre Leiterplatte verwenden würde. Sobald Sie Ihr HDI-Leiterplattenlayout fertiggestellt haben und es eine DFM-Prüfung durchlaufen hat, ist es an der Zeit, die Fertigungsdaten für Ihren Hersteller und den Monteur vorzubereiten. Die einheitliche Designumgebung in Altium Designer nimmt alle Ihre Designdaten und erstellt daraus Gerber/ODB++/IPC-2581-Fertigungsdateien, Bohrtabellen, eine Stückliste und Montagezeichnungen für Ihre neue HDI-Leiterplatte.

Wenn Sie auf der Suche nach der besten Software für das Design, das Layout und die Herstellung von HDI-Leiterplatten sind, dann sind Sie mit dem umfassenden Designtoolset in Altium Designer® gut beraten. Die integrierte Engine für Designregeln und der Lagenaufbau-Manager bieten Ihnen alles, was Sie brauchen, um Ihre HDI-Leiterplatte zu erstellen, Impedanzwerte zu berechnen und die Kupferrauhigkeit in Ihrem PCB-Materialsystem zu berücksichtigen. Wenn Sie Ihren Entwurf fertiggestellt haben und die Dateien für Ihren Hersteller freigeben möchten, können Sie auf der Altium 365™-Plattform ganz einfach zusammenarbeiten und Ihre Projekte teilen.

Wir haben nur an der Oberfläche dessen gekratzt, was mit Altium Designer auf Altium 365 möglich ist. Starten Sie noch heute Ihre kostenlose Testversion von Altium Designer und Altium 365.