Series Termination Resistor Calculation

With transmission lines, some things never seem to be simple. Determining the termination technique and the values of components in a termination network shouldn’t be a difficult task. Most PCB design programs force you to look online for calculators, or you’ll have to run the calculations by hand. Instead, your design software should make it easy to test a range of component values in your termination network.

Some components, traces, differential pairs, and interconnects that route through vias should be impedance matched in order to prevent transmission line effects from arising in high speed or high frequency circuits. While you can get away with small impedance mismatches, some signal drivers will have an impedance that does not match the standard 50 Ohm value typically used with signal traces. One should note that some routing and computer architecture standards (i.e., PCIe Gen 2 and Gen 3) also use a different value for differential pair impedance.

If you have determined that your trace will start to exhibit transmission line effects. In this article, I will show how to use the signal integrity tools in Altium Designer® to determine the correct value for a series resistor.

Which Termination Network Should I Use?

There are several answers to this question as there are several possible networks or terminators. For digital signals, we prefer resistive termination because resistors are broadband components. They can be used to terminate drivers up to very high bandwidths when placed directly on the driver pin of an IC. In contrast, an RF output or an antenna would prefer an LC network because we don't want to have resistive power loss, and the exact placement of the inductor and capacitor (either in series or as a shunt element) depends on how you need to shift the impedance in order to match the resonance frequency.

Regarding resistive termination, the two common methods used are series termination (placed at the driver pin) and parallel termination (placed at the receiver to GND). There are two important things to remember about the effects of series termination:

|

Some reasons to use series termination resistance at the driver include:

- If the line is long enough that you are expecting reflections from an unterminated load, is needed between an unterminated driver and the trace, and the impedance of the signal driver is smaller than your trace impedance

- You want to increase damping seen at the output to help suppress ground bounce, NEXT, SSN, or oscillation on a very short line

- If the signal being produced by the driver needs to be slowed down, which might be used in a fast interface instantiated in an FPGA or when the signals being produced are control signals that do not supply a continuous data stream

In point #1, you can place a series resistor at the output of your driver, but this is very uncommon unless a standard single-ended digital bus (such as SPI) is routed over a very long distance and has low rise time. Point #1 might also be used in the case where specialty RF components are used, and these component do not have on-die termination. Point #2 is more common, especially when the signal is being sourced by a modern processor like an MCU, FPGA, or MPU.

If you have determined that you need series termination, such as based on a critical length calculation, the resistor package should be the smallest possible package you plan to assemble on the board and it is simplest to place it exactly at the driver output pin. To determine series resistance, you either need to know the source impedance already, or you need to have a simulation model for the driver's output buffer (such as IBIS). If you know the source output impedance, then the series termination impedance requirement is:

Here is how to do it in simulation if you know the logic family or you have an IBIS model for the driver output pin.

Determining Series Termination Resistance

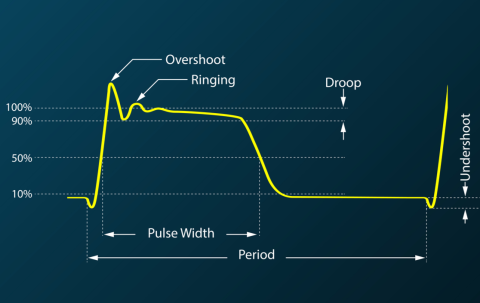

The common method for determining series termination resistance from simulation is to iterate through a range of series resistor values. Once you run the simulator, you’ll see a graph that shows how each component value in the network affects your signal. This allows you to visually determine the best component values to use in your termination network.

- Learn more about how series termination affects voltage levels

The process below applies to both differential signals and single-ended signals that are not part of a standardized interface. Remember, a differential signal can be treated as two separate single-ended signals each with defined odd-mode impedance, so the series termination method shown below applies to a trace in a differential pair as well as long as you count for the slight deviation between odd-mode and single-ended impedance.

Signal Integrity Tool Setup

Once you capture your schematic and layout your board, you’re ready to determine the appropriate termination resistor for your traces. Once you have your board prepared, you can access the signal integrity tool in Altium Designer from the Tools -> Signal Integrity… menu.

Accessing the Signal Integrity tool in Altium Designer

The Signal Integrity tool needs to be set up by either selecting the logic family for the pins on the driver and receiver, or by adding IBIS models to the component. You can also modify the signal stimulus being used as well in the Signal Integrity dialog.

|

Once you’ve opened up the Signal Integrity tool, you should see the Signal Integrity dialog shown in the image below. Here, you’ll need to select which signal nets you want to examine. You can double click the signal nets you want to examine, and these will be added to the table on the right side of the dialog.

Choosing nets and termination networks for your signal integrity simulation

You’ll also see a list of termination networks. In the example that follows, we’re going to examine two single-ended traces (NC1 and NC2). Note that you can change the number of sweeps, as well as the parameters in the termination network. You could also examine one of the differential pairs (i.e., NC3_P and NC3_N) using the same steps presented here.

Single-Ended Results

We’ll look at a series termination network, as well as the “Parallel Res & Cap to GND” termination network. Note that you can choose the maximum and minimum values for your sweep, as well as your VCC voltage.

Here, you can modify the values of the termination resistors in your matching network

Now that you have set up the simulation, click the “Reflection Waveforms…” button to start the simulation. Altium Designer will iterate through the various resistor values and generate a series of graphs. The results for nets NC1 and NC2 are shown in the figure below.

Signal reflection results for various matching networks

From the results above, we can see that the series matching resistor (top two graphs) and the combination of resistors to VCC and ground are actually not the best choices for this board. Both results help reduce ringing somewhat, but we also need to compensate for the slow rise time. Therefore, we should try a different network and repeat the process.

Here, we can go back and choose the “Parallel Res & Cap to GND” network and check to see how this network affects the signals in nets NC1 and NC2. The results for this network are shown below. To see the values for each component in the network, just click on one of the labels in the legend on the right side of the graph. In this board, it turns out that the optimum trace network uses a 56.67 Ohm resistor and an 83.33 pF capacitor (the red signal in the bottom graph).

Signal reflection results for the resistor/capacitor network

Process for a Differential Pair

To examine a differential pair, you can go back to the Signal Integrity dialog and examine each trace in the differential pair. If we consider the series termination formula shown above, we have to remember that the differential impedance is defined in terms of its odd-mode impedance; that is the value used for series resistor termination. Because the characteristic impedance of a trace in a differential pair is always larger than the odd-mode impedance, we can write the following relation:

Based on this deviation, the series resistor value required for a trace in a differential pair will be slightly lower than the value of series resistance determined by the signal integrity tool:

Going Further With Impedance Controlled Routing

Without a doubt, your best bet is to use impedance controlled routing so that you can ensure your traces will have consistent impedance values throughout your board. Ideally, this will help avoid the need to apply a termination network to every single trace in your board, saving you a significant amount of design time.

Determining the right termination network to use in your PCB is much easier when you work with a PCB design package that includes power design and simulation tools. With Altium Designer, you’ll have full control over your layer arrangement and design, and your simulation tools will take data directly from your layout. These tools are directly adaptable to rigid-flex and multi-board systems.

Download a free trial of Altium Designer to see how the powerful signal integrity tools can help you. You’ll have access to the best design features the industry demands in a single program. Talk to an Altium expert today to learn more.